Изобретение относится к области специализированной вычислительной техники, в частности к устройствам для вычисления модулей комплексных чисел.

Известно устройство [А.с. 623202 СССР, 1976] для вычисления модуля комплексного числа, содержащее регистры, сумматоры, коммутаторы, блоки сдвига, элементы НЕ, блок анализа знака.

Недостатком данного устройства является низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности является устройство для вычисления модуля комплексного числа [А.с. 1001085 СССР, 1983], которое содержит регистры, сумматоры и коммутатор, причем входы первого и второго регистров подключены к первому и второму входам устройства, прямые выходы разрядов первого регистра подключены к группе первых входов первого сумматора соответственно, выход коммутатора подключен к первому входу второго сумматора, прямые выходы разрядов первого регистра подключены к первым группам информационных входов первого и второго коммутаторов, вторые группы информационных входов которых подключены к прямым выходам разрядов второго регистра, инверсные выходы которых подключены к группе вторых входов первого сумматора, выход которого подключен к управляющим входам первого и второго коммутаторов, выход второго коммутатора подключен к второму входу второго сумматора, выход которого подключен к выходу устройства.

Недостатком известного устройства является низкая точность результатов.

Задачей настоящего изобретения является повышение точности выходной информации.

Технический результат предлагаемого изобретения - возможность получения более точного результата при неуменьшении разрядности, либо снижение разрядности входных данных (сокращение аппаратурных затрат) при сохранении прежней точности.

Технический результат достигается предложенным устройством для вычисления модуля комплексного числа, которое содержит первый и второй регистры, первый, второй, третий сумматоры и коммутатор, причем входы разрядов первого и второго регистров подключены к информационным входам устройства, прямые выходы разрядов первого регистра подключены к первой группе входов первого сумматора, инверсные выходы разрядов второго регистра подключены к второй группе входов первого сумматора, прямой и инверсный выходы знакового разряда которого подключены к управляющему входу коммутатора через элемент временной задержки сигналов, устройство содержит также третий сумматор, причем первая группа входов второго сумматора подключена к прямым выходам разрядов первого регистра, (n-2) старших разрядов которого подключены к первой группе входов третьего сумматора, вторая группа входов которого подключена к прямым выходам разрядов второго регистра, прямые выходы (n-2) старших разрядов которого подключены к второй группе входов второго сумматора, выходы разрядов второго и третьего сумматоров подключены к первой и второй группе информационных входов коммутатора соответственно, выход которого подключен к выходу устройства (n -двоичная разрядность исходных чисел).

Введение элемента временной задержки сигналов между выходом первого сумматора и управляющим входом коммутатора позволило предотвратить "гонки" в электронных цепях и, таким образом, обеспечить повышение точности (достоверности) выходного результата - модуль комплексных чисел.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют повысить достоверность (информативность) выходных результатов.

Предложенное устройство для вычисления модуля комплексного числа промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

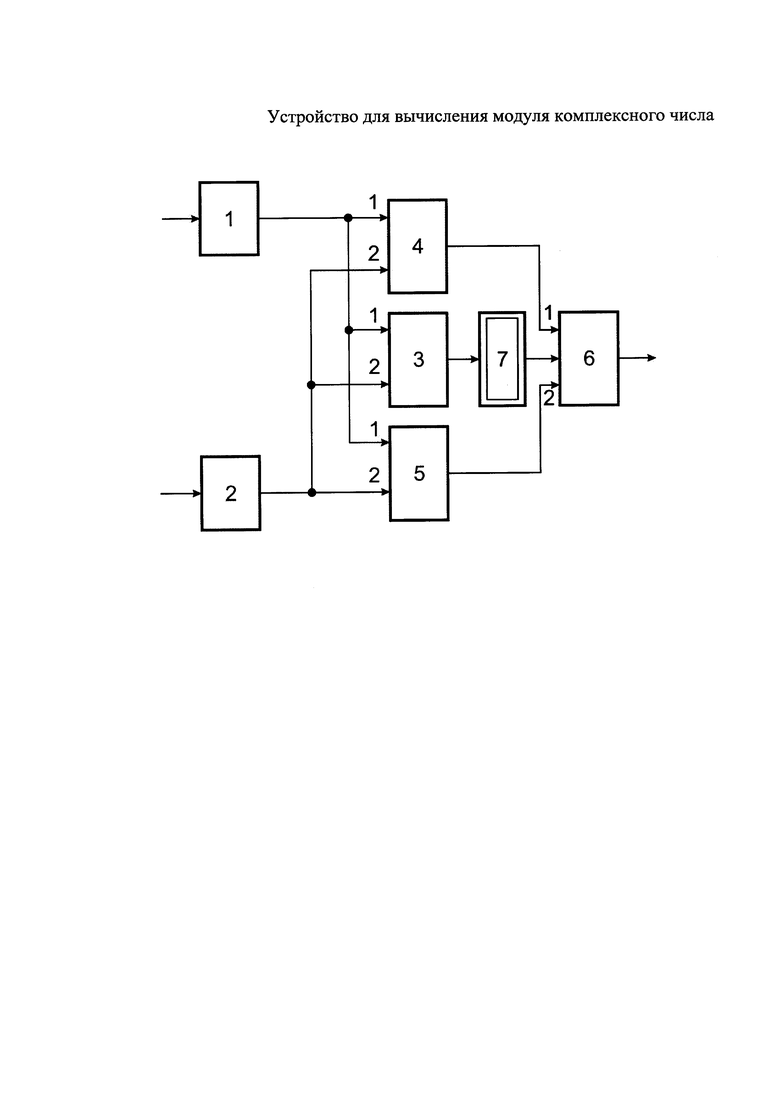

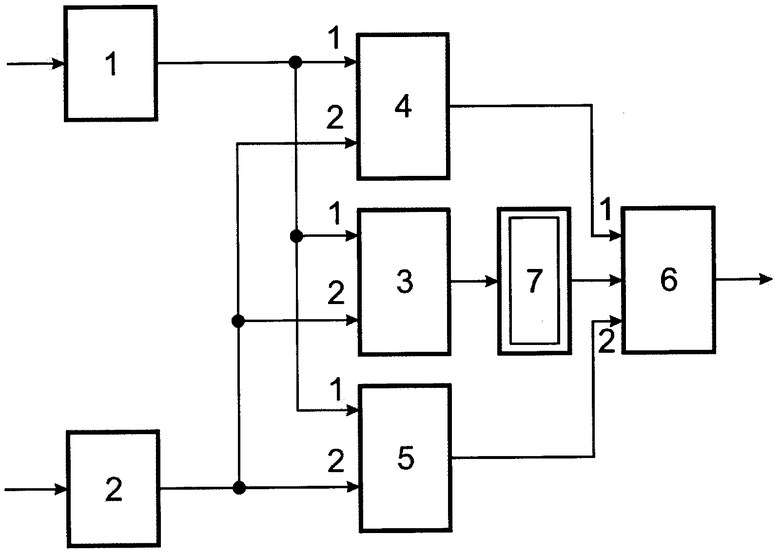

На чертеже представлена структурная схема устройства для вычисления модуля комплексного числа. Заявленное устройство содержит первый 1 и второй 2 регистры, первый 3, второй 4 и третий 5 сумматоры, коммутатор 6 и элемент 7 временной задержки сигналов, включенный между выходом первого сумматора и управляющим входом коммутатора.

Устройство работает следующим образом. В начальный момент времени в первый регистр 1 и второй регистр 2 заносятся соответственно n-разрядные мантиссы прямых кодов действительной и мнимой составляющих комплексного числа.

С выхода первого регистра 1 прямой код действительной составляющей поступает на первые входы первого 3 и второго 4 сумматора, а (n-2) старших разрядов этого кода - на первый вход третьего сумматора 5.

С выхода второго регистра 2 инверсный код мнимой составляющей поступает на второй вход первого сумматора 3, прямой код - на второй вход третьего сумматора 5, а (n-2) старших разрядов этого кода - на второй вход второго сумматора 4.

Сигнал с выхода знакового разряда первого сумматора 3 через элемент 7 временной задержки сигналов поступает на управляющий вход коммутатора 6, на первые информационные входы которого поступает с выхода второго сумматора 4 результат сложения кода действительной составляющей с мнимой, сдвинутой на два разряда в сторону младших разрядов.

На вторые информационные входы коммутатора 6 поступает с выхода третьего сумматора 5 результат сложения кода мнимой составляющей с действительной, сдвинутой на два разряда в сторону младших разрядов. При соответствующем управляющем сигнале, подаваемом на коммутатор, на его выходе вырабатывается результат сложения большей составляющей комплексного числа с меньшей составляющей, сдвинутой на два разряда в сторону младших разрядов.

Коммутатор 6 представляет собой набор из n элементов 2 И-ИЛИ, на входы каждого элемента подаются соответственно сигналы с выходов второго 4 и третьего 5 сумматоров и два управляющих сигнала, являющихся прямым и инверсным сигналами знакового разряда. На выходе коммутатора 6 в зависимости от управляющих сигналов образуется результат, снимаемый с выхода второго 4 или третьего 5 сумматора.

Устройство позволяет производить вычисление модуля комплексных чисел с большей точностью по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Устройство для вычисления модуля комплексного числа | 1980 |

|

SU911516A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА | 2014 |

|

RU2562411C1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1170462A1 |

Изобретение относится к устройствам для вычисления модуля комплексного числа. Технический результат заключается в повышении точности вычисления модуля комплексного числа. Устройство содержит первый и второй регистры, первый, второй, третий сумматоры и коммутатор, причем входы разрядов первого и второго регистров подключены к информационным входам устройства, прямые выходы разрядов первого регистра подключены к первой группе входов первого сумматора, инверсные выходы разрядов второго регистра подключены к второй группе входов первого сумматора, прямой и инверсный выходы знакового разряда которого подключены к управляющему входу коммутатора через элемент временной задержки сигналов. 1 ил.

Устройство для вычисления модуля комплексного числа, содержащее первый и второй регистры, первый, второй, третий сумматоры и коммутатор, причем входы разрядов первого и второго регистров подключены к информационным входам устройства, прямые выходы разрядов первого регистра подключены к первой группе входов первого сумматора, инверсные выходы разрядов второго регистра подключены к второй группе входов первого сумматора, прямой и инверсный выходы знакового разряда которого подключены к управляющему входу коммутатора через элемент временной задержки сигналов, причем первая группа входов второго сумматора подключена к прямым выходам разрядов первого регистра, (n-2) старших разрядов которого подключены к первой группе входов третьего сумматора, вторая группа входов которого подключена к прямым выходам разрядов второго регистра, прямые выходы (n-2) старших разрядов которого подключены к второй группе входов второго сумматора, выходы разрядов второго и третьего сумматоров подключены к первой и второй группе информационных входов коммутатора соответственно, выход которого подключен к выходу устройства, отличающееся тем, что дополнительно содержит элемент временной задержки сигналов, включенный между выходом первого сумматора и управляющим входом коммутатора.

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1635173A1 |

| Устройство для вычисления модуля комплексного числа | 1988 |

|

SU1589272A1 |

| Устройство для вычисления модуля комплексного числа | 1987 |

|

SU1439585A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1295387A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1259259A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1254478A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

Авторы

Даты

2017-05-02—Публикация

2016-02-25—Подача