Изобретение относится к вычислительной технике, в частности к организации управления памятью, и может быть использовано для сопряжения с памятью в вычислительных комплексах.

Цель изобретения - повышение быстродействия устройства за счет обеспечения возможности одновременной работы .двух ЭВМ с памятью.

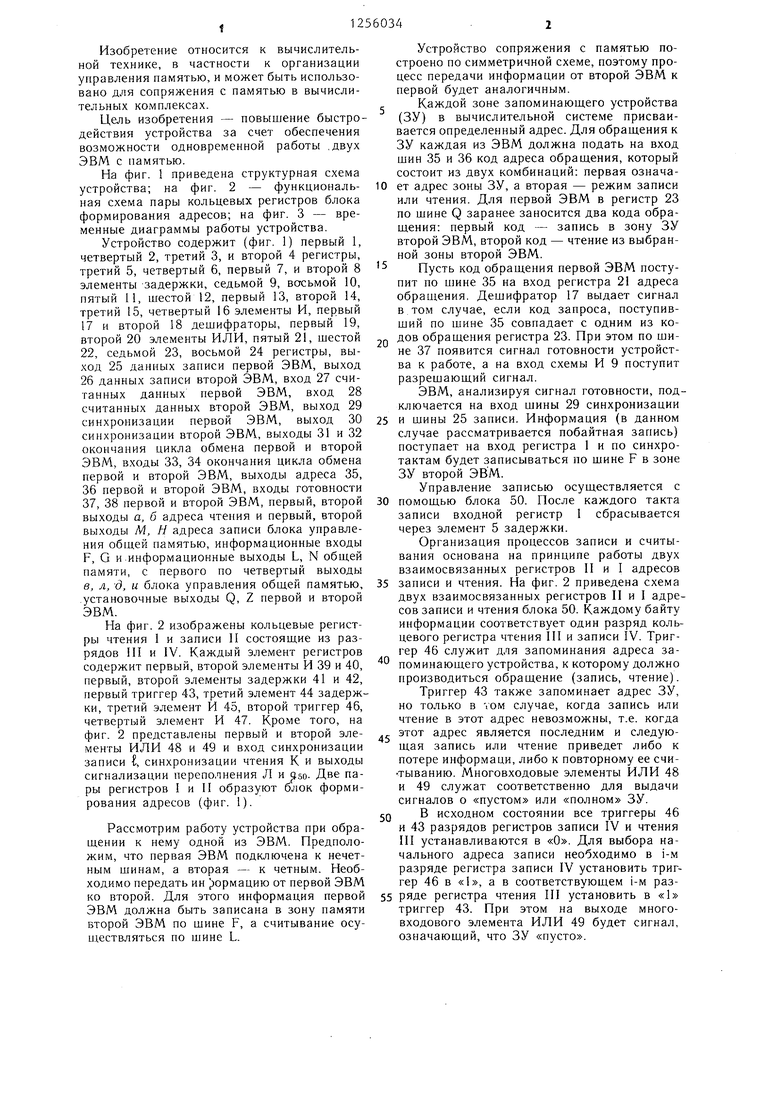

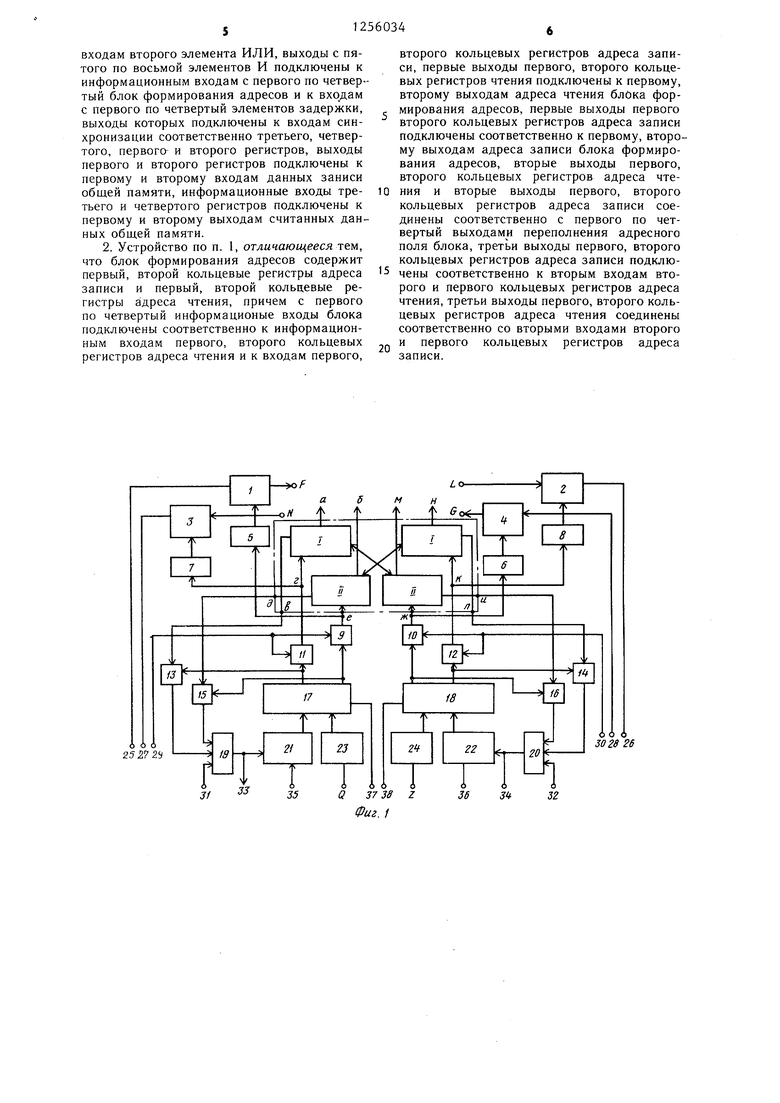

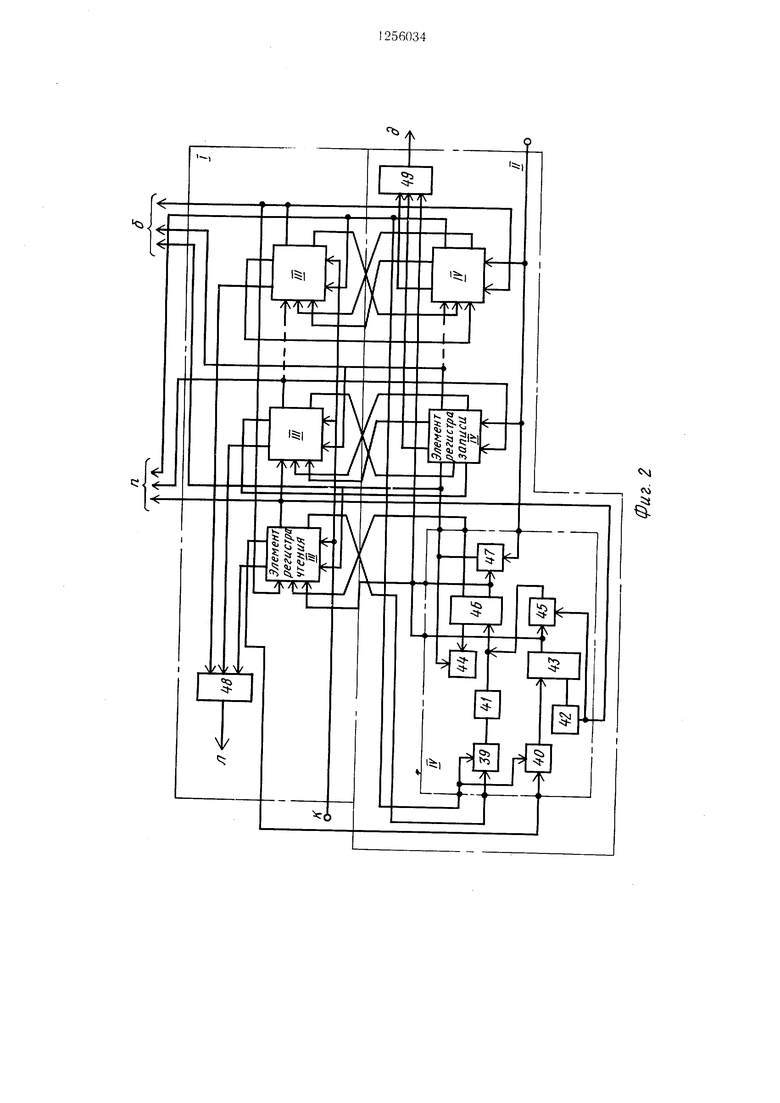

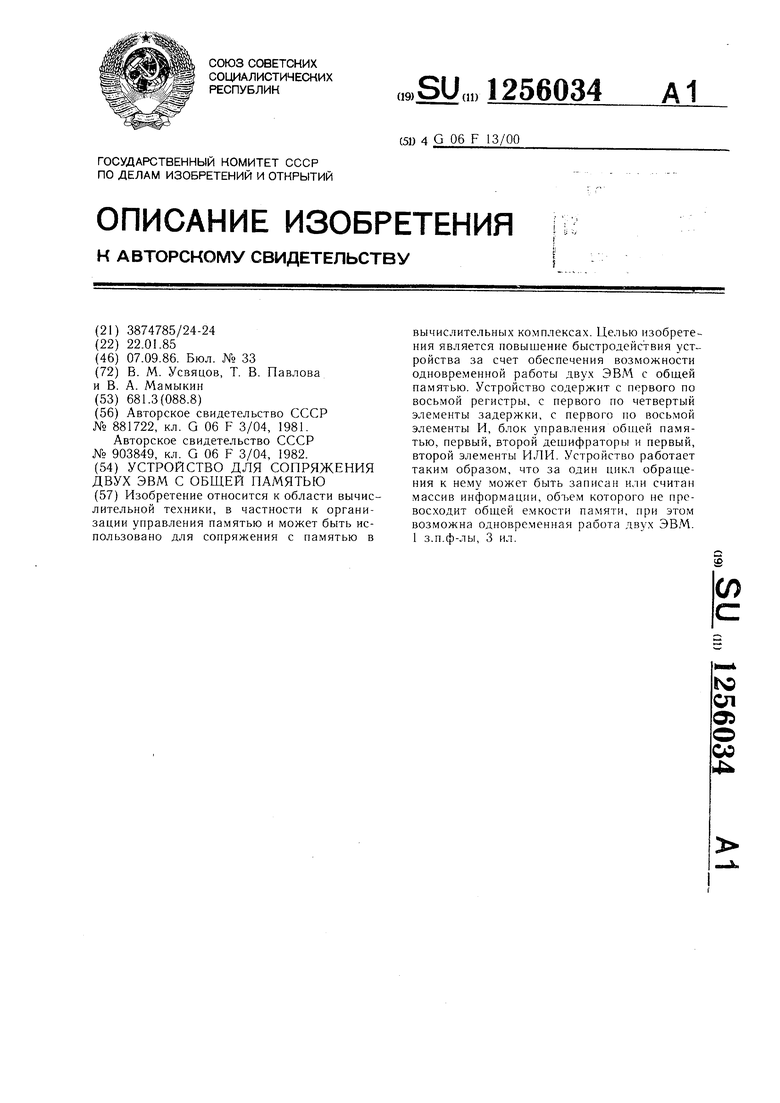

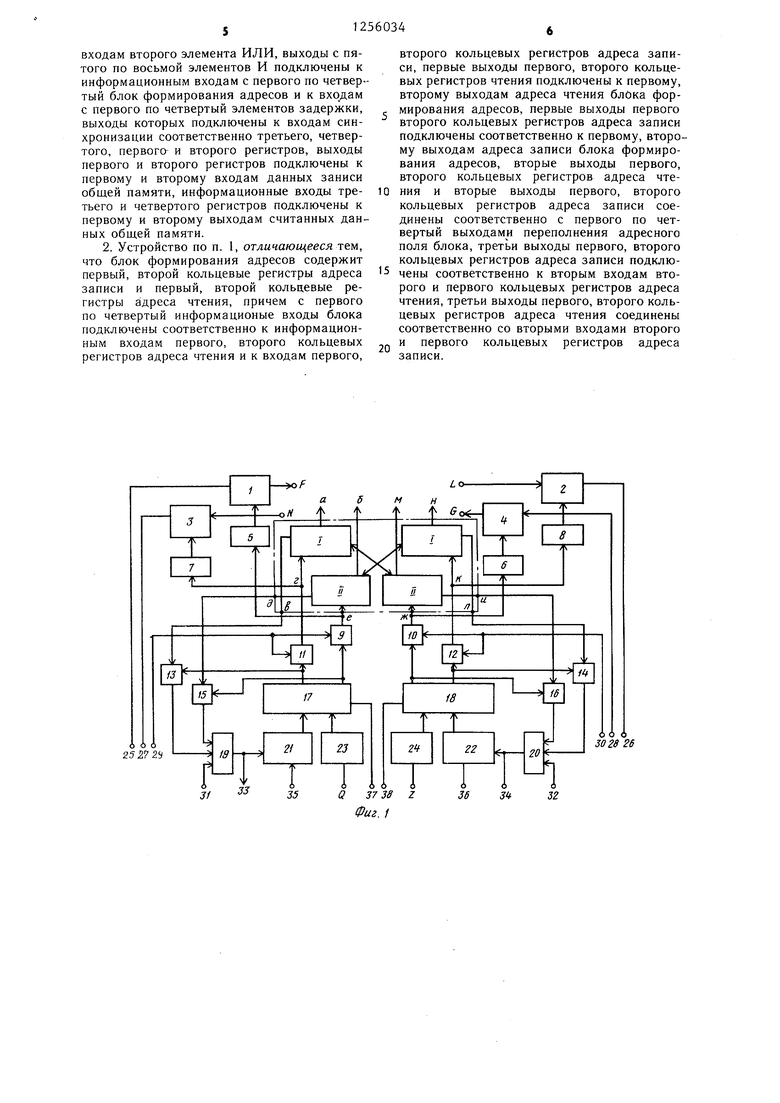

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема пары кольцевых регистров блока формирования адресов; на фиг. 3 - временные диаграммы работы устройства.

Устройство содержит (фиг. 1) первый 1, четвертый 2, третий 3, и второй 4 регистры, третий 5, четвертый 6, первый 7, и второй 8 элементы задержки, седьмой 9, восьмой 10, пятый 11, шестой 12, первый 13, второй 14, третий 15, четвертый 16 элементы И, первый 17 и второй 18 дешифраторы, первый 19, второй 20 элементы ИЛИ, пятый 21, шестой 22, седьмой 23, восьмой 24 регистры, выход 25 данных записи первой ЭВМ, выход 26 данных записи второй ЭВМ, вход 27 считанных данных первой ЭВМ, вход 28 считанных данных второй ЭВМ, выход 29 синхронизации первой ЭВМ, выход 30 синхронизации второй ЭВМ, выходы 31 и 32 окончания цикла обмена первой и второй ЭВМ, входы 33, 34 окончания цикла обмена первой и второй ЭВМ, выходы адреса 35, 36 первой и второй ЭВМ, входы готовности 37, 38 первой и второй ЭВМ, первый, второй выходы а, б адреса чтения и первый, второй выходы М, Н адреса записи блока управления общей памятью, информационные входы F, G и информационные выходы L, N обш,ей памяти, с первого по четвертый выходы в, л, д, и блока управления общей памятью, установочные выходы Q, Z первой и второй ЭВМ.

На фиг. 2 изображены кольцевые регистры чтения 1 и записи II состоящие из разрядов III и IV. Каждый элемент регистров содержит первый, второй элементы И 39 и 40, первый, второй элементы задержки 41 и 42, первый триггер 43, третий элемент 44 задержки, третий элемент И 45, второй триггер 46, четвертый элемент И 47. Кроме того, на фиг. 2 представлены первый и второй элементы ИЛИ 48 и 49 и вход синхронизации записи I, синхронизации чтения К и выходы сигнализации переполнения Л и QSO. Две пары регистров и И образуют блок формирования адресов (фиг. 1).

Рассмотрим работу устройства при обращении к не.му одной из ЭВМ. Предположим, что первая ЭВМ подключена к нечетным шинам, а вторая - к четным. Необходимо передать ин формацию от первой ЭВМ ко второй. Для этого информация первой ЭВМ должна быть записана в зону памяти второй ЭВМ по шине F, а считывание осу- плествляться по шине L.

Устройство сопряжения с памятью построено по симметричной схеме, поэтому процесс передачи информации от второй ЭВМ к первой будет аналогичным. - Каждой зоне запоминающего устройства (ЗУ) в вычислительной системе присваивается определенный адрес. Для обращения к ЗУ каждая из ЭВМ должна подать на вход шин 35 и 36 код адреса обращения, который состоит из двух комбинаций: первая означа0 ет адрес зоны ЗУ, а вторая - режим записи или чтения. Для первой ЭВМ в регистр 23 по шине Q заранее заносится два кода обращения: первый код - запись в зону ЗУ второй ЭВМ, второй код - чтение из выбранной зоны второй ЭВМ.

5 Пусть код обращения первой ЭВМ поступит по шине 35 на вход регистра 21 адреса обращения. Дешифратор 17 выдает сигнал в том случае, если код запроса, поступивший по шине 35 совпадает с одним из ко0 дов обращения регистра 23. При этом по шине 37 появится сигнал готовности устройства к работе, а на вход схемы И 9 поступит разрешающий сигнал.

ЭВМ, анализируя сигнал готовности, подключается на вход щины 29 синхронизации

5 и шины 25 записи. Информация (в данном случае рассматривается побайтная запись) поступает на вход регистра 1 и по синхро- тактам будет записываться по шине F в зоне ЗУ второй ЭВМ.

Управление записью осуществляется с

0 помощью блока 50. После каждого такта записи входной регистр 1 сбрасывается через элемент 5 задержки.

Организация процессов записи и считывания основана на принципе работы двух взаимосвязанных регистров И и I адресов

записи и чтения. На фиг. 2 приведена схема двух взаимосвязанных регистров II и I адресов записи и чтения блока 50. Каждому байту информации соответствует один разряд кольцевого регистра чтения III и записи IV. Триггер 46 служит для запоминания адреса за- поминающего устройства, к которому должно производиться обращение (запись, чтение). Триггер 43 также запоминает адрес ЗУ, но только в VOM случае, когда запись или чтение в этот адрес невозможны, т.е. когда

j этот адрес является последним и следующая запись или чтение приведет либо к потере информаци, либо к повторному ее счи- тыванию. Многовходовые элементы ИЛИ 48 и 49 служат соответственно для выдачи сигналов о «пустом или «полном ЗУ.

Q В исходном состоянии все триггеры 46 и 43 разрядов регистров записи IV и чтения III устанавливаются в «О. Для выбора начального адреса записи необходимо в i-м разряде регистра записи IV установить триггер 46 в «1, а в соответствующем i-м раз5 ряде регистра чтения III установить в «1 триггер 43. При этом на выходе много- входового элемента ИЛИ 49 будет сигнал, означающий, что ЗУ «пусто.

Информация, подлежащая записи, поступает с регистра 1 по шние F одновременно с приходом тактирующих импульсов по шине t. Элемент 47 И i-ro разряда элемента регистра записи разрешит прохождение первого импульса синхросерии по шине б ЗУ. Этот же сигнал через элемент 44 задержки, установит триггер 46 i-ro элемента регистра записи в состояние «О, а через элемент 39 И i-f-1-го элемента регистра записи, в зависимости от состояния триггера 46 i + 1-го разряда элемента регистра чтения, установит в состояние «1 триггер 46 Ж-го элемента регистра записи, кроме того, этот же сигнал установит триггер 46 i-ro разряда элемента регистра чтения в «1. Эта установка произойдет через элемент И 45 а через элемент 42 задержки триггер 43 будет установлен в «О.

Таким образом, при поступлении синхросерии «1 «маркер будет двигаться по кольцевому регистру II до тех пор, пока не прекратятся тактовые импульсы.

Режим окончания обмена может быть инициирован как самой ЭВМ, так и сигналом о заполнении ЗУ. В первом случае ЭВМ выдает сигнал на шину 31 (фиг. 1) и через элемент ИЛИ 19 произойдет сброс регистра 21 и ответный сигнал будет подан в ЭВМ по щине 33.

Сигнал окончания режима обмена может вырабатываться и в случае, если «маркер передается от 1-го разряда в i-й разряд регистра записи. Так как чтения информации из ЗУ не происходило, триггер 46 регистра чтения находится в «Ь, сигнал с i -1-го разряда регистра записи через элемент И 40 установит триггер 43 в «1, и через элемент ИЛИ 49 по шине о будет выдан сигнал о «полном ЗУ.

Процесс чтения второй ЭВМ может быть осуществлен путем передачи соответствующего кода адреса обращения по шине 36. В этом случае дешифратор 18 выдает сигнал о разрешении чтения на элемент И 12 и с помощью регистра 1 будет последовательно считываться вся информация, записанная первой ЭВМ. После каждого такта считывания регистр 2 сбрасывается через элемент 8 задержки. Причем окончание режима обмена может быть инициировано так же, как и в случае режима записи либо самой ЭбМ, либо блоком 50.

Таким образом, за один цикл обращения к устройству может быть последовательно записан массив информации, объем которой не превосходит емкости ЗУ. Организация работы регистров записи и чтения такова, что возможна одновременная работа двух ЭВМ, причем асинхронизация тактирующих сигналов будет отрабатываться обоими регистрами записи и чтения таким образом, что исключается порча информации и повторное ее считывание.

Формула изобретения

1. Устройство для сопряжения двух ЭВМ с общей памятью, содержащее с первого по щестой регистры, первый, второй 5 дешифраторы и первый, второй элементы ИЛИ, причем выходы данных записи первой и второй ЭВМ подключены к информационным входам соответственно первого- и второго регистров, входы считанных данных

0 первой и второй ЭВМ подключены к выходам соответственно третьего и четвертого регистров, выходы первого, второго элементов ИЛИ соединены с входами сброса соответственно пятого и шестого регистров, выходы которых подключены к первым вхо5 дам соответственно первого и второго дешифраторов, отличающееся тем, что, с целью повышения быстродействия устройства за счет обеспечения возможности одновременной работы двух ЭВМ с памятью, в него введены блок формирования адресов, седь мой, восьмой регистры, с первого по восьмой элементы И и с первого по четвертый элементы задержки, причем первый, второй выходы адреса чтения и первый, второй выходы адреса записи блока формирования адресов

5 подключены к одноименным входам общей памяти, с первого по четвертый выходы переполнения адресного поля блока формирования адресов подключены к первым входам соответственно с первого по четвертый элементов И, выходы и входы окончания цикла

0 обмена первой и второй ЭВМ подключены соответственно к первым выхода и входам первого, второго элементов ИЛИ, информационные входы с пятого по восьмой регистров соединены соответственно с выходом адреса первой ЭВМ, с установочными выхо5 дами первой и второй ЭВМ и с выходом адреса второй ЭВМ, выходы седьмого, восьмого регистров подключены соответственно к вторым входам первого, второго дешифраторов, первые выходы которых соединены соответственно с входами готовности первой, второй ЭВМ, второй выход первого дешифратора подключен к второму входу первого элемента И и к первому входу пятого элемента И, второй выход второго дешифратора соединен с вторым входом второго элемента И и с пер5 вым входом шестого элемента И, третий выход первого дешифратора соединен с вторым входом третьего элемента И и с первым входом седьмого элемента И, третий выход второго дешифратора подключен к второму входу четвертого элемента И и к первому входу

0 восьмого элемента И, вторые входы пятого и седьмого элементов И подключены к выходу синхронизации первой ЭБМ, вторые входы шестого и восьмого элементов И подключены к выходу синхронизации второй ЭВМ, выходы первого и третьего элемен5 тоБ И подключены соответственно к второму, третьему входам первого элемента ИЛИ, выходы второго и четвертого элементов И подключены соответственно к второму, третьему

0

входам второго элемента ИЛИ, выходы с пятого по восьмой элементов И подключены к информационным входам с первого по четвертый блок формирования адресов и к с первого по четвертый элементов задержки, выходы которых подключены к входам синхронизации соответственно третьего, четвертого, первого и второго регистров, выходы первого и второго регистров подключены к первому и второму входам данных записи общей памяти, информационные входы третьего и четвертого регистров подключены к первому и второму выходам считанных данных общей памяти.

2. Устройство по п. 1, отличающееся , что блок формирования адресов содержит первый, второй кольцевые регистры адреса записи и первый, второй кольцевые регистры адреса чтения, причем с первого по четвертый информационые входы блока подключены соответственно к информационным входам первого, второго кольцевых регистров адреса чтения и к входам первого.

J/

3SQ 37 38 Z36 3ttзг

Фиг. 1

второго кольцевых регистров адреса записи, первые выходы первого, второго кольцевых регистров чтения подключены к первому, второму выходам адреса чтения блика формирования адресов, первые выходы первого второго кольцевых регистров адреса записи подключены соответственно к первому, второму выходам адреса записи блока формирования адресов, вторые выходы первого, второго кольцевых регистров адреса чтения и вторые выходы первого, второго кольцевых регистров адреса записи соединены соответственно с первого по четвертый выходами переполнения адресного поля блока, третьи выходы первого, второго кольцевых регистров адреса записи подключены соответственно к вторым входам второго и первого кольцевых регистров адреса чтения, третьи выходы первого, второго кольцевых регистров адреса чтения соединены соответственно со вторыми входами второго и первого кольцевых регистров адреса

записи.

с;

NJ

vi

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Изобретение относится к области вычислительной техники, в частности к организации управления памятью и может быть использовано для сопряжения с памятью в вычислительных комплексах. Целью изобретения является повышение быстродействия устройства за счет обеспечения возможности одновременной работы двух ЭВЛ1 с общей памятью. Устройство содержит с первого по восьмой регистры, с первого по четвертый элементы задержки, с первого по восьмой элементы И, блок управления общей памятью, первый, второй дешифраторы и первый, второй элементы ИЛИ. Устройство работает таким образом, что за один цикл обращения к нему может быть записан или считан массив информации, объем которого не превосходит общей емкости памяти, при этом возможна одновременная работа двух ЭВМ. 1 з.п.ф-лы, 3 ил. 1чЭ СП о о CQ

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство сопряжения с памятью | 1979 |

|

SU903849A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-01-22—Подача