(54) УСТРОЙСТВО ДЛЯ ТЕСТОВОГО ДИАГНОСТИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Многоканальный коммутатор | 1985 |

|

SU1260993A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для тестового диагностирования | 1978 |

|

SU792258A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

I

Изобретение относится к вычислитепьной технике и может быть использовано в автоматизированных системах контроля цифровых объектов.

Известно устройство дпя контроля логических блоков, содержащее блок для хранения эгапонных входных наборов, регистр входных наборов, блок элементов i ,

Недостатками известного устройства являются низкая нацежность и ограниченные функциональные возможности.

Наиболее близким к предлагаемому по технической сущности является устройство для тестового диагностирования, содержащее триггер режима, первые элементы И, первый регистр, первый дещифратор, второй дешифратор, первый блок памяти, второй регистр, которое позво ляет реализовать условные и безусловные алгоритмы тестового диагностирования с определением состояния объекта диагноза. При условии тестирования модификация адреса очередных тестовых наборов осуществляется реакцией объекта, причем каждый выход объекта осуществляет модификацию соответствующего разряда адреса 2.

Недостатком этого устройства являются его ограниченные функциональные возможности, обусловленные тем, что устройство не позволяет исключить из процесса формирования адреса следующего входного набора выходы объекта, не10существенные для диагностики, при этом формат адреса входного набора ограничен разрядностью первого блока памяти. Тем самым ограничивается количество выходов диагностируемого объекта, так

15 как каждый из них участвует в модификации одного из разрядов ацреса и накладывается ограничение на класс диагностируемых объектов.

Коггачество контролируемых выходов

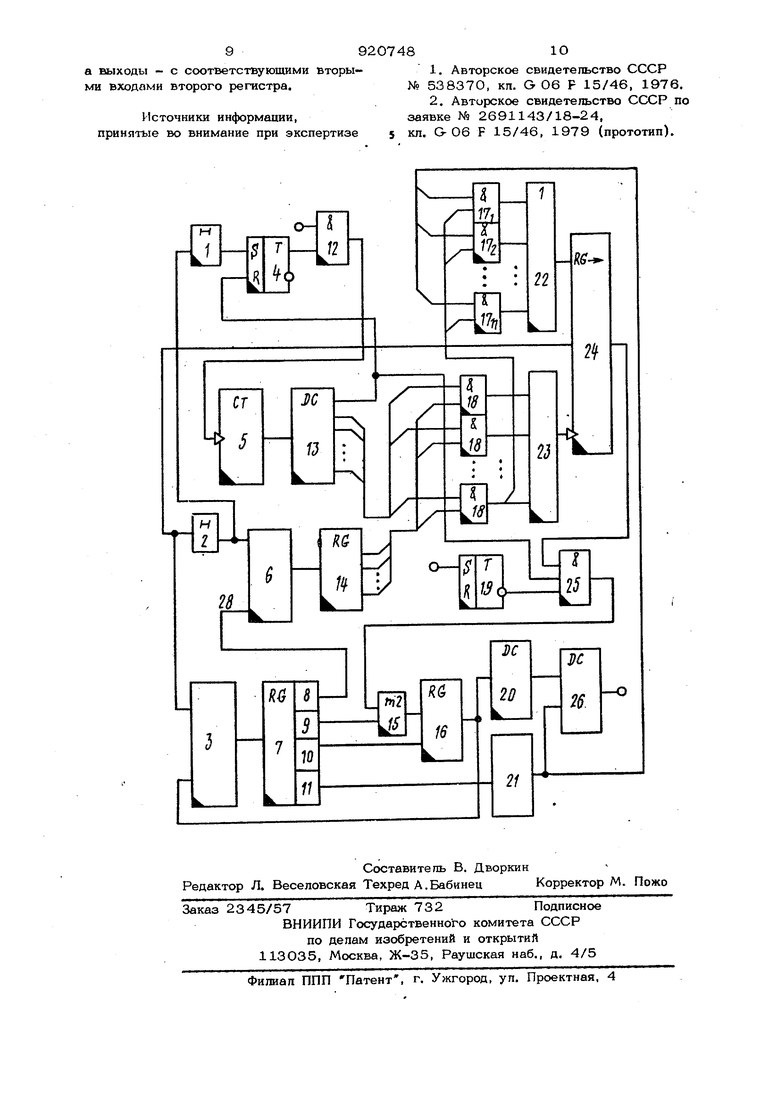

20 диагностируемого объекта можно расширить, если для модификации адреса следующего входного набора использовать лишь те выходы, которые являются су3 9207 ..щественными для предыдущего входного набора . Оцнако при этом оанЫ ременно со считыяанием вкоаного набора необ- яопимо аацавать существенные цля него выхоаы циагностируемого объекг-а и .j .осуществлять их: поаключение к узлу моцифйкацйи ацреса, что в яавестном устройстве невозможно. Ограниченные функциональные возможности известного устройства обусловле-° ны также и тем, что модификация адреса осуществляется на элементах И, которые могут изменить в адресе лищь погическую 1 на логический О. За счет этого вдвое уменьшается количество пере-15 ходов при модификации адреса и усложняется коаирование ацресов. Цель изобретения - расширение функциональных возможностей устройства,. Поставленная цель достигается тем, что в устройство для тестового диагностирования, содержащее первые элементы И, первый регистр, первые выходы которого соединены с входами объекта диагностирования, а второй выход - с первым входом второго регистра, выход которого соединен с первым входом первого блока памяти, второй вход которого соединен с первым входом устройства, а выход - с входом первого регистра вход первого дещифратора соединен с выходом второго регистра, а выход - с первым входом второго дещифратора, выход которого соединен с выходом устройства, вторые входы второго дешифратора соедине- ны с выходами объекта диагностирования, вход триггера режима соединен с вторым входом устройства, введены триггер управления, счетчик, третий дещифратор, сумматоры по модулю два, сдвигающий регистр, второй блок памяти, третий ре- гистр, первый и второй элементы ИШ, первый и второй элементы задержки, второй элемент И и по числу выходов объектас, диагностирования третьи и четвертые элементы И, каждый из которых соединен первым входом с соответствующим первым выходом третьего дешифратора. вторым входом - с соответствующим выкопом третьего регистра, выхоаом-со соответствующим входом второго элемента ИЛИ, соединенного выходом с первым управляющем входом сдвигающего регистра, информационный вход которого соеди-. нен с выходом первого элемента ИЛИ,55 входы которого соединены с выходами соответствующих третьих элементов И, первые входы которых соединены соот48 4 ветственно с выходами одноименных четвертых элементов И, вторые входы с соответствующими выходами объекта диагностирования третий выход первого регистра соединен с первым входом второго блока памяти, соединенного выходом с входом третьего регистра, вторым входом через первый элемент задержки - с первым входом устройства и вторым управняющим входом сдвигающего регист Р элемент задержки первым входом триггера управления, соединенного выходом с первым входом торого элемента И, соединенного вторым входом с третьим входом устройства, выходом через счетчик - с входом третьего дещифратора, соединенного вторым выходом с вторым входом триггера управления и первыми входами первых элементов И, соединенш: 1Х вторыми входами ссоответствующими выходами сдвигающего регистра, третьими входами - с выходом триггера режима, выходами - с первыми входами соответствующих сумматоров по модулю два, вторые входы которых соединены с соответствующими четвертыми выходами первого регистра, а выходы - с соответствующими вторыми входами второго регистра. На чертеже представлена функциональная схема предлагаемого устройства, Устройство содержит второй элемент задержки 1, первый элемент задержки, 2, первый блок памяти 3, триггер управления 4, счетчик 5, второй блок памяти б, первый регистр 7 с полями адреса маски 8, переменной 9 и постоянной 1О части адреса следующего входного набо- ра и полем входного набора 11,. второй элемент И 12, третий дешифратор 13, третий. регистр 14, сумматоры по модулю два 15, второй регистр 16, тре- тий 17 и четвертые 18 элементы И, триггер режима 19, первый дешифратор 20, объект диагностирования 21, первый 22 и второй 23 элементы И.ПИ,сдвирающий регистр 24, первые элементы И 25 и второй дешифратор 26. Элемент задержки 1 предназначен для подачи сигнаш на запуск счетчика 5 ттшь после того, как будет считан код. маски, а на выходах объекта диагностирования сформируется устойчивая реакция на поданный входной набор, а элемент задержки 2 - для подачи сигнала на считывание кода маски лищь после окончани я формирования адреса маски. Блок памяти 3 служит для хранения наборов входных сигналов, предназначенных для

подачи на объект диагностирования 21 Триггер управления 4 управляет элементом И 12, который управляет подачей импульсов с тактового входа устройства на счетчик 5, предназначенный дня управления опросом разрядов кода маски Блок памяти 6 предназначен для хранения и выдачи кода маски, соответствующего входному набору. Регистр 7 предназначен для хранения входного набора, считанного из блока памяти 3. В поле 8 регистра 7 записывается адрес маски, соответствующей входному набору; в поле 9 регистра 7 - переменная часть адреса следующего входного набора; в поле 10 регистра 7 - постоянная част адреса; в поле 11 регистра 7 - набор входных сигналов предназначенный для подачи на объект диагностирования 21. В регистре 14 хранится код маски. Сум маторы по модулю два 15 предназначены для модификации переменной части адреса следующего входного набора сигналами с существенных выходов объекта диагностирования 21. В регистре 16 хра нится адрес следующего входного набора Элементы И 17 предназначены для опроса состояния существенных выходов объекта диагностирования 21, а элементы И 18 - для формирования сигналов опро- са существенных выходов объекта диагностирования по коду м&ски. Триггер режима 19 фиксирует режим работы устройства. Дещифратор 2О формирует сигнал об окончании тестирования. Элемент

ИЛИ 22 предназначен для подачи сигналов с существенных выходов объекта диагностирования 21 на информационный вход сдвигающего регистра 24, а элемент ИЛИ 23 - для подачи сигналов сдв га на динамический вход сдвигающего регистра. Сдвигающий регистр 23 предназначен для запоминания сигналов на существенных выхоцах объекта диагностирования 21. Элементы И 25 управляют выдачей информации из сдвигающего регистра 15. Дещифратор 26 формирует сигнал о результатах тестирования в зависимости от реакции объекта диагностирования 21 после прихода сигнала об окончании тестирования из дещифрато- ра 2О.

Предлагаемое устройство для тестового диагностирования работает в двух режимах: условного и безусловного тестирования.

Устройство работает следующим образом.

Перед началом диагностирования счетчик 5, регистр 7 и сдвигешэщий регистр 24 находятся в исходном, состоянии, в регистр 16 записан адрес первого входного набора. В зависимости от прихода сигнала на управляющий вход триггер режима 19 устанавливается в нулевое (в режиме условного тестирования), или в единичное (в режиме безусловного тестирования) состояние.

В режиме условного тестирования по сигналу на первом входе устройства из блока памяти 3 по адресу, записанному в регистр 7, считывается код. Из поля 11 регистра 7 поступает на объект диагностирования 21. Из поля 8 регистра 7 на блок памяти 6 поступает адрес маски. По сигналу с выхода элемента задержки 2 по этому адресу в регистр 14 считъ вается код маски, задающей выходы объекта диагностирования 21, которые при поданном на него тесте Являются существенными. Сигналами с группы выходов регистра 14 отпираются соответствующие элементы И 18.

, После того, как на выходе объекта диагностирования 21 сформируется устойчивая реакция на поданный тест, по сигналу с выхода элемента задержки 1 триггер управления 4 устанавливается в единицу и отпирает элемент И 12, разрешая заполнение счетчика 5 импульсами с тактового входа. При этом на первых выходах дешифратор 13 поочередно вырабатывает сигналы, которыми поочередно опрашиваются элементы И 18. Единичные сигналы будут сформированы лишь теми элементами И 18, которые соответствуют выделенным маской существенным выходам объекта диагностирования 21. Каждый из таких сигналов отпирает соответствующий элемент И 17, через который сигнал.с соответствующего существенного выхода объекта 21 записывается в старший разряд сдвигающего регистра 24. Сигналом с того же элемента И 18 в регистре 24 осуществляется сдвиг информации в сторону младших разрядов, причем в случае несущественного выхода сдвиг и запись информации в регистре 24 не происходят.

Таким образом, осуществляется поочередный опрос всех существенных выходов объекта диагностирования 21 и запись их состояний на регистр 24 с исключением записи состояний несущественных для диагностики въ1ходов.

По окончании опроса всех элементов Н 18 по .сигналу на втором выходе де- шифратора 13 триггер управления 4 устанавливается в ноль, запирая элемент И 12. По эгому же сигналу из регистра 24 через блок элементов И 25 поступают сигналы о состоянии существенных выходов объекта 21 на первые входы сумматоров по модулю два 15 и модифицируют в регистре 16 переменную часть адреса следующего входного набора. Сформированный таким образом адрес следующего входного набора поступает из регистра 16 в блок памяти 3. По сигналу считывания на первом входе устройства ИЗ блока памяти 3 считывается следующий входной набор и т, д. После считывания в регистр 7 послед него входного набора в регистр 16 записывается код окончания тестирования, по которому дешифратор2О формирует сиг нал разрещения анализа результатов тестирования. По этому сигналу дешифратор 26 анализирует реакцию объекта 21 и формирует результат диагностирования на своем выходе, В режиме безусловного тестирования триггер 19 устанавливается в едлницу и запирает элементы И 25 на время диагностирования, поэтому адрес спедуюше го входного набора из полей 8 и 9 регистра 7 поступает на регистр 16 без изменения. В остальном работа устройства не отличается от работы в режиме условного тестирования. При изменении типа объекта диагностирования 21 необходимо записать новую программу в блок памяти 3 и в бло памяти 6. Таким образом, введение новых элементов и связей позволяет исключить из числа анализируемых несущественные для диагностики выходы объекта увеличить количество контролируемых выходов объекта диагностирования, не увеличивая формат адреса входных наборов, и тем самым расширить функциональные возмож HOCTg устройства. Формула изобретения Устройство для тестового диагностирования, содержащее первые элементы И первый регистр, первые выходы которого соединены с входами объекта диагностирования, а второй выход с первым вхоаом второго регистра, выход которого соединен с первым входом первого блока памяти, второй вход которого соединен с первым входом устройства, а выход - с 9 8 входом первого регистра, вход первого дешифратора соединен с выходом второго регистра, с. выход - с первым входом второго дешифратора, выход которого соединен с выходом устройства, вторые входы второго дешифратора соединены с выходами объекта диагностирования, вход триггера режима соединен с вторым входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в не«го введены триггер управления, счетчик, третий дешифратор, сумматоры по iv.ofty- . лю два, сдвигающий регистр, второй блок памяти,третий регистр, первый и второй элементы ИЛИ, первый и второй элементы задержки, второй элемента И, по числу выходов объекта диагностирования третьи и четвертые элементы И, каждый из которых соединен первым входом с соответствующим первым выходом третьего дешифратора, вторым входом - с соответствующим выхоаом третьего регистра, выхоаом -с соответствующим пкодом второго элемента ИЛИ, соединенного выходом с первым управляющим входом сдвигающего регистра, информационный вход которого соединен с выходом первого элемента ИЛИ, входы которого соединены с ixoцами соответствующих: третьих элементов И, первые вхоцы которых соецинены соответственно с выходами одноименных четвертых элементов И, вторые входы с соответствующими выходами объекта диагностирования, третий выход первого регистра соединен с первым входом второго блока памяти, соединенного выходом с входом третьего регистра, вторым входом через первый элемент задержки с первым входом устройства и вторым управляющим входом сдвигающего регистра, а через второй элемент задержки - с первым входом триггера управления, соединенного выходом с первым входом второго элемента И, соединенного вторым входом с третьим входом устрой- ства, выходом через счетчик - с входом третьего дешифратора, соединенного вторым выходом с вторым входом триггера управления и первыми входами первых элементов И, соединенных вторыми вхО дами с соответствующими выходами сдвигающего регистра, третьими входами с выходом триггера режима, выходами с первыми входами соответствующих сумматоров по моду|7ю два, вторые входы которых соединены с соответствующими четвертыми выходами первого регистра.

Авторы

Даты

1982-04-15—Публикация

1980-07-23—Подача