Изобретение относится к вычисли- i тельной технике и может быть использовано для синхронизации вычислител-ьных систем.

Известно устройство синхронизации, .содержащее задающий генератор, выходц которого соединены с входами группы линий задержки, выходы которых соединены с входами блоков выработки синхросигналов, выходы блоков которых являются выходами устройства Щ

Недостатком этого устройства является то, что оно вырабатывает только две фазы синхросигналов С1 и С2, сдвинутые один относительно другого на половину такта вычислительной системы, т.е. невозможно эффективно использовать временные интервалы между фазами С1 и С2 для синхронизации блоковс различной глубиной комбинационной логики, что снижает быстродействие системы.

Наиболее близким техническим решением к изобретению является -устройство, содержателе задающий генератор, выходы которого соединены соответственно с входами элементов задержки, выходы которых соединены соответст- венио с входами блоков выработки синхросигналов, каждый из которых содер-.

жит дешифратор, счетчик, селектор, группу элементов И, причем в каждом блоке выработки синхросигналов выход счетчика соединен с входом селектора и входом дешифратора, первый, второй, третий и четвертый выходы которого подключены к первым входам соответственно первого, второго, третьего и четвертого элемента И группы эле10ментов И, первый и второй выходы селектора соединены с перЕЫми входами соответственно пятого и шестого элемента И группы элементов И, а вторые входы элементов И и вход счетчика

15 каждого из блоков выработки синхросигналов соединены с выходом соответствующего элемента задержки первой группы, причем выходы группы элементов И каждого из блоков выработки

20 синхросигналов соединены с входами соответствующего элемента задержки второй группы, выходы которых являются выходами устройства.

Устройство вырабатывает четыре фа25зы синхросигналов, сдвинутых один относительно другого на Ift (где Т ц

длительность машинного такта синхронизируемой вычислительной системы) и на величину выбранной фиксированной

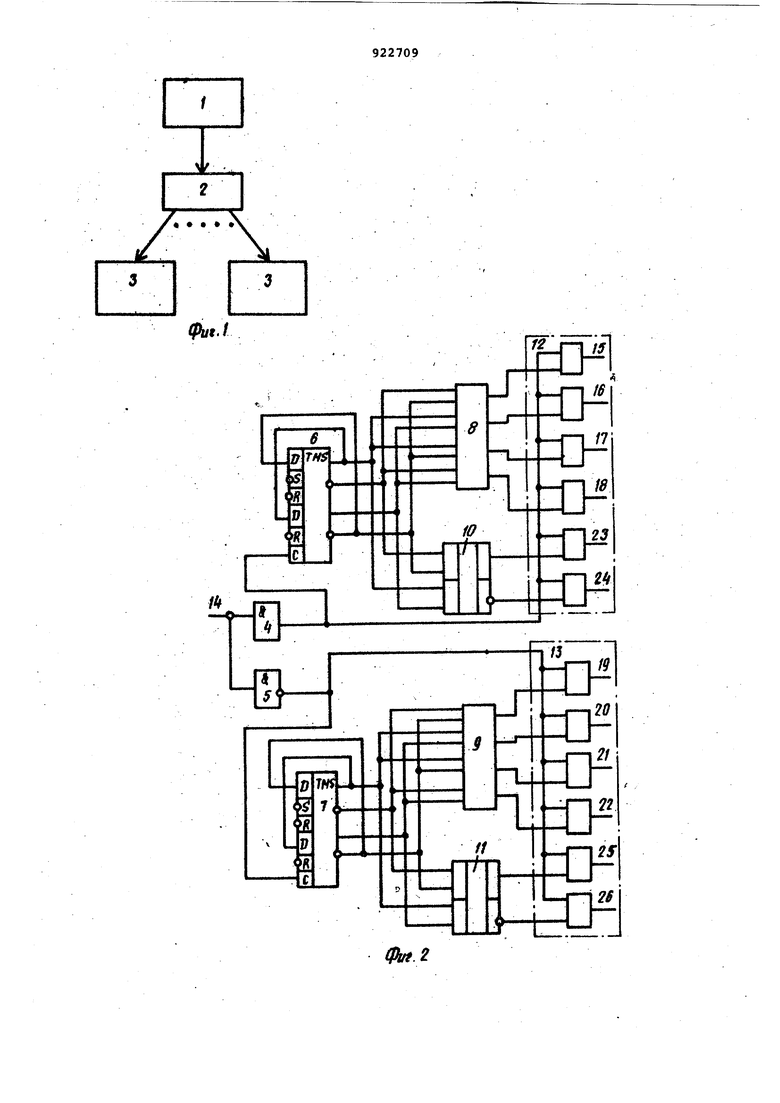

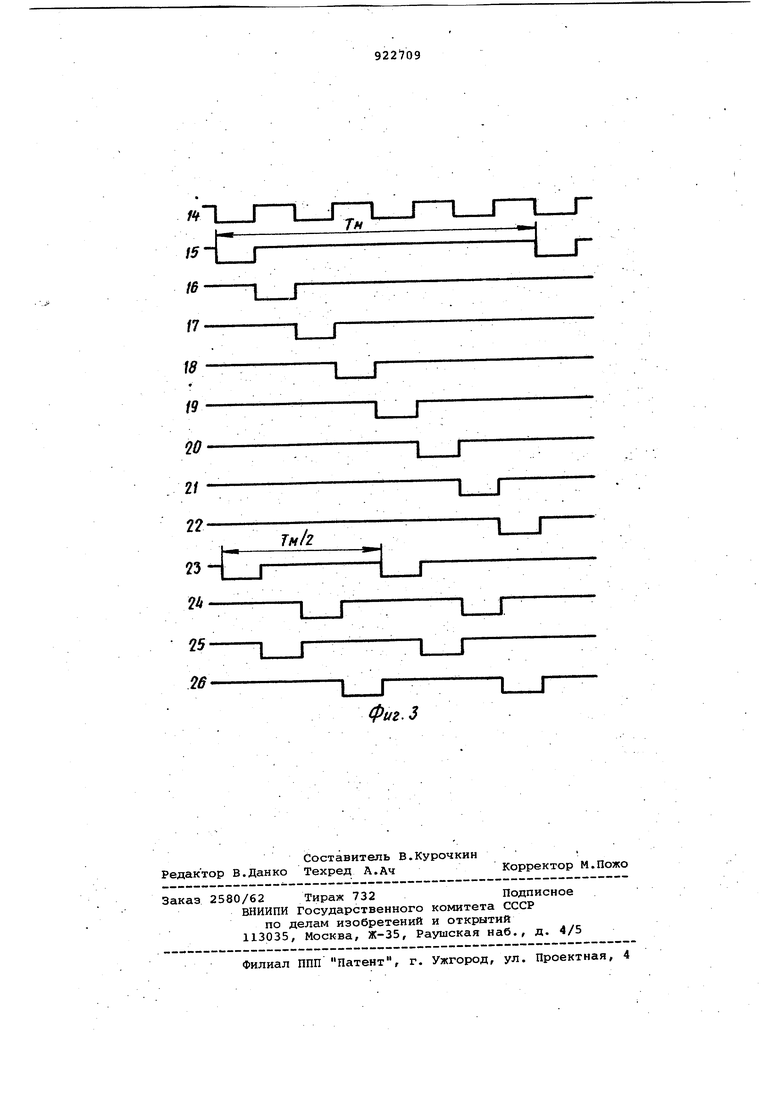

30 задержки 21 и З . . Недостатком данного устройства является то, что сдвиг синхросигналов определяется величиной задержки постоянной для определенной конфигу ции блоков синхронизируемой вычисли тельной, системы. Это не позволяет автоматически изменить частоту зада ющего генератора (и тем самым велич ну Тм и сдвиг синхросигналов один от носительно другого) в процессе вычислений в соответствии с решаемой задачей вычислительной системой для уменьшения времени выполнения команд. Цель изобретения - повышение быст родействия вычислительной системы.. Указанная цель достигается тем, что в устройство, содержащее задающий генератор, выходы которого соединены с входами элементов задержки выходы которых соединены соответственно с входами блоков выработки . синхросигналов, каждый из которых содержит первый счетчик, первый дешифратор, первый селектор, первую группу элементов И, причем в каждом блоке выработки синхросигналов выходы первого счетчика соединены с входами первого селектора и входами первого дешифратора, выходы которого соединены с первыми входами соответственно первого, второго, третьего и четвертого элементов И перво°й группы элементов И, прямой и инверсный выходы первого селектора соединены с первыми входайи соответственно пятого и шестого элементов И первой группы элементов И, дополнительно введены повторитель, элемент НЕ, втррой счетчик, второй дешифратор, второй селектор, вторая группа эле. ментов И, причем в каждом блоке выработки синхросигналов вход.блока выработки синхросигналов соединен со ответственно с входами повторителя и элемента НЕ, выход повторителя соединен с входом первого счетчика и с вторыми входами элементов И первой группы элементов И, выход элемента НЕ соединен с входом второго счетчика,- с первьили входами элементов И второй группы элементов И, выходы второго счетчика соединены с входами второго селектора, второго дешифрато ра, выходы которого соединены соответственно с вторыми входами первого, второго, третьего и четвертого элементов И второй группы элементов И, прямой и инверсный выходы второго селектора соединены соответственно с вторыми входами пятого и шестого элементов И второй группы элементов и, выхода) элементов И первой и втррой групп элементов И соединены с выходами устройстваi Па фиг.1 изображена блок-схема устройства для синхронизации вычислительной системы; а фиг.2 - схема блока выработки синхросигналов; на фиг.З - временная диаграмма синхрйдсигналов. Устройство содержит задающий генератор 1, элемент 2 задержки, блок 3 выработки синхросигналов, повторитель 4, элемент НЕ 5, счетчик б и 7, дешифраторы 8 и 9, селекторы10 и 11 и группы 12 и 13 элементов И. Устройство работает следующим образом. Задающий генератор 1 вырабатывает исходную последовательность синхросигналов, поступающую на входы элементов 2 задержки, служащих для выравнивания синхросигналов на входах 14 блоков 3 выработки синхросигналов. . Эта исходная последовательность.поступает на входы блоков выработки синхросигналов, в каждом из которых поступает на входы элемента НЕ 5, слу|Жащего для инверсии исходной последовательности, и повторителя 4, служащего для выравнивания исходной последовательности внутри блока выработки синхросигналов, с выхода которых последовательность импульсов поступает на входы первого и второго счетчиков б и 7, делят исходную последовательность на четыре и каждый из которых позволяет получить четыре сдвинутые на lUt сигналы длительностьюТ. Сигналы с счетчиков поступают на входам дешифрато- . ров 8 и 9, на выходе кгшдого из которых пoлs aютcя четыре сигнала длительностью Т, сдвинутые один относительно другого на , в совокупности с двух дешифраторов получают сигналы, сдвинутые на Ъ., длительностью ,с периодом Tjti. . . Сигналы с выходов счетчиков поступают также на входы селекторов для получения сигналов, аналогичных сигналам с выходов дешифратора, но имею-i щих период jPoi, Сигналы с выходов дешифраторов и селекторов позволяют управлять первой и второй группами элементов И для получения синхросигналов, имеющих длительность TJ и сдвинутых друг S т,, относительно друга на с периодом (синхросигналы на выkoдax 15-22 блока 3) и ЪУ (синхросигналы на выходах 23-26 блока 3). Период следования синхросигналов в ЭВМ определяется глубиной комбинационной схемы обрабатывающего устройства, т.е. арифметического устройства, в котором максимальная глубина комбинационной схемы логических каскадов (логический каскад равен задержке одной интегральной схемы). Команды управления (условные и безусловные переходы, загрузки) для научных вычислительных задач имеют вес, 40%. Выполнение этих команд не требует использования сумматоров, и в ЭВМ эти команды выполняютоя в процессоре команд, что позволяет уменьшить время выполнения команд управления за счет сокращения количества Т. В процессоре команд используются комбинационные схемы обработки, имею щие, в среднем, 2-3 логических каскада. Изменение периода следования синхросигналов (увеличение частоты задающего генератора автоматически в соответствии с выполняемой командой) позволяет уменьшить время выпол нения команд управления. Время выполнения команд управлеНИН (условные и безусловные переходы загрузки и т.д.) определяется количеством периодов синхросигналов. Выполнение одной команды управления в известном устройстве занимает шесть тактов. При использовании автоматического изменения частоты генератора и схем выработки синхросигналов время выполнения одной команды управления составляет 5,5 тактов, что позволяет повысить производительнос выполнения команд управления на 8%. Кроме увеличения производительности ЭВМ изобретение позволяет увеличить вычислительную мощность ЭВМ. При вычислении задач на ЭВМ возможно возникновение машинной ошибки обусловленной отказом аппаратуры или сбоями в аппаратуре. Сигнал Машинная ошибка перевод ЭВМ из режима Вычисление в режим Повторение. При выполнении режима Повторени многократно (до восьми раз) произво дится повторениевыполнения команду на которой произошел сбой. Если команда не выполняется, то требуется ремонт ЭВМ. При исполнении изобретения имеет ся возможность после 8-кратного пов торения понизить автоматически частоту задающего генератора и повторить режим Повторение. Понижение частоты позволяет уменьшить возникновение сбоев, связанных с перекосом питания. Формула изобретения Устройство для синхронизации вы,числительной системы, содержащее за дающий генератор, выходы которого соответственно соединены с входами элементов задержки, выхода которых соединены соответственно с входами блоков выработки синхросигналов, каждый из которых содержит первый счетчик, первый дешифратор, первый селектор, первую группу элементов И, выходы первого счетчика соединены с входами первого селектора и первого дешифратора , выходы первого детаифратора соединены -соответственно с первыми входами первого, второго, третьего и четвертого элементов И первой группы элементов И, прямой и инверсный выходы первого селектора соединены соответственно с первыми вхо-. дами ПЯТОГО и шестого элементов И первой группы элементов И, о т л и чающее с я тем, что, с целью повышения йдстродействия, в каждый блок выработки синхросигналов дополнительно введены повторитель, элемент НЕ, второй счетчик, второй дешифратор, второй селектор, вторая группа элементов И, причем вход каждого блока выработки синхросигналов соединен соответственно с входами повторителя и элемента НЕ-, выход повторителя соединен с входом первого счетчика и с вторыми входами элементов И первой группы- элементов И,.выход элемента НЕ соединен с входом второго счетчика, с первыми входами элементов И второй группы элементов И, выходы второго счетчика соединены с входами второго селектора, второго дешифратора, выходы которого соединены соответственно с вторыми входами первого, второго, третьего и четвертого элементов И первой группы элементов И, прямой и инверсный выходы второго селектора соединены соответственно с вторыми входами пятого и шестого элемента И второй группы элементов И, выходы элементов И первой и второй групп элементов И соединены с выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Электронная вычислительная машина ЕС-1050. М., Статистика, 1976, с. 254. 2.Авторское свидетельство СССР № 752314, кл. G Об F 1/04, 1978 (прототип) . 3.Королев Л.Н. Структуры ЭВМ и их математическое обеспечение. М., Наука, 1974, с. 92.

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Устройство для синхронизации вычислительной системы | 1978 |

|

SU752314A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

| Устройство для синхронизации цифровой системы | 1981 |

|

SU981980A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

| Устройство для контроля синхронизации | 1983 |

|

SU1200268A1 |

(pof 2

17 W

ч

19 20 21 2223 242526Фиг.З

Авторы

Даты

1982-04-23—Публикация

1980-05-22—Подача