Изобретение относится к вычислительной технике и предназначено для использования в цифровых системах автоматики, рлботакнцих с многофазными кодами.

Цель изобретения - повышение быстродействия и уменьшение количества оборудования.

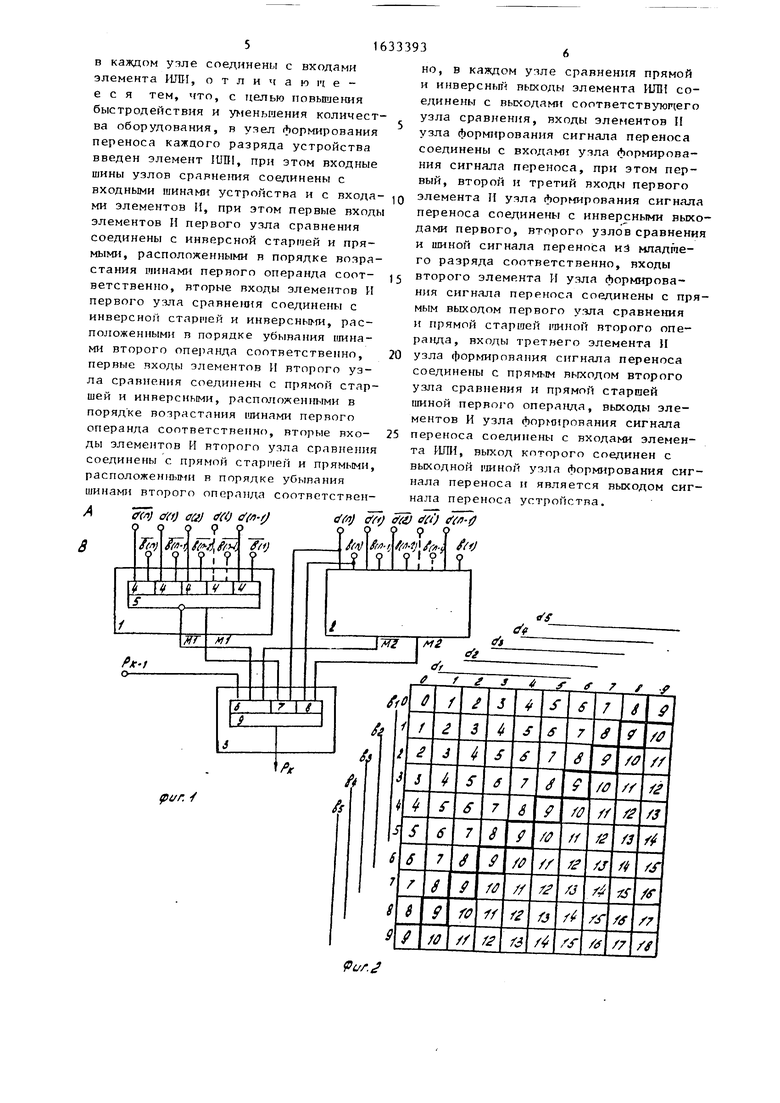

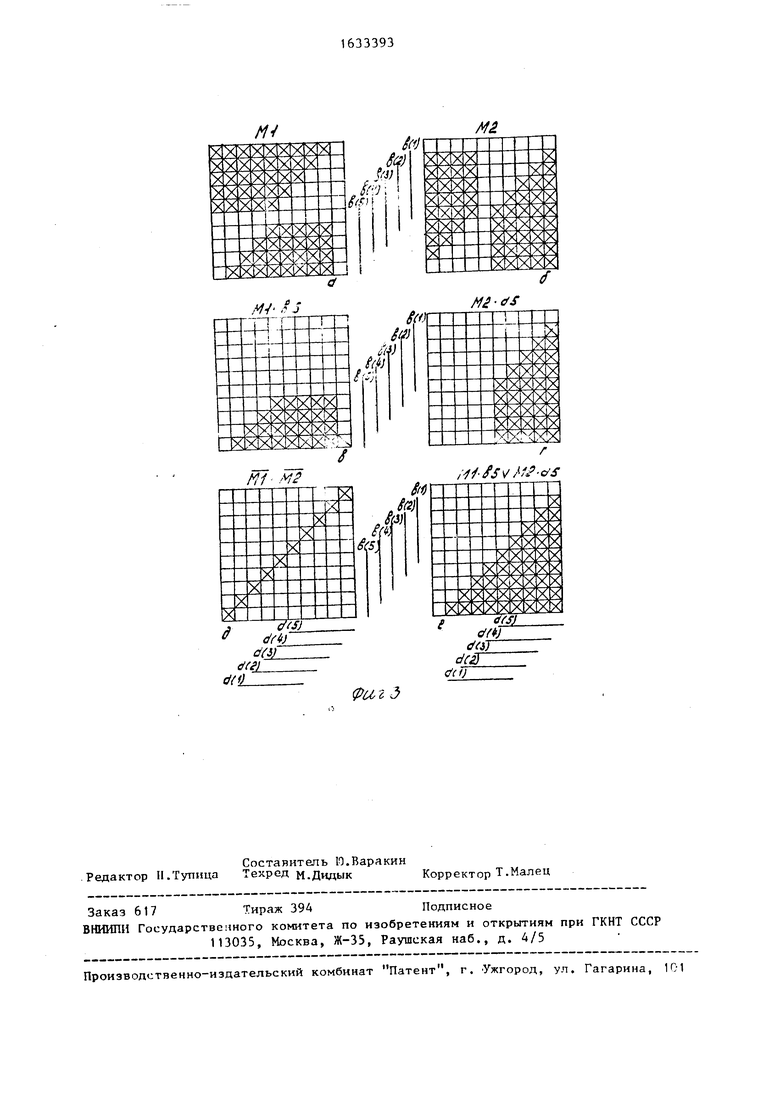

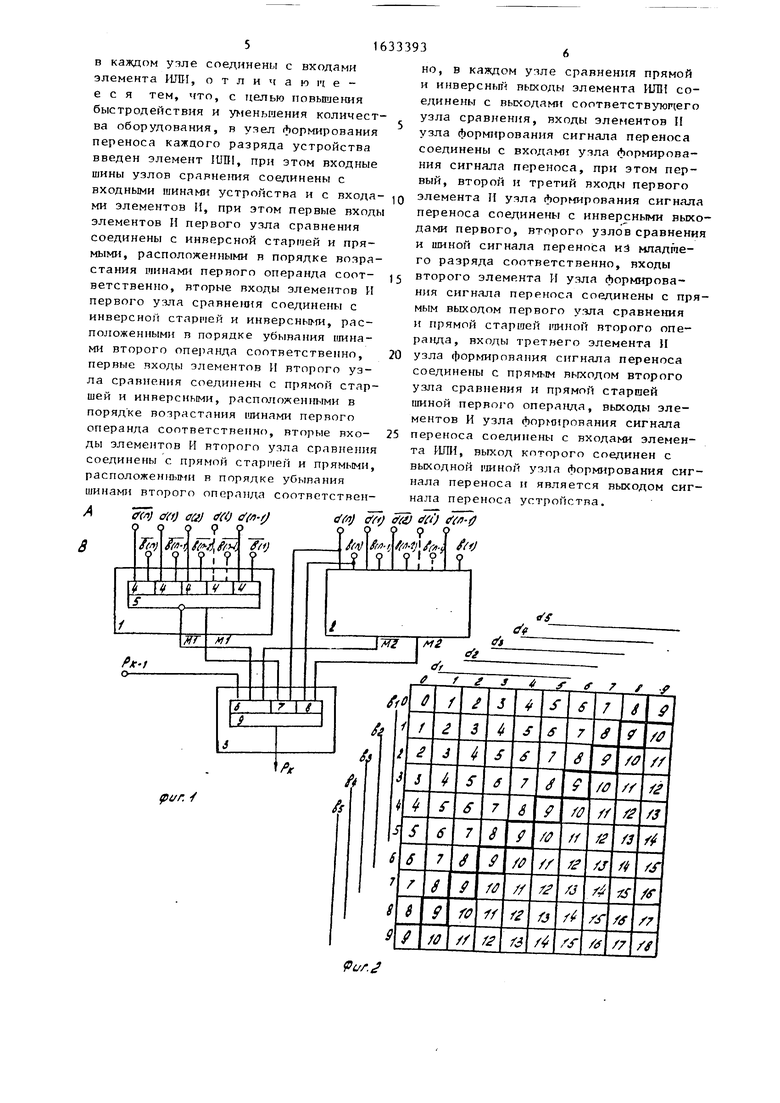

На фиг . 1 приведена функциональная схема одного разряда устройства; на фиг.2 - таблица сложения для пяти- фазного кода (основание систе- 1 счисления N 10); на фиг.З - формирование сигнала переноса.

Устройство состоит из двух узлов 1 и 2 сравнения и узла 3 формирования сигнала переноса, каждый узел сравнения содержит N/2 логических элементов И 4 (где N/2 Y - фазность многофазного кода, N - основание системы счисления) и логический эле мент ИЛИ 5, узел 3 формирования сигнала переноса состоит из трех логических элементов И 6-8 и одного логического элемента ИЛИ 9. Входные иины узлов 1 и 2 сравнения соединены с входами логических элементов И 4, при этом первые входы логических элементов И 4 узла 1 сравнения соединены с шинами операнда А соответственно ар, Я( a2 aF-i вторые входы логических элементов II 4 узла 1 сравнения соединены с пинами операнда В соответственно b

г

Ьр, , , .. . ,Ь, , первые входы логических элементов И 4 узла 2 сравнения соединены с шинами операнда А соответственно a F, a,,

a«.i

F-1

вторые входы логических

элементов И 4 узла 2 сравнения соединены с шинами операнда В соответственно Ьс, bf , , Ь , . . . ,Ъц. Внутреннее строение узлов 1 и 2 сравнения идеи0500 GO

со со

GO

тично, выходы логических элементов И А соединены с входами логического элемента ИЛИ 5, выходы которых соответственно Ml, М1 и М2, М2 соедине- ны с выходными шинами соответствующих узлов 1 и 2 сравнения, входы логических элементов И 6-8 узла 3 формирования сигнала переноса являются входными шинами узла 3 формирования сигнала переноса, входы логического элементами 6 соединены с выходными шинами Ml, M2 узлов 1 и 2 сравнения и шиной переноса из младшего разряда Р k( , входы логического эле- мента И 7 соединены с выходной шиной М1 узла 1 сравнения и шиной bff операнда В, входы логического элемента И 8 соединены с выходной шиной М2 узла 2 сравнения и шиной as опекай- да А, выходы логических элементов И 6-8 соединены с входами логического элемента ИЛИ 9, выход которого является выходной шиной узла 3 формирования сигнала переноса и устройст- ва в целом.

Устройство работает следующим образом.

i

В соответствии с таблицей сложени

цифровых сигналов операндов А и В (фиг.2) на выходных шинах узла 1 сравнения формируется сигнал, определяющий множество цифр результата сложения операндов А и В, который может быть описан логическим уравнением

Ml

Л Ь,

V а , А Ь4 V а2 Л b3V

J a А Ьг V Ч ЛЬ,

и представлен на фиг.За. Логическое умножение с сигналом Ь5 операнда В формирует сигнал результата сложения операндов А и В, определяющих множество цифр, расположенных ниже главной 45 диагонали (результаты сложения больше числа 9), который представлен на фиг.Зв и формируется логическим элементом И 7 узла 3 формирования сигнала переноса. На выходных ши-50

нах узла 2 сравнения формируется сигнал, определяющий множество цифр результата сложения операндов А и В, который может быть описан логическим уравнением55

М2 а5ЛЬ5 а ЛЬ4 Va2 Л Ъ3У I btva4Ab,

, Q 5 0 5

0 5

0

5 0

5

и представлен на фиг.Зб. Логическое умножение с сигналом а формирует сигнал результата сложения операндов А и В, определяющих множество цифр, расположенных ниже главной диагонали (фиг.Зг), и формируется логическим элементом И 8 узла 3 формирования сигнала переноса. Множества М1 A bg и М2 А я перекрываются между собой, а их логическое сложение полностью определяет результат сложения операндов А и В, который больше числа 9 и представлен на фиг.Зе. Результат сложения, равный числу 9, может быть получу логическим умножением множеств I11 и М2 при сигнале переноса из младшего разряда Р х-1 и результате сложения, равном 9, сигнал Р( АМ1 Л М2 формируется логическим элементом И 6, на выходе логического элемента ИЛИ 9 формируется сигнал переноса при суммировании многофазных кодов, который может быть описан логическим выражением Рк Pk, А М2 V М1 А Ь5 V

V М2 Л а5

и является выходным для устройства. Формирование сигнала переноса Р при суммировании многофазных кодов с помощью двух перекрывающихся между собой подмножеств, результатов сложения операндов А и В позволяет исключить промежуточные операции по дешифрации кодов, что в результате повышает быстродействие и уменьшает количество оборудования предлагаемого устройства по сравнению с известным.

Формула изобретения

Устройство для формирования сигнала переноса при суммировании многофазных кодов, содержащее в каждом разряде узел формирования переноса, включающий три элемента И и два узN

ла сравнения, содержащие по --- элементов И (где N - основание системы счисления) и одному элементу ИЛИ, причем входы каждого разряда устройства соединены с прямыми и инверсными шинами, представляющими разряд многофазного кода первого и второго операндов и с шиной переноса из младNшего разряда, выходы --- элементов И

в каждом узле соединены с входами элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия и уменьшения количества оборудования, в узел формирования переноса каждого разряда устройства введен элемент ИЛИ, при этом входные шины узлов сравнения соединены с

но, в каждом узле сравнения прямой и инверсный выходы элемента ИЛИ соединены с выходами соответствующего узла сравнения, входы элементов И узла формирования сигнала переноса соединены с входами узла формирования сигнала переноса, при этом первый, второй и третий входы первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1979 |

|

SU922728A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для суммирования | 1979 |

|

SU868750A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Цифроаналоговый преобразователь с многофазным выходом | 1987 |

|

SU1476611A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для суммирования | 1978 |

|

SU822183A2 |

| Устройство для сравнения кодов | 1982 |

|

SU1080134A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| Устройство для умножения | 1979 |

|

SU826341A1 |

Изобретение относится к вычислительной технике и предназначено для 2использования в цифровых системах автоматики, раПотрюпщх с многофазными кодами. Цель изобретения - повышение быстродействия и уменьшение количества оборудования. Цель достигается тем, что устройство, содержащее в каждом разряде узел формирования переноса, включаюшлй три элеменN та И,и два узла сравнения по --- элементов И (N - основание системы счисления) и одному элементу ИЛИ, содержит в узле формирования переноса каждого разряда устройства элемент ИЛИ с соответстпуюпими связями.3 ил.

входными шинами устройства и с входа- дэлемента И узла формирования сигнала

ми элементов И, при этом первые входыпереноса соединены с инверсными выхоэлементов И первого узла сравнениядами первого, второго узлов сравнения

соединены с инверсной старшей и пря-и шиной сигнала переноса из младгаемыми, расположенными в порядке возра-го разряда соответственно, входы

стания шинами первого операнда COOT- jвторого элемента И узла формироваветственно, вторые входы элементов И первого узла сравнения соединены с инверсной старпей и инверсными, расположенными в порядке убывания шинами второго операнда соответственно, первые входы элементов И второго узла сравнения соединены с прямой старшей и инверсными, расположенными в порядке возрастания шинами первого операнда соответственно, вторые входы элементов И второго узла сравнения соединены с прямой старшей и прямыми, расположенными в порядке убывания шинами второго операнда соответственА В

ния сигнала переноса соединены с прямым выходом первого узла сравнения и прямой старшей шиной второго операнда, входы третнего элемента И

узла формирования сигнала переноса соединены с прямым выходом второго узла сравнения и прямой старшей шиной первого операнда, выходы элементов И узла формирования сигнала

переноса соединены с входами элемента ИЛИ, выход которого соединен с выходной шиной узла формирования сигнала переноса и является выходом сигнала переноса устройства.

///

/

AY M2

M2.

M2-JS

/

/j/ /SV/W-o S

Фаг J

| Шагурин И.И | |||

| транзисторно-транзисторные логические схемы | |||

| - М.: Советское радио, 1974, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Г, 06 F 7/49, 1982. | |||

Авторы

Даты

1991-03-07—Публикация

1989-02-03—Подача