Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализации вычисления функций х cos (pv у- sin аргументов, представленных в прямом коде в форме с фиксированной запятой.

Известно устройство для вычисления тригонометрических функций, содержащее три регистра, два сумматора-вычислителя, блок суммирования, сумматор, два сдвигателя, блок памяти итерационных констант, блок номера итерации и блок управления.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для вычислений функций х cos у , содержащее два мультиплексора, пять регистров, два сумматора, блок постоянной памяти, инвертор, элементы И, элементы ИЛИ, элемент НЕ и элемент ИЛИ-НЕ.

Недостатком известного устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия устройства.

В устройство для вычисления функций х cos р и у sin (p , содержащее блок памяти задания начальных условий, два мультиплексора, пять регистров и два сумматора, причем выходы первого и второго сумматоров соединены с первыми информационными входами соответственно первого и второго мультиплексоров, вторые информационные входы которых соединены соответственно с первым и вторым выходами блока памяти, выходы первого и второго мультиплексоров соединены с информационными входами соответственно первого и второго регистров, выходы которых подключены к входам первого и второго слагаемых соответственно первого и второго сумматоров и выходом соответственно косинуса и синуса устройства, вход старших разрядов аргумента которого соединен с адресным

Ј

VI СА)

ю

CJ

J

N3

входом блока памяти, выходы вторых слагаемых первого и второго сумматоров соединены соответственно с выходом третьего регистра и инверсным выходом четвертого регистра, дополнительно введены с третье- 5 го по пятый мультиплексоры, блок управления и с первого по третий сдвигатели, выходы которых соединены с первыми информационными входами соответственно с третьего по пятый мультиплексоров, вторые 10 информационные входы которых соединены соответственно с входом младших разрядов устройства, первым и вторым входами блока памяти, выходы с третьего по пятый мультиплексоров соединены с ин- 15 формационными входами соответственно с третьего по пятый регистров, выходы которых соединены с информационными входами соответственно с первого по третий сдвигателей, причем блок управления со- 20 держит элемент ИЛИ, элемент ИЛИ-НЕ и К элементов И (где К - количество младших разрядов аргумента), первый вход элемента ИЛИ соединен с выходом первого элемента И, инверсный вход которого соединен с вы- 25 ходом элемента ИЛИ-НЕ, входы которого соединены с выходами соответствующих разрядов пятого регистра, с первого по к-й инверсные входы (к-И)-го элемента И, (k

1,2К-1) соединены с выходами с первого 30

по k-й разрядов пятого регистра, (к+1)-й вход (k+1)-ro элемента И соединен с выходом (к+1)-го разряда пятого регистра, вторые входы элемента ИЛИ и первые элементы И соединены с входами соответ- 35 ственно запуска и тактовых импульсов устройства, выход конца преобразования которого соединен с выходом элемента ИЛИ-НЕ и управляющими входами всех мультиплексоров, выходы элементов И со 40 второго по k-й соединены с входами соответствующих разрядов всех сдвигателей, выход элемента ИЛИ соединен с входами записи всех регистров.

Все элементы предлагаемого устройст- 45 ва могут быть выполнены на серийно выпускаемых микросхемах.

В основе работы устройства лежит следующий алгоритм вычисления функций х

cos sin p . Значение положительного 50 аргумента р , определяемого двоичным кодом а о ои О-2 ... an, где а0- разряд целой части, а 1 а 2 ... о. п - разряды дробной части аргумента, представляются в виде

оо

р1+)2 аоЙ1С2... a4+00..0(2q + lOq+2.-. иг).

где q n/2; q e{n/2п}; 0 р .

По значению величины р ч определяются начальные n-разрядные приближения вычисляемых функций xo cos p 1 и Уо sin p ч . Последующие вычисления производятся с использованием рекуррентных соотношений:

Г ак ак-1 - dK-i;

(1)

Ьк Ьк-1 + Ск-1

Уке{1,2..д} { ск Ск-1 2-JK; dK aVi jK (lK-l-2-JK) -2JK, где к - номер выполняемой итерации;

t Ј {1,2,...,n-q} - количество итераций, необходимое для получения результата.

Значение JK при выполнении к-й итерации выбирается равным номеру старшего единичного числового разряда кода 1к-1 согласно выражению

jK min{j e N/lK-i(|)1}.(2)

Начальные значения переменных определяются соотношениями

ао хо,Ьо уо, с0 хо , do уо 2-q,

lo ( 2+2 Сп+1)) -2q.(3)

Вычисления продолжаются до тех пор,

пока в результате реализации очередной t-й

итерации будет выполнено условие

-ч

V It (0 0.

i-H

(4)

Полученные в результате вычислений значений at и bt являются искомыми значениями функций х cos p и у sin (p соответственно с абсолютной погрешностью, не превышающей .

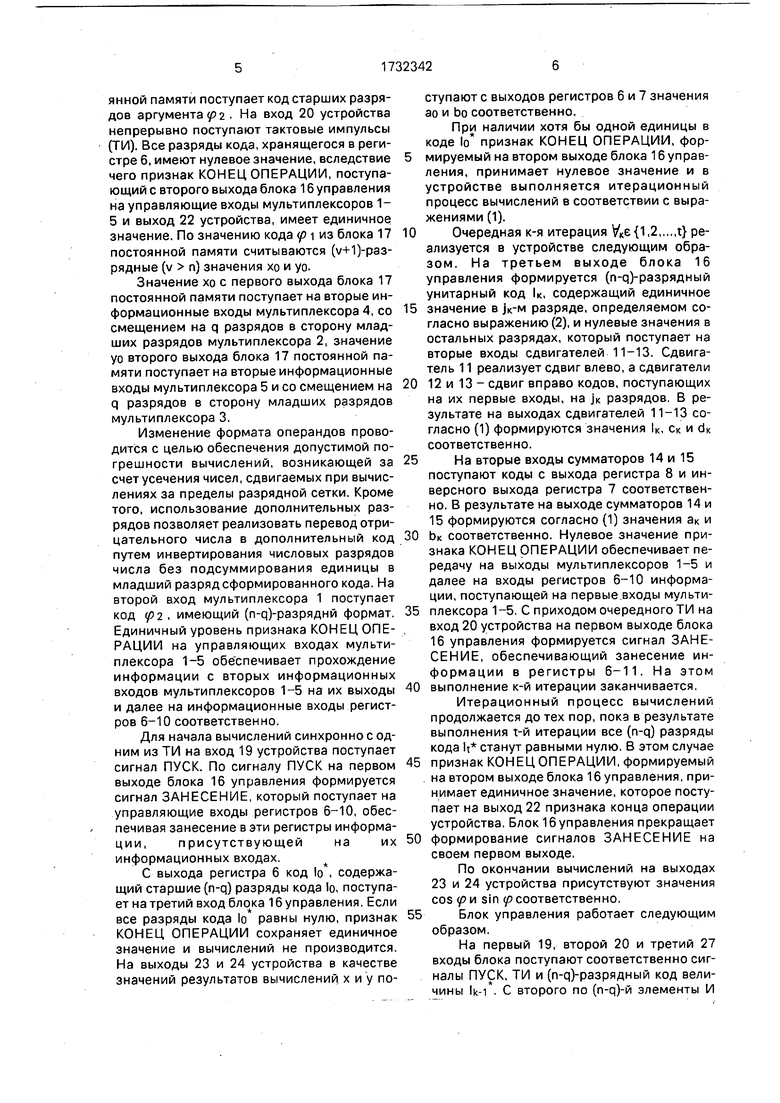

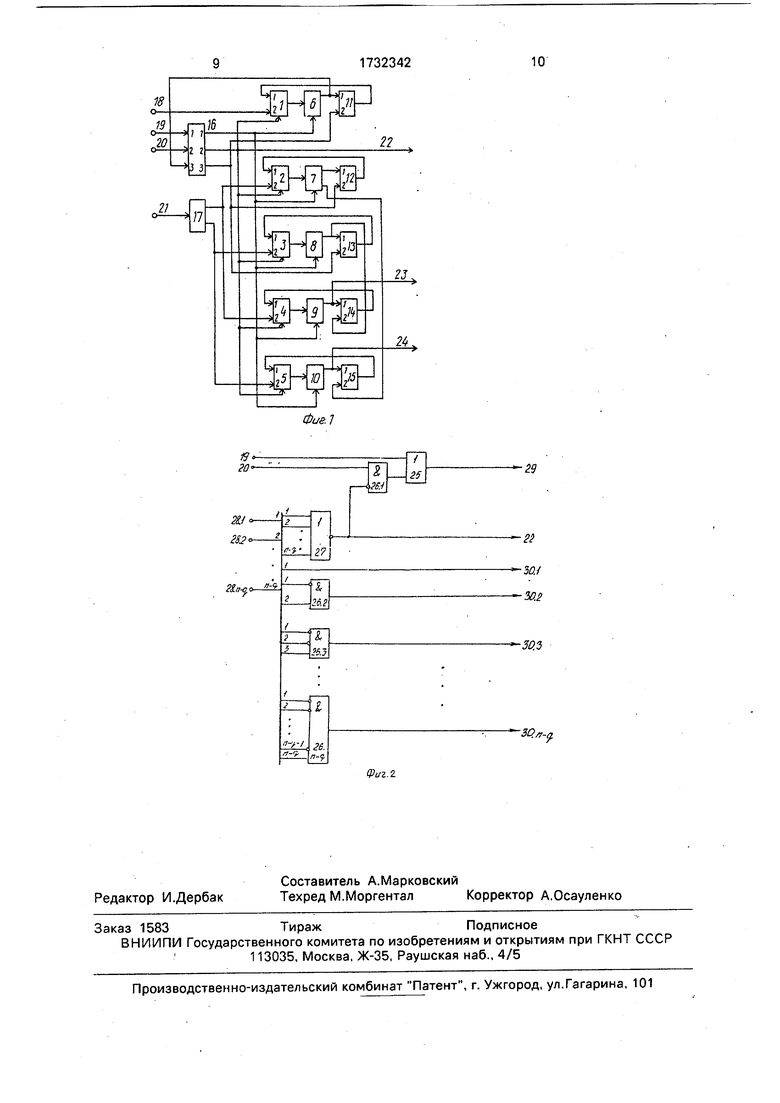

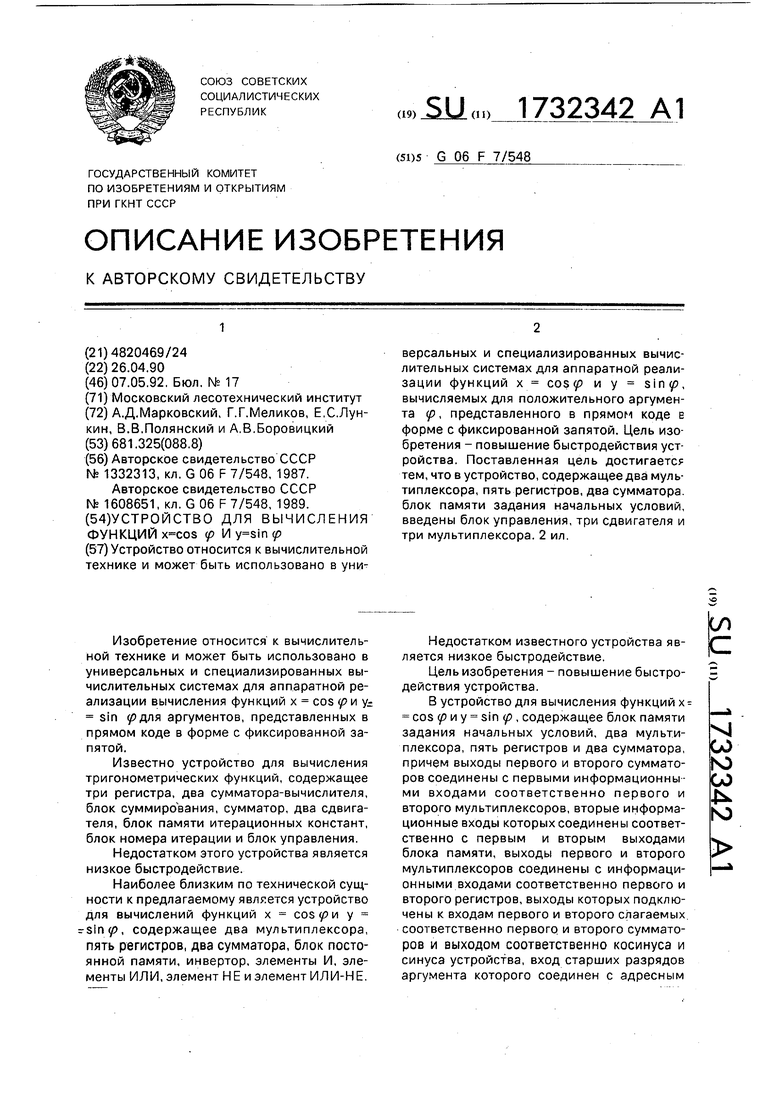

На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема блока управления.

Устройство содержит мультиплексоры 1-5, регистры 6-10, сдвигатели 11-13, сумматоры 14-15, блок 16 управления и блок 17 постоянной памяти, а также имеет вход 18 младших разрядов аргумента, вход 19 запуска, тактовый вход 20 и вход 21 старших разрядов аргумента, выход 22 признака конца операции, выход косинуса 23 и синуса 24.

Блок управления содержит элемент ИЛИ 25, n-q элементов И 26, элемент ИЛИ- НЕ 27, а также имеет первый 19, второй 20 и третий 28 входы, первый 29, второй 22 и третий 30 выходы.

Устройство работает следующим образом.

В исходном состоянии на вход 18 устройства и далее на второй информационный вход мультиплексора 1 поступает код младших разрядов аргумента (рг , дополненный единицей в (n-q+1)-M разряде. На вход 21 устройства и далее на вход блока 17 постоянной памяти поступает код старших разрядов аргумента р г На вход 20 устройства непрерывно поступают тактовые импульсы (ТИ). Все разряды кода, хранящегося в регистре 6, имеют нулевое значение, вследствие чего признак КОНЕЦ ОПЕРАЦИИ, поступающий с второго выхода блока 16 управления на управляющие входы мультиплексоров 1- 5 и выход 22 устройства, имеет единичное значение. По значению кода р 1 из блока 17 постоянной памяти считываются (v+1)-pas- рядные (v п) значения хо и уо.

Значение хо с первого выхода блока 17 постоянной памяти поступает на вторые информационные входы мультиплексора 4, со смещением на q разрядов в сторону младших разрядов мультиплексора 2, значение уо второго выхода блока 17 постоянной памяти поступает на вторые информационные входы мультиплексора 5 и со смещением на q разрядов в сторону младших разрядов мультиплексора 3.

Изменение формата операндов проводится с целью обеспечения допустимой погрешности вычислений, возникающей за счет усечения чисел, сдвигаемых при вычислениях за пределы разрядной сетки. Кроме того, использование дополнительных разрядов позволяет реализовать перевод отрицательного числа в дополнительный код путем инвертирования числовых разрядов числа без подсуммирования единицы в младший разряд сформированного кода. На второй вход мультиплексора 1 поступает код р2 , имеющий (п-р)-разряднй формат. Единичный уровень признака КОНЕЦ ОПЕРАЦИИ на управляющих входах мультиплексора 1-5 обеспечивает прохождение информации с вторых информационных входов мультиплексоров 1-5 на их выходы и далее на информационные входы регистров 6-10 соответственно.

Для начала вычислений синхронно с одним из ТИ на вход 19 устройства поступает сигнал ПУСК. По сигналу ПУСК на первом выходе блока 16 управления формируется сигнал ЗАНЕСЕНИЕ, который поступает на управляющие входы регистров 6-10, обеспечивая занесение в эти регистры информации, присутствующей на их информационных входах.

С выхода регистра 6 код lo , содержащий старшие (n-q) разряды кода lo, поступает на третий вход блока 16 управления. Если все разряды кода lo равны нулю, признак КОНЕЦ ОПЕРАЦИИ сохраняет единичное значение и вычислений не производится. На выходы 23 и 24 устройства в качестве значений результатов вычислений х и у поступают с выходов регистров 6 и 7 значения ао и bo соответственно.

При наличии хотя бы одной единицы в коде lo признак КОНЕЦ ОПЕРАЦИИ, формируемый на втором выходе блока 16 управления, принимает нулевое значение и в устройстве выполняется итерационный процесс вычислений в соответствии с выражениями (1).

0 Очередная к-я итерация VKe{1,2t} реализуется в устройстве следующим образом. На третьем выходе блока 16 управления формируется (п)-разрядный унитарный код IK, содержащий единичное

5 значение в JK-M разряде, определяемом согласно выражению (2), и нулевые значения в остальных разрядах, который поступает на вторые входы сдвигателей 11-13. Сдвига- тель 11 реализует сдвиг влево, а сдвигатели

0 12 и 13 - сдвиг вправо кодов, поступающих на их первые входы, на JK разрядов. В результате на выходах сдвигателей 11-13 согласно (1) формируются значения к, Ск и JK соответственно.

5 На вторые входы сумматоров 14 и 15 поступают коды с выхода регистра 8 и инверсного выхода регистра 7 соответственно. В результате на выходе сумматоров 14 и

15формируются согласно (1) значения ак и 0 Ьк соответственно. Нулевое значение признака КОНЕЦ ОПЕРАЦИИ обеспечивает передачу на выходы мультиплексоров 1-5 и далее на входы регистров 6-10 информации, поступающей на первые входы мульти5 плексора 1-5. С приходом очередного ТИ на вход 20 устройства на первом выходе блока

16управления формируется сигнал ЗАНЕСЕНИЕ, обеспечивающий занесение информации в регистры 6-11. На этом

0 выполнение к-й итерации заканчивается.

Итерационный процесс вычислений продолжается до тех пор, пока в результате выполнения t-й итерации все (n-q) разряды кода It станут равными нулю. В этом случае

5 признак КОНЕЦ ОПЕРАЦИИ, формируемый на втором выходе блока 16 управления, принимает единичное значение, которое поступает на выход 22 признака конца операции устройства. Блок 16 управления прекращает

0 формирование сигналов ЗАНЕСЕНИЕ на своем первом выходе.

По окончании вычислений на выходах 23 и 24 устройства присутствуют значения cos p и sin p соответственно.

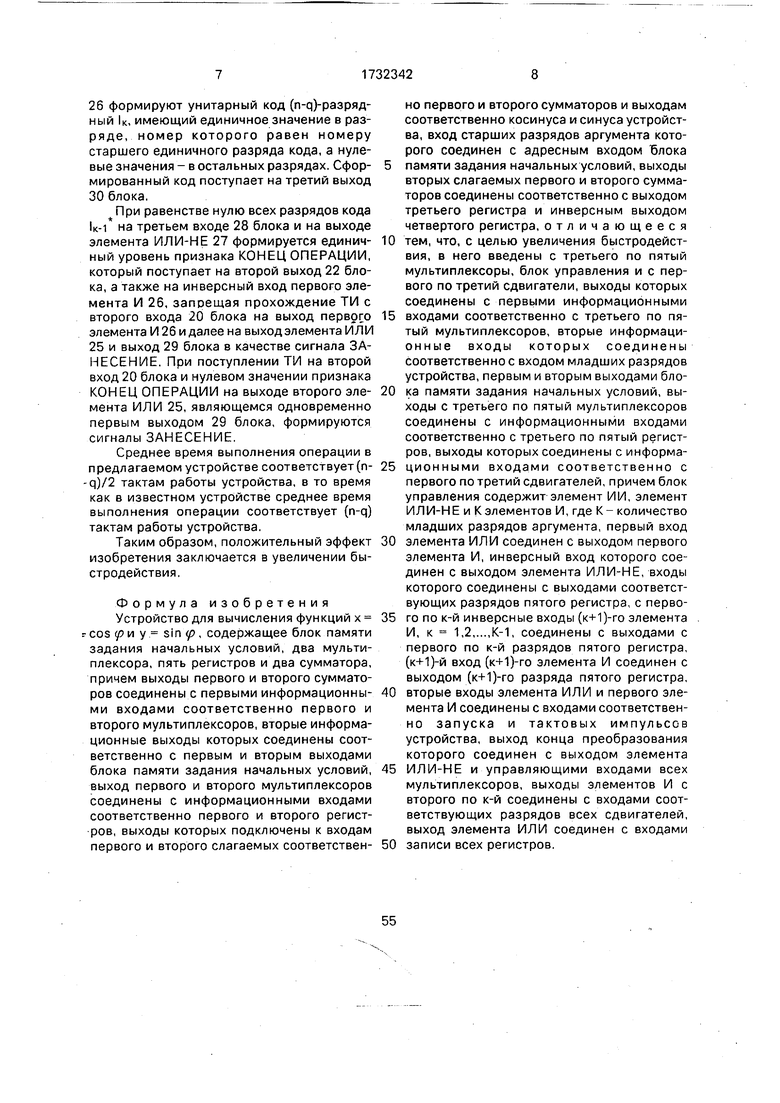

5 Блок управления работает следующим образом.

На первый 19, второй 20 и третий 27 входы блока поступают соответственно сигналы ПУСК, ТИ и (п)-разрядный код величины lk-1 . С второго по (n-qj-й элементы И

26 формируют унитарный код (п-р)-разряд- ный IK, имеющий единичное значение в разряде, номер которого равен номеру старшего единичного разряда кода, а нулевые значения - в остальных разрядах. Сфор- мированный код поступает на третий выход 30 блока.

При равенстве нулю всех разрядов кода К-Г на третьем входе 28 блока и на выходе элемента ИЛИ-НЕ 27 формируется единич- ный уровень признака КОНЕЦ ОПЕРАЦИИ, который поступает на второй выход 22 блока, а также на инверсный вход первого элемента И 26, запрещая прохождение ТИ с второго входа 20 блока на выход первого элемента И 26 и далее на выход элемента ИЛИ 25 и выход 29 блока в качестве сигнала ЗАНЕСЕНИЕ. При поступлении ТИ на второй вход 20 блока и нулевом значении признака КОНЕЦ ОПЕРАЦИИ на выходе второго эле- мента ИЛИ 25, являющемся одновременно первым выходом 29 блока, формируются сигналы ЗАНЕСЕНИЕ.

Среднее время выполнения операции в предлагаемом устройстве соответствует(п- -q)/2 тактам работы устройства, в то время как в известном устройстве среднее время выполнения операции соответствует (n-q) тактам работы устройства.

Таким образом, положительный эффект изобретения заключается в увеличении быстродействия.

Формула изобретения Устройство для вычисления функций х cos р и у sin p, содержащее блок памяти задания начальных условий, два мультиплексора, пять регистров и два сумматора, причем выходы первого и второго сумматоров соединены с первыми информационны- ми входами соответственно первого и второго мультиплексоров, вторые информационные выходы которых соединены соответственно с первым и вторым выходами блока памяти задания начальных условий, выход первого и второго мультиплексоров соединены с информационными входами соответственно первого и второго регистров, выходы которых подключены к входам первого и второго слагаемых соответствен-

но первого и второго сумматоров и выходам соответственно косинуса и синуса устройства, вход старших разрядов аргумента которого соединен с адресным входом Ъпока памяти задания начальных условий, выходы вторых слагаемых первого и второго сумматоров соединены соответственно с выходом третьего регистра и инверсным выходом четвертого регистра, отличающееся тем, что, с целью увеличения быстродействия, в него введены с третьего по пятый мультиплексоры, блок управления и с первого по третий сдвигатели, выходы которых соединены с первыми информационными входами соответственно с третьего по пятый мультиплексоров, вторые информационные входы которых соединены соответственно с входом младших разрядов устройства, первым и вторым выходами блока памяти задания начальных условий, выходы с третьего по пятый мультиплексоров соединены с информационными входами соответственно с третьего по пятый регистров, выходы которых соединены с информа- ционными входами соответственно с первого по третий сдвигателей, причем блок управления содержит элемент ИИ, элемент ИЛИ-НЕ и К элементов И, где К- количество младших разрядов аргумента, первый вход элемента ИЛИ соединен с выходом первого элемента И, инверсный вход которого соединен с выходом элемента ИЛИ-НЕ, входы которого соединены с выходами соответствующих разрядов пятого регистра, с первого по к-й инверсные входы (к+1)-го элемента

И, к 1,2К-1, соединены с выходами с

первого по к-й разрядов пятого регистра, (к+1)-й вход (к+1)-го элемента И соединен с выходом (к+1)-го разряда пятого регистра, вторые входы элемента ИЛИ и первого элемента И соединены с входами соответственно запуска и тактовых импульсов устройства, выход конца преобразования которого соединен с выходом элемента ИЛИ-НЕ и управляющими входами всех мультиплексоров, выходы элементов И с второго по к-й соединены с входами соответствующих разрядов всех сдвигателей, выход элемента ИЛИ соединен с входами записи всех регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Устройство для вычисления квадратного корня из суммы квадратов | 1990 |

|

SU1751751A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

Устройство относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных системах для аппаратной реализации функций х cos p и у sirup, вычисляемых для положительного аргумента р, представленного в прямом коде в форме с фиксированной запятой. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее два мультиплексора, пять регистров, два сумматора блок памяти задания начальных условий, введены блок управления, три сдвигателя и три мультиплексора. 2 ил.

2&/

Ј

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций @ и @ | 1988 |

|

SU1608651A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-07—Публикация

1990-04-26—Подача