(54) МНОГОПРОГРАММНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Распределитель импульсов | 1980 |

|

SU884136A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

| Регистр сдвига | 1980 |

|

SU877618A1 |

| Многопрограмный распределитель импульсов | 1987 |

|

SU1443163A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

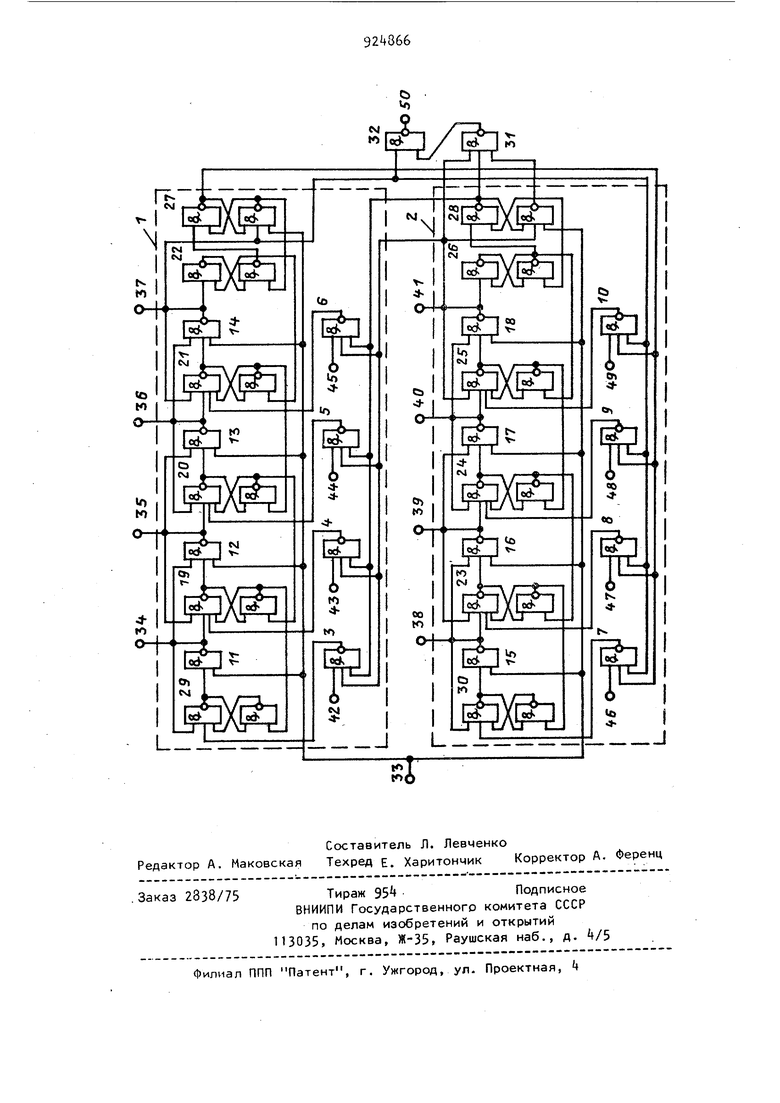

Изобретение относится к импулЬсной технике и может быть использовано в устройствах, где необходимо деление последовательности входных импульсов на число (как целое так и дробное), задаваемое в процессе работы устройства соответствующим управляющим сигналом. Кррме того, предлагаемый делител может быть использован для распределения счетных импульсов по К выходным шинам, где К задается в процессе работы устройства соответствующим управляющим сигналом. Известен делитель частоты с программным управлением, содержащий ком мутатор входных импульсов, три счетч ка импульсов, три логических элемента ИЛИ, осуществляющих коммутацию поступления импульсов из счетчика l Недостатком известного устройства является большое количество обору дования и значительная сложность уст ройства Наиболее близким техническим решением к предлагаемому является многопрограммный делитель частоты, содержащий два выходных логических элемента ИЛИ-НЕ и два п-разрядных рас-пределителя, каждый разряд которых со-держит триггер памяти, комму та ционньгй триггер и управляющий логический элемент ИЛИ-НЕ, а последний разряд каждого распределителя, кроме того, содержит дополнительный коммутационный триггер 2. Недостатком известного устройства является выполнение его на большом количестве оборудования, а следовательно, низкая надежность. Цель изобретения - повышение надежности работы устройства. Поставленная цель достигается тем, что вМногопрограммный делитель частоты, содержащий два выходных логических элемента и два п-разрядных распределителя, каждый разряд которых содержит триггер памяти и управляю392 4щий логический элемент, а последний разряд каждого распределителя, кроме того, содержит коммутационный триггер, причем к первому входу управляющего логического элемента каждого разряда обоих распределителей подкг1ючена шина управления данным ра рядом распределителей, единичный выход коммутационного триггера одного распределителя соединен с вторым вхо дом управляющего логического элемент каждого разряда другого распределителя, единичный и нулевой выходы ком мутационного триггера второго распределителя соединены соответственно с первым и вторым входами первого вы ходного логического элемента, выход которого соединен с первым входом второго выходного логического элемента, к выходу которого подключена выходная шина, в каждый распределитель введены дополнительный триггер, а в кажд| 1й из разрядов распределителей - логический элемент И-НЕ, выход которого соединен с первым входом логического элемента И-НЕ последующего разряда, с первым единичным входом триггера памятиданного разряда, с вторым единичным входом триг гера памяти предыдущего разряда и с информационным выходом данного разряда, единичный выход триггера памят каждого разряда (кроме последнего) распределителей соединен с вторым входом логического элемента И-НЕ последующего разряда, а нулевой выход триггера памяти каждого разряда (кро ме первого) - с нулевым входом тригг ра памяти предыдущего разряда, выход управляющего логического элемента каждого разряда (кроме первого) обоих распределителей соединен с третьим единичным входом триггера памяти предыдущего разряда, выход логического элемента И-НЕ последнего разряда данного распределителя соединен с первым нулевым входом коммутационно го триггера данного распределителя и с третьим входом управляющего логического элемента каждого разряда дру гого распределителя, нулевой аход триггера памяти последнего разряда данного распределителя .соединен с нулевым выходом коммутационного триг гера данного распределителя, единичный вход которого соединен с нулевым выходом триггера памяти последнегд разряда данного распределителя, единичный выход дополнительного триггера каждого распределителя соединен с г1.ервым входом логического элемента И-НЕ первого разряда данного распреелителя, выходы управляющего логического элемента и логического элемента И-НЕ первого разряда каждого распреелителя подключены к единичным вхоам дополнительного триггера данного распределителя, к нулевому входу которого подключен нулевой выход триггера памяти первого разряда данного распределителя, выход логического элемента И-НЕ последнего разряда первого распределителя соединен с вторым входом второго выходного логического элемента, выход логического элемента И-НЕ последнего разряда второго распределителя соединен с третьим входом первого выходного логического элемента И, а входная шина подключена к второму входу логического элемента И-НЕ каждого разряда распределителей и к второму нулевому входу коммутационного триггера каждого распределителя, кроме того, управляющие и входные логические элементы выполнены на логических элементах И-НЕ, На чертеже представлена функциональная схема многопрограммного делителя частоты. Устройство содержит первый и второй четырехразрядные распределители 1 и 2, управляющие логические элементы 3-10 И-НЕ, логические элементы 11-18 И-НЕ, триггеры 19-26 памяти, коммутационные триггеры 27-28, дополнительные триггеры 29-30, выходные логические элементы 31-32 И-НЕ, s входную шину 33, информационные выходные шины , управляющие шины ) выходную шину 50 дробного коэффициента деления. Устройство работает следующим образом . В исходном состоянии входной сигнал на шине 33 отсутствует (равен логическому нулю). Триггер 22 памяти установлен в единичное состояние, а остальные триггеры памяти и дополнительные триггеры установлены в нулевое состояние. В этом случае на выходах логических элементов 11-18 И-НЕ, на выходе выходного логического элемента 31 И-НЕ и выходах коммутационного триггера 27 сигналы равны логической единице, а на выходе выходного логического элемента 32 И-НЕ логический нуль, коммутационный триггер 28 находится в нулевом состоянии. Пусть, например, необходимо получить коэффициент деления 2,5. Для этого необходимо подать сигнал, равный логической единице, на управляющие входы t8 и 3, а на остальные управляющие входы - логический нуль. Тогда на выходе управляющего логического элемента 9 И-НЕ появляется сигнал, равный логическому нулю, который устанавливает триггер памяти 2 в единичное состояние. Состояния остальных триггеров памяти не изменяют ся, так как на выходах остальных управляющих логических элементов распределителей сигналы равны логической единице. С приходом на шину 33 первого счетного импульса на нулевом выходе коммутационного триггера 27 появляется сигнал, равный логическому нулю, 20 который устанавливает триггер 27 .памяти в нулевое состояние. Одновременно на выходе логического элемента 17 И-НЕ появляется сигнал,равный логическому нулю, который устанавливает триггер 25 памяти в единичное с стояние, а сигнал, равный логическому нулю, с нулевого выхода последнего устанавливает логическую единицу на нулевом выходе триггера 2 памяти. Наличие связи с выхода логического элемента 17 И-НЕ на вход логического элемента 18 И-НЕ и на единичный вход триггера 2k памяти препятствует появлению на выходах последних сигнала, равного логическому нулю, в время действия первого счетного импульса. В паузе после первого счетного импульса коммутационный триггер 27 устанавливается в нулевое состояние и закрывает управляющие логи ческие элементы 7-10 И-НЕ, а триггер 2k памяти также устанавливается в нулевое состояние и закрывает логический элемент 17 И-НЕ. Следовательн первый счетный импульс сдвигает единицу из триггера памяти в триггер 25 памяти. Аналогично с приходом второго. счетного импульса единица из триггера 25 переписывается через элемент 18 И-НЕ в триггер 26 памяти. При этом на выходах коммутационного триг гера 28 устанавливаются сигналы, равные логической единице. Наличие связи с выхода логического элемента 18 И-НЕ на выходы логических элементов 3-6I 31 И-НЕ препятствует появлению на их выходах сигнала, равного логическому нулю. В паузе после второго счетного импульса на выходах логических элементов k, 31 И-НЕ появляются сигналы, равные логическому нулю. Первый из них через логический элемент 32 И-МЕ поступает на выходную шину 50, а второй устанавливает триггер 19 памяти в единичное состояние. С приходом третьего счетного импульса сигнал, равный логическому нулю, с нулевого выхода коммутационного триггера 28 устанавливает триггер 2б памяти в нулевое состояние и закрывает логический элемент 31 И-НЕ. При этом прекращается формирование сигнала на шине 50. Одновременно происходит сдвиг единицы из триггера 19 памяти через элемент 12 в триггер 20 памяти. В паузе после третьего счетного импульса коммутационный триггер 28 устанавливается в нулевое состояние и закрывает логические элементы 3-6, 31 И-НЕ. Четвертый счетный импульс производит сдвиг единицы из триггера 20 памяти через элемент 13 И-НЕ в триггер 21 памяти, а пятый счетный им- : пульс сдвигает единицу из триггера 21 памяти в триггер 22 памяти. При этом сигнал, равный логическому нулю, с выхода логического элемента }k И-НЕ поступает через логический элемент 32 И-НЕ на выходную шину 50, а также блокирует логические элементы 7 10 И-НЕ, так как на единичном выходе коммутационного триггера 27 появляется логическая единица. В паузе после пятого счетного импульса прекращается формирование сигнала на выходной шине 50, а на выходе логического, элемента 9 И-НЕ появляется сигнал, равный логическому нулю, который устанавливает триггер 2 памяти в единичное состояние. Следовательно, схема возвращается в исходное состояние. Таким образом, на пять входных импульсов на выходной шине 50 формируются два импульса, т.е. осуществляется деление на 2,5. При этом с информационных выходов kQ, k, 35-37 могут быть распределены сигналы, равные по длительности счетным импульсам, а частота этих сигналов в пять раз меньше частоты счетных импульсов. Коэффициент деления 1,5 получают при наличии на управляющих входах kk и 49 логической единицы, а 3,5 на управляющих входах k2 и 7 и т.д. По сравнению с известным предлага емое устройство выполнено на меньшем количестве оборудования, что ведет к уменьшению потребляемой мощности и к повышению надежности устройства. Формула изобретения 1. Многопрограммный делитель частоты, содержащий два выходных логических элемента и два п-разрядных распределителя, каждый разряд которых содержит триггер памяти и управляющий логический элемент, а последний разряд каждого распределителя, кроме того, содержит коммутационный триггер, причем к первому выходу управляющего логического элемента кажд го разряда обоих распределителей под ключена шина управления данным разрядом распределителей, единичный выход коммутационного триггера одного распределителя соединен с вторым вхо дом управляющего логического элемента каждого разряда.другого распределителя, единичный и нулевой выходы коммутационного триггера второго распределителя соединены соответственно с первым и вторым входами первого выходного логического элемента, выход которого соединен с первым входом второго выходного логического элемента, к выходу которого подключена выходная шина, отличающийся тем,что, с целью повышения надежности, в каждый распределитель введены дополнительный триггер, а в каждый из разрядов распределителей - логический элемент И-НЕ, выход которого соединен с первым входом логического элемента И-НЕ последующего разряда, с первым единичным входом триггера памяти данного разряда, с вторым единичным входом триггера памяти предыдущего разряда и с информационным выходом данного разряда, единичный выход триггера памяти каждого разряда (кроме последнего) распределителей соединен с вторым входом логического элемента И-НЕ последующего разряда, а нулевой выход триггера памяти каждого разряда (крюме первого) - с нулевым входом триггера памяти предыдущего разряда, выход управляющего логического эле9

мяти первого разряда данного распределителя, выход логического элемента И-НЕ последнего разряда первого распределителя соединен с вторым входом второго выходного логического элемента, выход логического элемента И-НЕ последнего разряда второго распределителя соединен с третьим входом первого выходного логического элемента И, а входная шина подключена к второму входу логического элемента И-НЕ каждого разряда распределителей и к второму нулевому входу коммутационного триггера каждого распределителя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-04-30—Публикация

1980-02-14—Подача