Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах, . -где необходимо Деление частоты импульсов на 15 и на 7,5. По основному авт. св. МЬ 818О22 известно устройство, содержащее четыре разряда, каждый из которых включает в себя элемент И-НЕ, триггер памяти и коммутационный триггер, взсрд которого подключен ко входной шине, причем в каждом из первой трех разрядов единичный выход триггера памяти соединен с единичньм входом коммутационного триг гера, единичный выход которого соединен с первым входом элемента И-НЕ, а нулевой выход - с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров памяти предыдущих разрядов и со вторым входом элемента И-Н предыдущего разряда, выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго разряда, вькод элемента И-НЕ второго разряда соединен с ед1ганчным и нулевым входами коммутационного триггера третьего разряда, выход элемента И-НЕ третьего разряда соединен с единичный входом коммутационного триггера четвертого разряда, единичный выход , которого соединен с единичным входом триггера памяти этого же разряда, с нулевыми входами коммутационньк триг геров и триггеров памяти предыдущих разрядов и вторым входом элемента И-НЕ третьего разряда, нулевой выход коммутационного триггера четвертого разряда соединен с нулевьтми входами триггеров памяти и коммутационных триггеров предьшущих разрядов, первьй и второй входы элемента И-НЕ четвертого разряда соединены с нулевыми выходами триггера памяти и коммутационного триггера данного разряда, нулевые -входц комму- тационного триггера четвертого соединены с выходами элементов И-НЕ третьего и четвертого разрядов, единичный вход с нулевым входом коммутационного триггчэра третьего разряда, и с вькодом элемента И-НЕ первого past ря;, а единичный выход - с четвертым входом элемента И-НЕ первого , при этом нулевые выходы коммутационных триггеров третьего и четвертого разрядов соединены с третьими входами элементов И-НЕ соответственно первого и третьего разрядов fl}

Недостаток известного устройства ограниченные функциональные возможности, не позволяющие осуществлять де- ление частоты следования импульсов на 7,5.

Цель изобретения - расширение функциональных возможносавй, зй счет получения коэффициента деления равного 7,5.

Эта цель достигается тем, что в делитель частоты спедованшз импульсов, содержащий четьфе разряда, каждый из ко торых включает в себя элемент И-НЕ, триггер памяти и коммутационный триггер, вход которого подключен ко входной шине, причем в каждом из первых трех разрядов единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный выход которого соединен с первым входом эле мента И-НЕ, а нулевой выход - с единичным входом трип ра памяти дйнного разряда, с нулевыми входами коммутационных триггеров памяти предыдущих разрядов и со вторым входом элемента И-НЕ предыдущего разряда, выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго разряда, выход элемента И-НЕ второго разряда соединен с единичным и нулевым входами коммутационного тригге ра-, третьего разряда, выход элемента И-НЕ третьего разряда соединен с единичным входом коммутационного триггера четвертого разряда, единичньй выход которого соединен с единичным входом Памяти этого же разряда, с нулевыми входами коммутационных триггеров и триггеров памяти предыдущих разрядов и вторым входом элемента И-НЕ третьего разряда, нулевой выход коммутационного триггера четвертого разряда соединен с нулевыми входами триггеров памяти и коммутационных триггеров предыдущих разрядов, а первый и второй входы элемента И-НЕ четвертого; разряда соедине ны с нулевыми выходами триггера памяти и коммутационного триггера данного разряда, нулевые входы коммутационного триггера четвертого разряда соединены

I с выходами элементов И-НЕ третьего и четвертого разрядов, единичный вход с нулевьпл входом коммутационного триггера третьего разряда, и с выходом эле5 мента И-НЕ первого разряда, а единичный выход - с четвертым входом элемента И-НЕ первого разряда, при этом нулевые выходы коммутационных триггеров третьего и четвертого разрядов соедине0 ны с третьими входами элементов И-НЕ соответственно первого и третьего разР$ЩОВ, введены дополнительные элементы И-НЕ, первый, второй и третий входы пербого из которых соединены соответ5 ственно с выходом элемента И-НЕ первого разряда и с единичным выходом триггера памяти третьего разряда, а вькод - с первым входом второго дополнительного элемента И-НЕ, второй вход

0 KOTopciro соединен с нулевьгм выходом коммутационного триггера четвертого разряда,

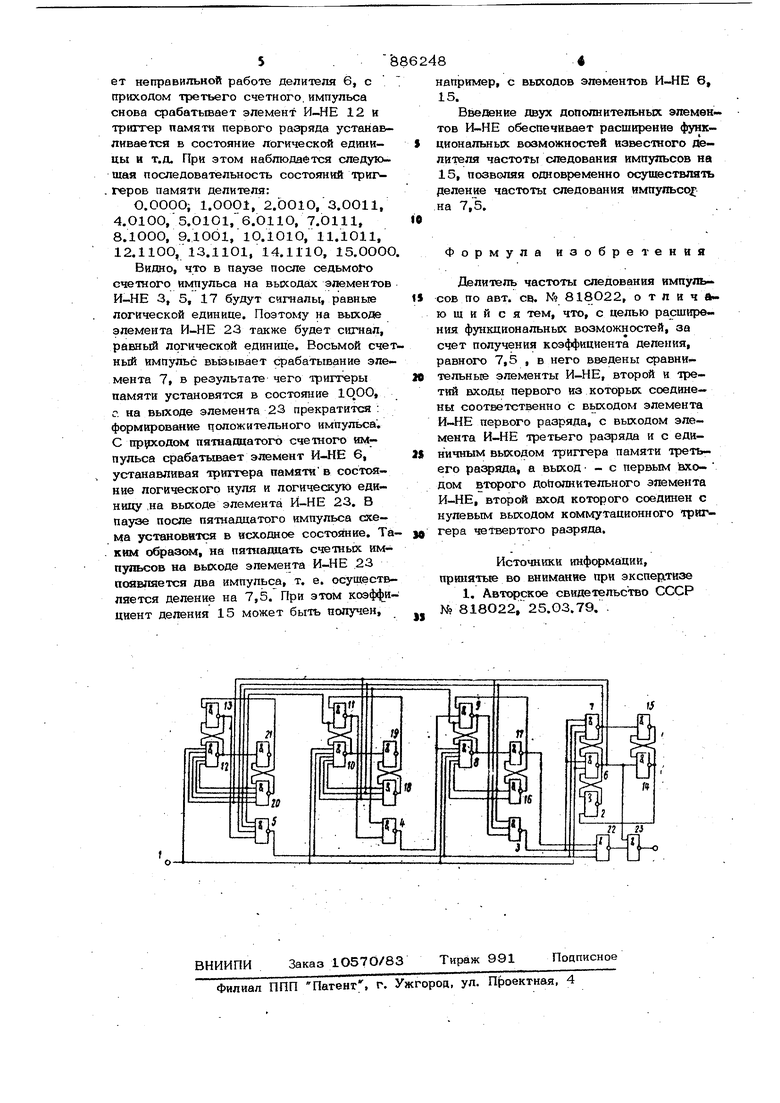

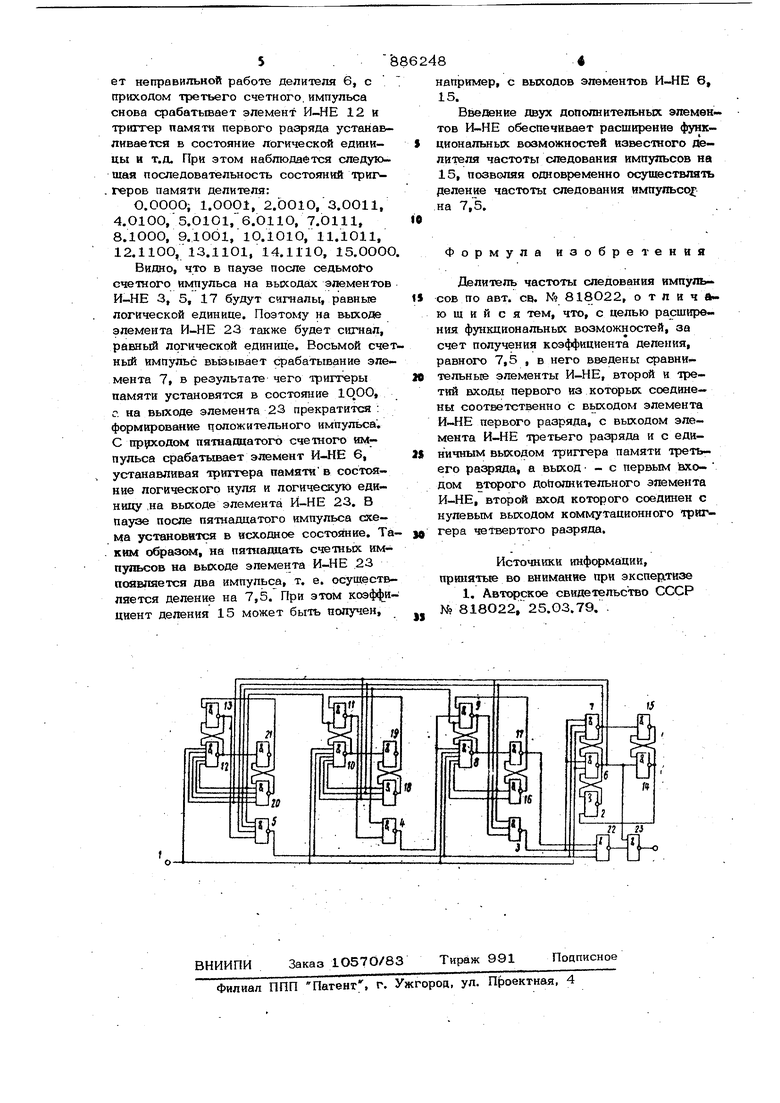

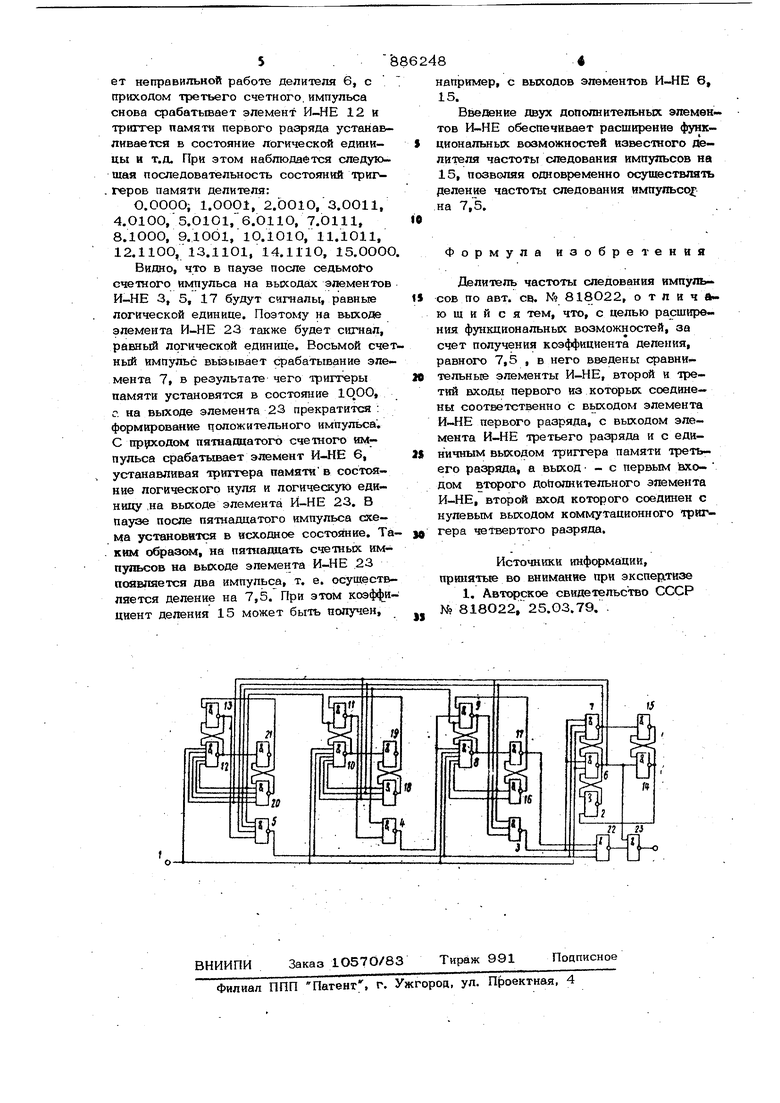

На чертеже представлена структурная схема устройства..

5 Устройство содержит входную шину 1, четыре счетных разряда, каждый из которых содержит элемент И-НЕ 2-5, коммутационный триггер и триггер памяти. Коммутационные триггеры выполнены на

0 элементах И-НЕ 6-13, а триггеры памяти вьтолнены на элементах И-НЕ 14-21. Входной сигнал поступает на входную шину 1.

Принцип работы делителя заключается в следующем.

В исходном состоянии все триггеры памяти находятся в нулевом состоянии, а выходной , поступающий по шине 1, отсутствует и равен логическому нулю. В этом случае на выхсзЯах элементов И-НЕ 2-5, 15, 17, 19, 21 сигнал равен логическому О, а на выходах остальньрс элементов И-НЕ - логической 1, Поэтому с приходом первого

счетного импульса на шину 1 фабатывает только элемент 12, устанавливая триггер памяти первого разряди в состояние логичесжой единицы. В паузе после первого счетного импульса на выходе эпемента И-НЕ 5 появляется логическая единица с приходом второго счетного импульса срабатьшает элемент И-НЕ 10, устанавливая триггер Памяти второго раа ряда в состояние логической единицЫ| а

5 триггер памяти первого разряда - в со стояние логического ну11я. Наличие свя- . зн с выхода элемента И-НЕ 1О на входы элементов И-НЕ 5, 12 препятству5. ет неправильной работе делителя 6, с гфихояом третьего счетного, импульса снова срабатьюает элемент И-НЕ 12 н трюгтер памяти первого разряда устанавливается в состояние логической единицы и т.д. При этом наблюдается следующая последовательность состо5гаий триг- . герое памяти делителя: O.OOOOi 1.0О01, 2.0010, 3.0011, 4.О100,5.О1О1,б.ОИО, 7.О111, 8ЛООО, 9.lObl,l0.101O, 11.1011, 12.1100, 13.1101, 14.1110, 15.0000 Видно, что в паузе после седьмого счетного импульса на вькодах элементов И-НЕ 3, 5, 17 будут сигналы, равные логической единице. Поэтому на выходе элемента И-НЕ 23 также будет сигнал, равньй логической единице. Восьмой сче ный импульс вызывает срабатывание эле мента 7, в результате чего триггеры памяти установятся в состояние 10ОО, с. на выходе элемента 23 прекратится : формирование положительного импульса, С пятнадцатого счетнохч) mvt- пульса срабаты ет элемент И-НЕ 6, устанавливая триггера памятив состояние логического нуля и логическую единицу .на выходе элемента Й-НЕ 23. В паузе после пятнадцатого импульса схема установится в исходное состодаие. Та КИМ образе, на пят11адашть счетных импульсов на выходе элемента И-НЕ 23 появляется два импульса, т. е. осуществ ляется деление на 7,5. При этом коэффи циент деления 15 может быть получен, 8 например, с выходов элементов И-НЕ 6, 15. Введение двух дополнительных элемен тов И-НЕ обеспечивает расширение функциональных возможностей известного делителя частоты следования импульсов на 15, позволяя одновременно осуществлять деление частоты следования импупьсо ; на 7,5. Формула изобретения Делитель частоты следования импульсов по авт. св. № 818О22, отличающийся тем, что, с целью расщирвния функциональных возможностей, за счет получения коэффициента деления, равного 7,5 , в него введены сравни тельнью элементы И-НЕ, второй и третий входы первого из которых соединены соответственно с вьхходом элемента первого разряда, с вьосодом элемента И-НЕ третьего разряда и с единичным выходом триггера памяти третьего , а выход - с первым входом второго Дополнительного элемента И-НЕ, второй вход которого соединен с нулевым выходом коммутационного триггера четвертого разряда. Источники информации, принятые во внимание при экспе{;1тизе 1. Автс зское свидетельство СССР №818022, 25.03.79. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU873417A1 |

| Делитель частоты | 1979 |

|

SU845291A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

Авторы

Даты

1981-11-30—Публикация

1980-03-28—Подача