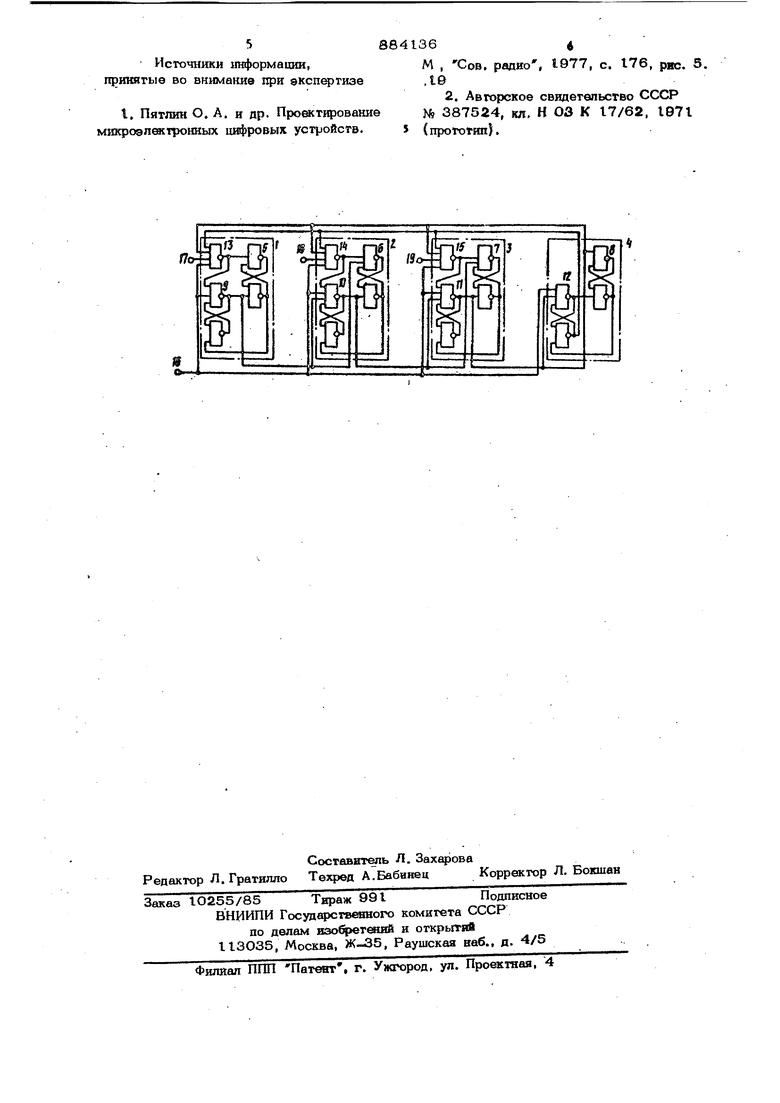

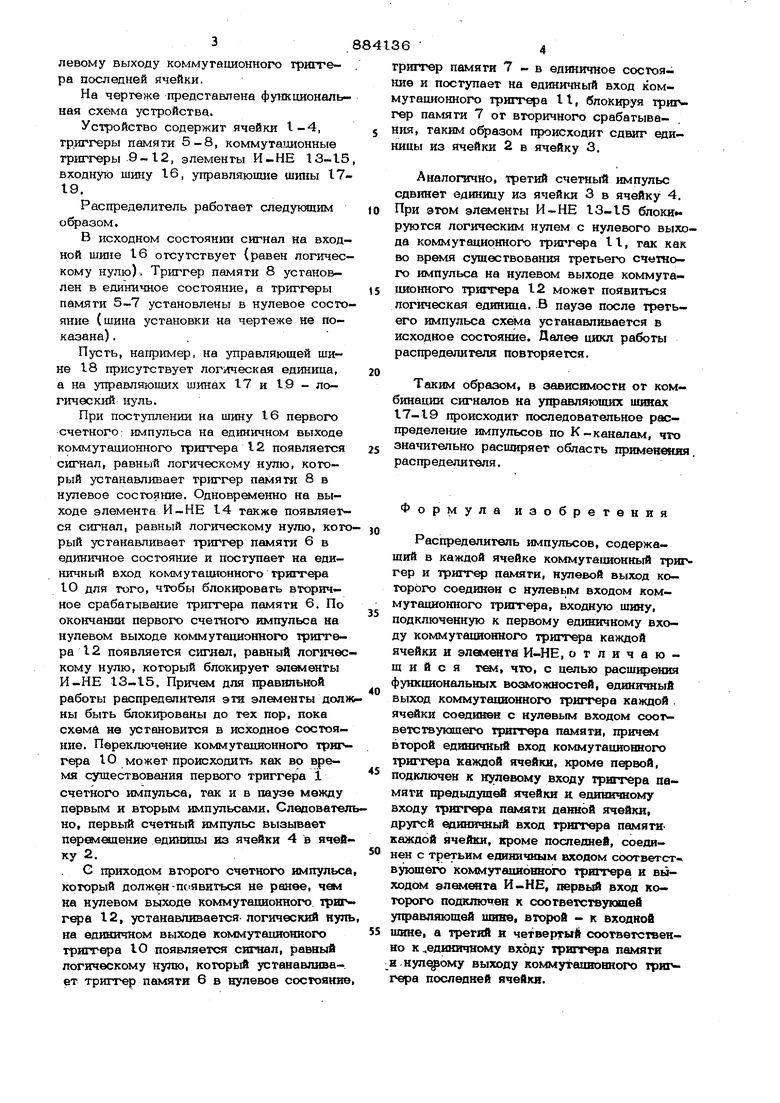

Изобретение огносигся к автоматике и вычислительной технике и может быть ис пользовано в различных устройствах для распределения сигналов по К-выходным шинам, где К-1, 2,..., N. Известен распределитель импульсов, содержащий ячейки памяти, каждая из ко торых состоит из триггера памяти и ком мутационного триггера С Наиболее близким к изобретению техническим решением является распределитель импульсов, содержащий в каждой ячейке коммутационный триггер и тригге памяти, а также входную шину, подключе ную к единичному входу коммутационых триггеров и элементы И-НЕ.. Недостатком устройств является нево можность изменения в процессе работы числа каналов, по которым происходит распределесше сигналов. С целью расширения функциональных возможностей в распределителе импульс содержащем в каждой ячейке Коммутационный триггер и триггер памяти, нулевой выход которого соединен с нулевым входом коммутационного триггера, входную шину, подключенную. к первому единичному входу кoм Iyтaциoннoгo триггера каждой ячейки и элементы И-НЕ, единичный выход коммутационного триггера каждой ячейки соединен с нулевым входом Соответствующего триггера памяти, причем второй единичный вход коммутац1юнного триггера каждой ячейки, кроме первой, подключен к нулевому входу триггера памяти предыдущей ячейки и ешиигдаому входу триггера памяти данной ячейки, )й едишгчный вход триггера памяти каждой ячейки, кроме последней, соединен с третьим единичным входом соответствующего коммутационного триггера и выхот дом элемента И-НЕ, первый вход которого подключен к соо гнете гвующой управляюв1ей шине, второй - к входной urmie, а третий и четвертый соответстпешю к единичному входу триггера памяти и нулевому выходу коммугационного триггера последней ячейки. На чергеже предсгавлена функциональная схема устройства. Устройство содержит ячейки 1.-4, триггеры памяти 5-8, коммутационные триггеры 9 - 12, элементы И-НЕ 13-15 входную шину 16, управляющие шины 1719. Распределитель работает следующим образом, В исходном состоянии сигнал на входной шине 16 отсутствует (равен логическому нулю). Триггер памяти 8 установлен в единичное состояние, а триггеры памяти 5-7 установлены в нулевое состо яние (шина установки на чертеже не показана) .. Пусть, например, на управляющей шине 18 присутствует логическая единица, а на управляющих шинах 17 и 1.9 - логический нуль. При поступлении на шину 16 первого счетного, импульса на единичном выходе коммутационного триггера 12 появляется сигнал, равный логическому нулю, котхэрый устанавливает триггер памяти 8 в нулевое состояние. Одновременно на выходе элемента И-НЕ 14 также появляется сигнал, равный логическому нулю, кото рый устанавливает триггер памяти 6 в единичное состояние и поступает на единичный вход коммутационного триггера 1О для того, чтобы блокировать вторичное срабатывание триггера памяти 6. По окончании первого счетного импульса на нулевом выход.е коммутационного триггера 12 появляется сигнал, равный логичес кому нулю, который блокирует эп&леаты И-НЕ 13-15. Причем для правильной работы распределителя эти элиvleнты долж ны быть блокированы до тех пор, пока схемй не установится в исходное состояние. Переключение коммутационного триггера 10 может происходить как во время существования первого триггера 1 счетного импульса, так и в паузе между первым к вторым импульсами. Следовател но, первый счетный импульс вызывает перемещение единицы нз ячейки 4 в ячей ку 2. G приходом второго счетного импульса который должен-появиться не ранее, чем на нулевом выходе коммутационного триг гера 12, устанавливается-логический нул на единичном выходе коммутационного триггера Ю появляется сигнал, равный логическому нулю, который устанавливает триггер памяти 6 в нулевое состояние 64 триггер памяти 7 - в единичное состояие и поступает на единичный вход коммутационного триггера II, блокируя триггер памяти 7 от вторичного срабатывания, таким образом происходит сдвиг единицы из ячейки 2 в ячейку 3. Аналогачно, третий счетный импульс сдвинет единицу из ячейки 3 в ячейку 4. При этом элементы И-НЕ 13-15 блоки руются логическим нулем с нулевого выхода коммутационного триггера 11, так как во время существования третьего счетного импульса на нулевом выходе коммутационного триггера 12 может появиться логическая единица. В паузе после третьего импульса схема устанавливается в исходное состояние. Далее цикл работы распределителя новторяется. Таким образом, в зависимости от комбинации сигналов на управляющих шяяах 17-19 происходит последовательное рас- пределе1ше импульсов по К-каналам, что значительно расщиряет область применения, распределителя. Формула изобретения Распределитель импульсов, содержащий в каждой ячейке коммутационный триггер и триггер памяти, нулевой выход которого соединен с нулевь1М входом коммутационного триггера, входную щину, подключенную к первому единичному входу коммутационного триггера каждой ячейки и И-НЕ, отличающийся т&л, что, с целью расширения функциональных возможностей, единичный выход коммутационного триггера каждой . ячейки соединен с нулевым входом соот ветствукицего триггера памяти, причем второй единичный вход коммутационного триггера каждой ячейкн, кроме первой, подключен к нулевому входу триггера памяти предыдущей ячейкн и единичному входу триггера памяти данной ячейки, другсй единичный вход грштера памятикаждой ячейки, кроме последней, соединен с третьим единичным входом соответст вующего коммутационного триггера и выходом алемента И-НЕ, первый вход которого подключен к соогвегс1«ующей управляющей шине, второй - к входной щине, а третий и четвертый соответственно к единнчнш у входу триггера памягя и. выходу коммутационного триггера последней ячейки. Источники информашш, принятые во внимание при експертизе 1. Пятпин О. А. и др. Проистирование микроэпектронных цифровых устройств.J М , Сов. радио , 1977, с. 176, ртс. 5. Д0 2. Авторское свидегепьство СССР № 387524, кл. Н ОЗ К 17/62, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Регистр сдвига | 1980 |

|

SU877618A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2020 |

|

RU2726497C1 |

| Устройство для построения программируемых логических автоматов | 2023 |

|

RU2814507C1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

Г7(

Авторы

Даты

1981-11-23—Публикация

1980-02-14—Подача