I

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах, где необходимо деление частоты следования импульсов на нечетное число.

Известен делитель частоты следования импульсов, содержащий триггеры памяти, коммутационные триггеры и элементы И-НЕ

1 Однако данное устройство содержит большое количество оборудования и вследствие этого низкая надежность.

Наиболее близким к предлагаемому является устройство, содержащее четыре разряда, каждый из которых содержит элемент И-НЕ, триггер памяти и коммутационный триггер, соответствующие входы каждого из которых соединены со входной шиной, причем единичнь1е выходы триггеров памяти первых трех разрядов соединены с единичными входами коммутационных триггеров тех же разрядов, единичные выходы которых соединены с первыми входами элементов ИНЕ тех же разрядов, а нулевые выходы коммутационных триггеров каждого из первых трех разрядов соединены с единичными

входами триггеров памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров памяти всех предыдущих разрядов и вторыми входами элемента И-НЕ предыдущего разряда, выходы элементов И-НЕ первого и второго разрядов с двумя входами коммутационных триггеров соответственно второго и третьего разрядов, выход элемента И-НЕ третьего разряда соединен с единичным входом коммутационного триггера четвертого разряда, единичный выход которого соединен с единичным входом триггера памяти этого же разряда, с нулевыми входами триггеров памяти и коммутационных триггеров всех предыдущих разрядов и со вторым входом элемента ИНЕ третьего разряда, а нулевой выход коммутационного триггера четвертого разряда с нулевы.ми входами всех триггеров памяти и нулевыми входами коммутационных триггеров предыдущих разрядов 2.

Недостатком описанного устройства также является сравнительно низкая надежность.

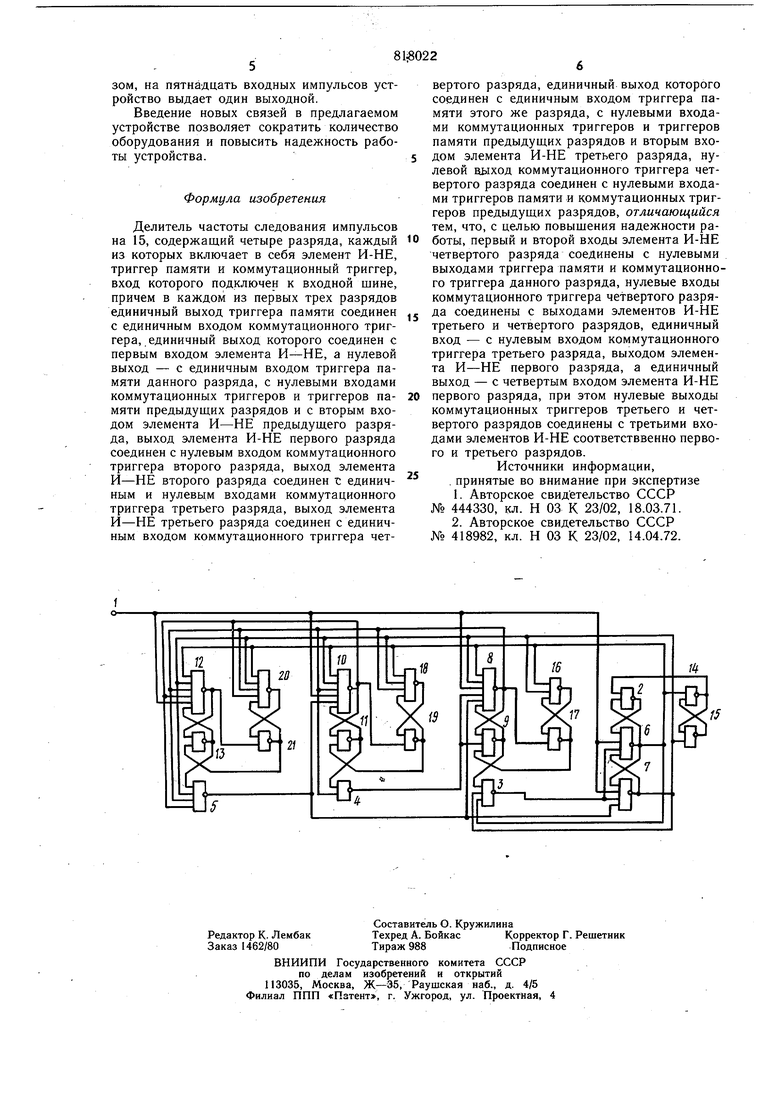

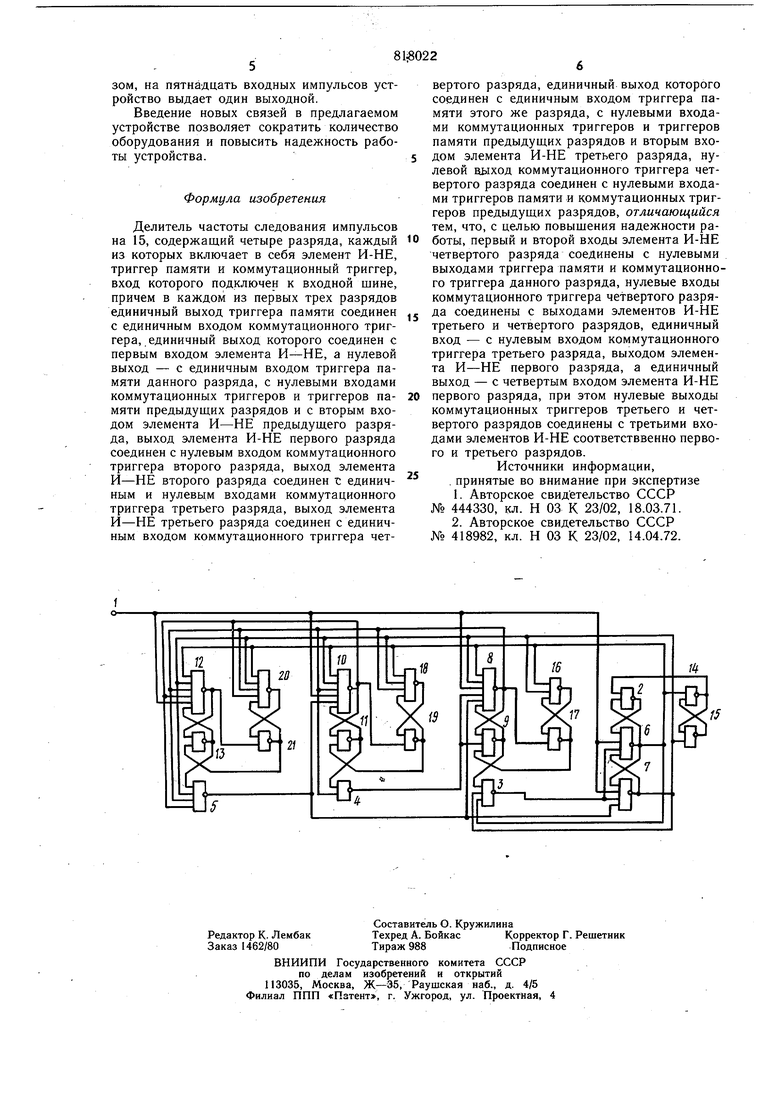

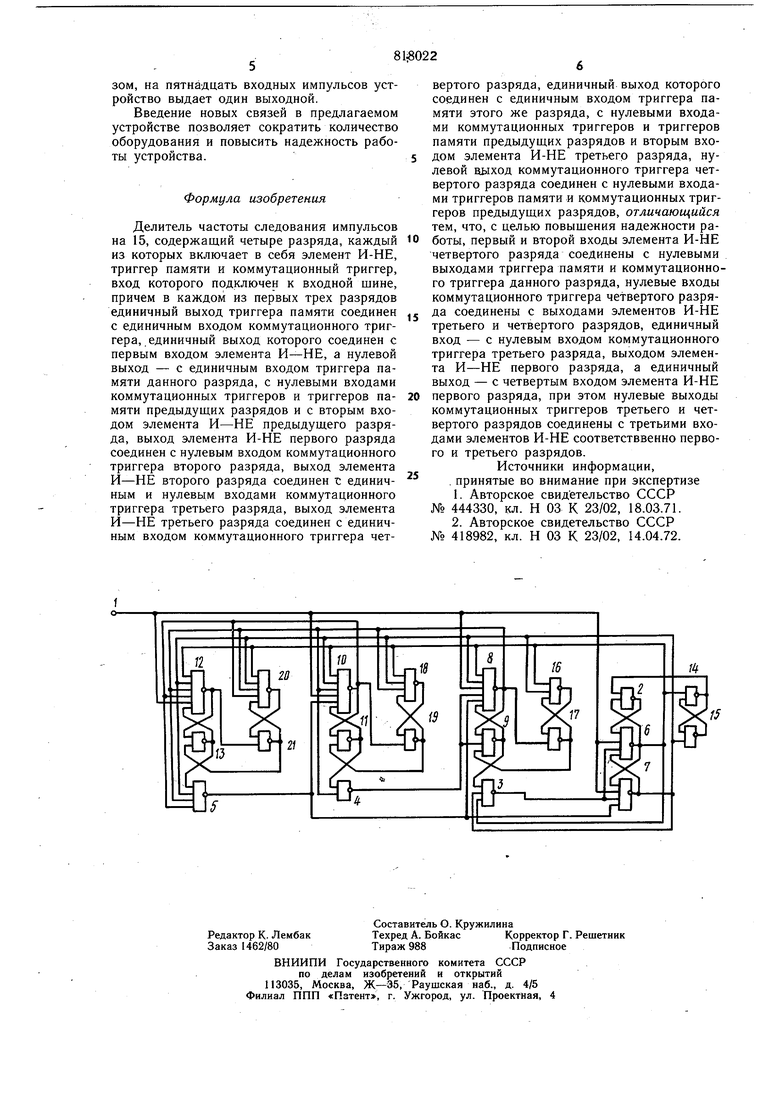

Цель изобретения - повышение надежности работы устройства. Для достижения этой цели в делитель частоты следования импульсов на 15, содержащий четыре разряда, каждый из которых включает в себя элемент И-НЕ, триггер памяти и коммутационный триггер, вход которого подключен к входной шине, причем в каждом из первых трех разрядов единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный выход которого соединен с первым входом элемента И-НЕ, а нулевой выход - с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров памяти предыдущих разрядов и с вторым входом элемента И-НЕ предыдущего разряда, выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго разряда, выход элемента И-НЕ второго разряда соединен с единичным и нулевым входами коммутационного триггера третьего разряда, выход элемента И-НЕ третьего разряда соединен с единичным входом коммутационного триггера четвертого разряда, единичный выход которого соединен с единичным входом триггера памяти этого же разряда, с нулевыми входами коммутационных триггеров и триггеров памяти предыдущих разрядов и вторым входом элемента И-НЕ третьего разряда, нулевой выход коммутационного триггера четвертого разряда соединен с нулевыми входами триггеров памяти и коммутационных триггеров предыдущих разрядов, первый и второй входы элемента И-НЕ четвертого разряда - с нулевыми выходами триггера памяти и коммутационного триггера данного разряда, нулевь1е входы коммутационного триггера четвертого разряда соединены с выходами элементов И-НЕ третьего и четвертого разрядов, единичный вход - с нулевым входом коммутационного триггера третьего разряда, выходом элемента И-НЕ первого разряда, а единичный выход - с четвертым входом элемента И-НЕ первого разряда, при этом нулевые выходы коммутационных триггеров третьего и четвертого разрядов соединены с третьими входами элементов И-НЕ соответственно первого и третьего разрядов. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство содержит шину 1 входную, элементы И-НЕ, элементы 6т 13 И-НЕ коммутационных триггеров, элементы 14Ц21 И-НЕ триггеров памяти. Делитель частоты работает следующим образом. В исходном состоянии все триггеры памяти находятся в нулевом состоянии, а входной сигнал, поступающий по щине 1, отсутствует, т.е. равен логическому нулю. В этом случае на выходах элементов 2;5, 15, 17, 19 И 21 - логический нуль, а на выходах остальных элементов И-НЕ - логическая единица, поэтому с приходом первого импульса срабатывает только элемент 12, устанавливая триггер памяти первого разряда в единицу. После окончания входного импульса на выходе элемента 5 появляется логическая единица. С приходом следующего импульса срабатывает элемент 10, устанавливая триггер памяти второго разряда в единицу, а триггер памяти первого разряда - в нуль. Для того чтобы не сработал элемент 12 в момент действия сигнала после того, как триггер памяти первого разряда установится в нуль, а также для обеспечения устойчивой работы элемента 10, его выход соединен со входами элементов 5, 11 и 12. С приходом третьего импульса срабатывает только элемент И-НЕ 12, поскольку на выходах элементов 2, 3 и 5 - логические нули. По окончании действия тактирующего импульса на выходе элемента 5 появляется логическая единица, а поскольку и триггер памяти второго разряда находится в единичном состоянии, то на выходе элемента И-НЕ 4 стоит логическая единица. Таким образом, с приходом четвертого импульса срабатывает элемент 8, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти младших разрядов в нулевое. Наличие связи с выхода элемента 8 на входы элементов 4, 5, 10 и 12 опять препятствует неправильной работе делителя. Аналогично элемент 7 сработает лищь при наличии на выходах элементов 3 и 5 логической единицы. Это значит, что триггеры памяти первых трех разрядов находятся в единице. Сигнал, равный логическому нулю, появившийся на выходе элемента 7, устанавливает триггер памяти четвертого разряда в единицу, а триггеры памяти младших разрядов - в нуль. После окончания импульса на выходе элемента 2 появляется сигнал, равный логической единице, а на выходах элементов 3, 4 и 5 установится сигнал, равный логическому нулю. Очевидно, что элементы 9, 4 и 11 работают как полусумматор, складывая единицы переноса на разряд с состоянием триггера памяти разряда, причем сигнал на выходах элементов И 2-5 изменяется лишь после окончания действия импульса. Далее счет продолжается аналогичным образом до тех пор, пока с приходом четырнадцатого импульса в делителе не устанавливается код 1110, при этом на выходе элемента 3 появляется логическая единица. С приходом пятнадцатого импульса срабатывает элемент 6, устанавливая делитель в исходное состояние. Наличие связи с выхода логического элемента 6 на входы элементов 3, 5, 8, 10 и 12 опять препятствует неправильной работе делителя. Таким образом, на пятнадцать входных импульсов устройство выдает один выходной. Введение новых связей в предлагаемом устройстве позволяет сократить количество оборудования и повысить надежность работы устройства. Формула изобретения Делитель частоты следования импульсов на 15, содержащий четыре разряда, каждый из которых включает в себя элемент И-НЕ, триггер памяти и коммутационный триггер, вход которого подключен к входной шине, причем в каждом из первых трех разрядов единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный выход которого соединен с первым входом элемента И-НЕ, а нулевой выход - с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров памяти предыдущих разрядов и с вторым входом элемента И-НЕ предыдущего разряда, выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго разряда, выход элемента И-НЕ второго разряда соединен t единичным и нулевым входами коммутационного триггера третьего разряда, выход элемента И-НЕ третьего разряда соединен с единичным входом коммутационного триггера четвертого разряда, единичный выход которого соединен с единичным входом триггера памяти этого же разряда, с нулевыми входами коммутационных триггеров и триггеров памяти предыдущих разрядов и вторым входом элемента И-НЕ третьего разряда, нулевой выход коммутационного триггера четвертого разряда соединен с нулевыми входами триггеров памяти и коммутационных триггеров предыдущих разрядов, отличающийся тем, что, с целью повышения надежности работы, первый и второй входы элемента И-НЕ четвертого разряда соединены с нулевыми выходами триггера памяти и коммутационного триггера данного разряда, нулевые входы коммутационного триггера четвертого разряда соединены с выходами элементов И-НЕ третьего и четвертого разрядов, единичный вход - с нулевым входом коммутационного триггера третьего разряда, выходом элемента И-НЕ первого разряда, а единичный выход - с четвертым входом элемента И-НЕ первого разряда, при этом нулевые выходы коммутационных триггеров третьего и четвертого разрядов соединены с третьими входами элементов И-НЕ соответстввенно первого и третьего разрядов. Источники информации, . принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 444330, кл. Н 03 К 23/02, 18.03.71. 2.Авторское свидетельство СССР № 418982, кл. Н 03 К 23/02, 14.04.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Делитель частоты импульсов на двенадцать | 1977 |

|

SU733110A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты импульсов | 1979 |

|

SU843247A2 |

Авторы

Даты

1981-03-30—Публикация

1979-05-25—Подача