ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для формирования теста оперативной памяти | 1986 |

|

SU1425789A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство управления полупроводниковой памятью | 1986 |

|

SU1410098A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке оперативной памяти с встроенными средствами диагностирования в интегральном исполнении. Целью изобретения является повышение достоверности диагностического контроля. Устройство содержит формирователь теста, генератор импульсов, блок сравнения, выходы которого подключены к информационным входам формирователя распределения ошибок, выходы которого соединены с входами блока памяти распределения ошибок, формирователи адреса и данных, управляемые инверторы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. При тестировании в блоке памяти распределения ошибок фиксируется сводная карта ошибок оперативной памяти, которая затем выводится в процессор для обработки. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано при разработке оперативной памяти с встроенными средствами диагностирования в интегральном исполнении.

Целью изобретения является повышение достоверности диагностического контроля.

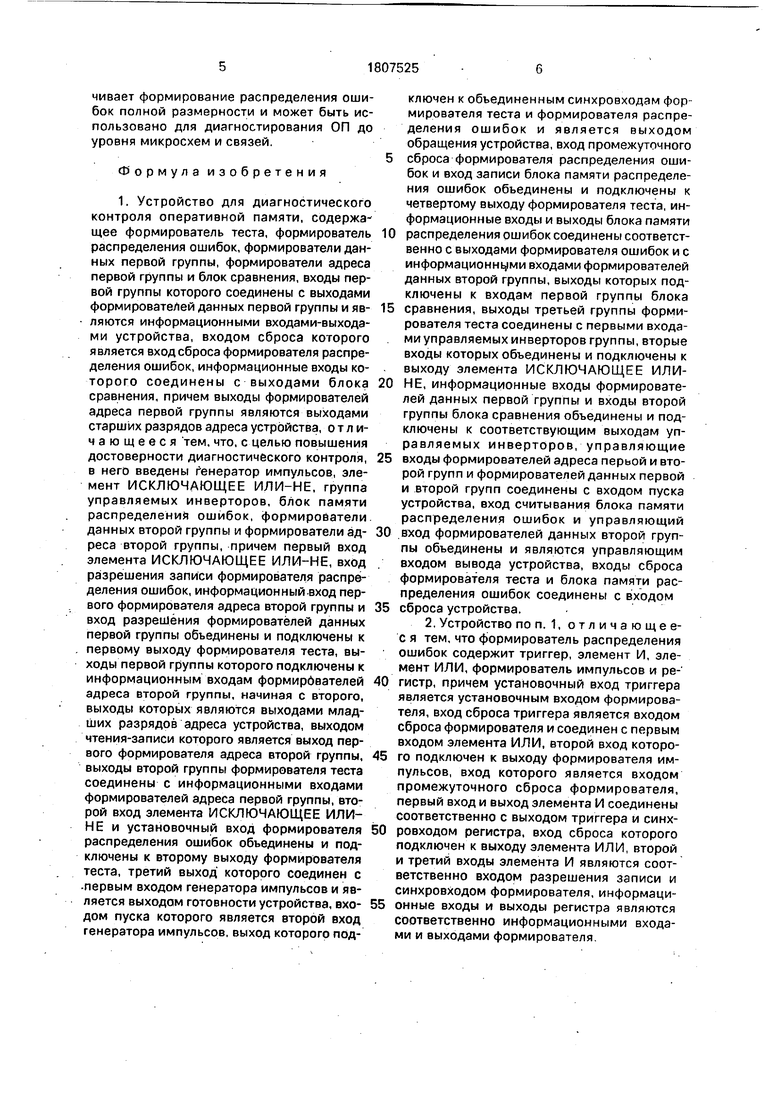

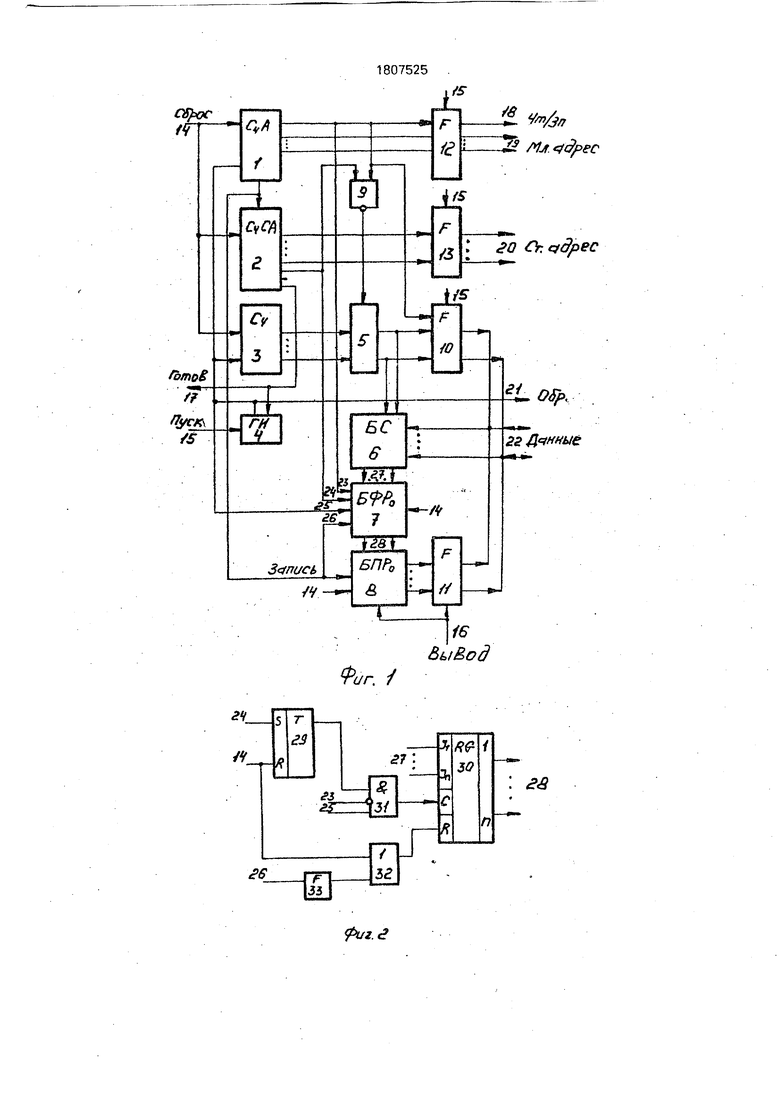

На фиг. 1 изображена схема устройства для диагностического контроля оперативной памяти; на фиг. 2 - блок фиксации распределения ошибок.

Устройство содержит счетчик 1 младших адресов, счетчик 2 старших адресов, счетчик 3 формирователя теста, генератор 4 импульсов, группу управляемых инверторов 5. блок сравнения б, блок 7 формирования распределения ошибок, блок 8 памяти распределения ошибок, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ--НЕ 9 шинные формирователи

данных 10, 11 и адреса 12, 13, вход 14 сигнала начальной установки, вход 15 сигнала запуска, вход 16 сигнала чтения распределения ошибок, выход 17 сигнала готовности устройства, выход 18 сигнала чтение - запись в накопитель, выходы 19 младших адресов, выходы 20 старших адресов, выход 21 сигнала обращения к накопителю, выходы- входы 22 данных. Блоки 1-3 образуют формирователь теста.

Блок 7 формирования распределения ошибок по входу 23 подключен к выходу младшего разряда счетчика 1 младших адресов, по входу 24 к выходу N-2 разряда счетчика 2 старших адресов, по входу 25 - к выходу генератора импульсов 4, по входу 26 - к выходу сигнала переполнения счетчика 1 младших адресов, по входам 27 - к выходам блока сравнения 6 по выходам 28 - к информационным входам блока 8 памяти распределения ошибок.

00

5

СП

ю

СП

Блок 7 формирователя распределения ошибок (фиг. 2) содержит триггер 29, регистр 30, состоящий из l-триггеров, элемент И 31, элемент ИЛИ 32, формирователь импульсов 33.

Счетчик формирователя теста 3 используется для генерации псевдослучайной тестовой последовательности данных и может быть реализован известными способами.

Блок 8 памяти распределения ошибок представляет собой стек и может быть выполнен по схеме.

Устройство работает следующим образом.

После включения питания перед началом работы в устройство подается сигнал начальной установки 14, который устанавливает счетчики 1 и 2 адреса, в нулевое состояние, обнуляет счечтик 3 формирования теста, устанавливает триггер 29 в состояние Лог. О, обнуляет регистр 30 и блок 8 памяти распределения ошибок, В режиме диагностирования на вход 15 устройства поступает сигнал запуска, который разрешает работу генератора импульсов 4 и служит сигналом выборки формирователей адреса 12,13 и данных 10.

Генератор импульсов 4 обеспечивает переключение счетчика 1 младших адресов, младший разряд которого является сигналом чтение - запись для оперативной памяти (ОП). Перебор остальных адресов этого счетчика позволяет тестировать первую линейную ОП. Генератор импульсов 4 обеспечивает также перебор данных в счетчике 3 формирователя теста, который формирует псевдослучайную последовательность кодов для реализации моделированного алгоритма теста Марш для Многоразрядной памяти. Данные со сметчика 3 формирователя теста через управляемые инверторы 5 поступают на шинный формирователь дан- - ных 10, который осуществляет передачу на шину данных ЗУ 22. Управление управляемыми инверторами 5 осуществляется с помощью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ в зависимости от режима Чтение или Запись и от N-2 разряда счетчика 2 старших разрядов, который характеризует четность порядкового номера цикла прохождения теста. Младший разряд счетчика 1 младших разрядов, характеризующий режим чтение - запись осуществляет блокировку сигнала выборки формирователя данных 10 в режиме ЧТЕНИЕ. Генератор импульсов 4 формирует также сигнал обращения к ЗУ 21.

Таким образом по каждому адресу линейки ОП в зависимости от состояния разрядов счетчика младших адресов и сигнала переполнения счетчика старших разрядов

устройство диагностики инициирует два обращения: чтение прямого (инверсного) кода .и запись инверсного (прямого) кода. В циклах чтения данные из ОП по двунаправленным шинам 22 поступают в блок сравнения 6, где сравниваются с эталоном, формируемым на выходах управляемых инверторов счетчиком 3 формирователя теста. Результирующий вектор сравнения 27 поступает

на блок 7 фиксации распределения ошибок, который работает следующим образом.

Основой блока 7 является диагностический регистр 30, каждый разряд которого i представляет 1-триггер,, стробируемый сиг5 налом 25 от генератора импульсов 4 при наличии признака действительности данных с выхода триггера 29 и признака цикла чтения с выхода 23. Необходимость введения триггера 29 обуславливается тем, что

0 первоначально в накопителе тестируемой ОП присутствует случайная информация и результаты чтения на первом проходе теста не несут полезной информации. При полном переборе всех адресов ОП на N-3

5 выходе счетчика 2 старших адресов появляется сигнал 24, который устанавливает триггер 29 в состояние Лог. 1, что соответствует появлению признака действительности данных, Этот же сигнал 24 из0 ,меняет логическое состояние на одном из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ- НЕ, что приводит к тому, что если при первом проходе мы производили чтение прямого кода и запись инверсного, то при

5 осуществлении второго прохода мы будем

читать инверсный код и записывать прямой,

.По окончании прохода каждой линейки ОП

с выхода переполнения счетчика младших

ёдресов поступает сигнал 26, который запу0 екает формирователь 33 и по заднему фронту сбрасывается содержимое регистра 30, после того как по последнему фронту сигнала 26 оно было переписано в блок памяти распределения ошибок 8. После осуществ5 ления четырех проходов теста в старшем разряде счетчика старших разрядов 2 появится сигнал готовности 17. который одновременно отключит генератор импульсов 4 и сообщит процессору о завершении диаг0 ностирования. Для передачи в процессор по окончании тестирования хранящейся в блоке 8 памяти распределения ошибок матрицы распределения Ошибок необходимо подать активный сигнал Вывод 16 столько

5 раз сколько линеек имеет ОП, Сигнал Вывод будет сигналом чтения из блока памяти распределения ошибок и сигналом выборки шинного формирователя данных 4.

Таким образом, предложенное устройство для диагностического контроля оСеспечивает формирование распределения ошибок полной размерности и может быть использовано для диагностирования ОП до уровня микросхем и связей.

Формула изобретения

Фиг. /

гз

ft

Ј3

16

ВыВод

27

Ј

ЯР 50

:

| Запоминающее устройство с тестовым самоконтролем | 1986 |

|

SU1396160A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с обнаружением отказавших блоков | 1980 |

|

SU903974A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-04-07—Публикация

1991-02-25—Подача