. (5) МАТРИЧНЫЙ НАКОПИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Матричный накопитель для полупроводникового запоминающего устройства | 1978 |

|

SU729636A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1429167A1 |

| Ячейка памяти | 1976 |

|

SU681455A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1405575A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

1

Изобретение относится к вычислительной технике и предназначено для использования в качестве устройства памяти оперативных запоминающий устройств микро-ЭВМ и микропроцессоров, в частности, с системой автодиагностики.

Известен матричный накопитель МДП запоминающего устройства с произвольной выборкой информации, выполненный на однотранзисторных запоминающих элементах ( МОП ЗУПВ емкостью 409б бит на однотранзисторных запоминающих элементах, в котором первые выводы запоминающих конденсаторов подключены к истокам соответствующих адресных транзисторов а вторые выводы соединены с шиной нулевого потенциала р .

Информация, считанная непосредственно после включения источника питания, соответствует логическому нулю для всех запоминающих элементов матричного накопителя. Это связано

с тем, что в исходном состоянии (непосредственно после включения питания) запоминающие конденсаторы разряжены. Поэтому недостатком известного устройства является ограниченная область применения, обусловленная невозможностью считывания заранее запрограммированной информации, т.е. матричный накопитель может быть использован только в oneт

ративных запоминающих устройствах, где считыванию информации предшествует цикл обязательной ее записи.

Наиболее близким по технической сущности к предлагаемому является матричный накопитель МДП-запоминающего устройства с произвольной йыборкой динамического типа, выполненный на однотранзисторных запоминающих элементах 2 .

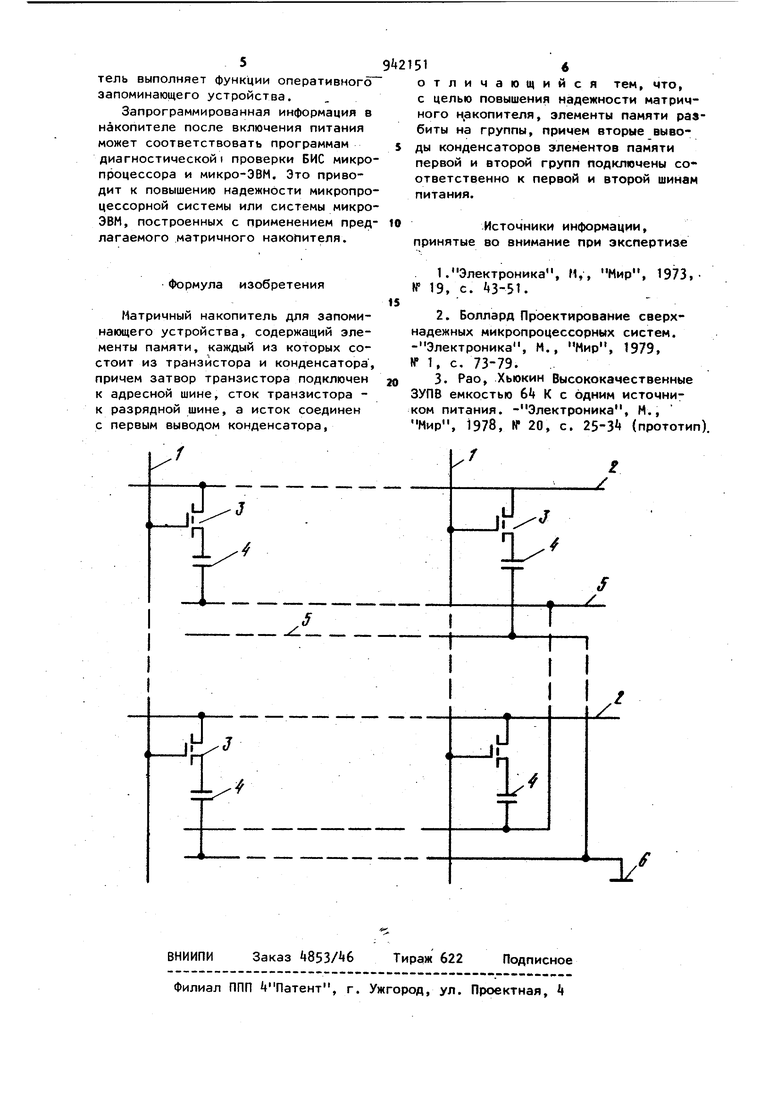

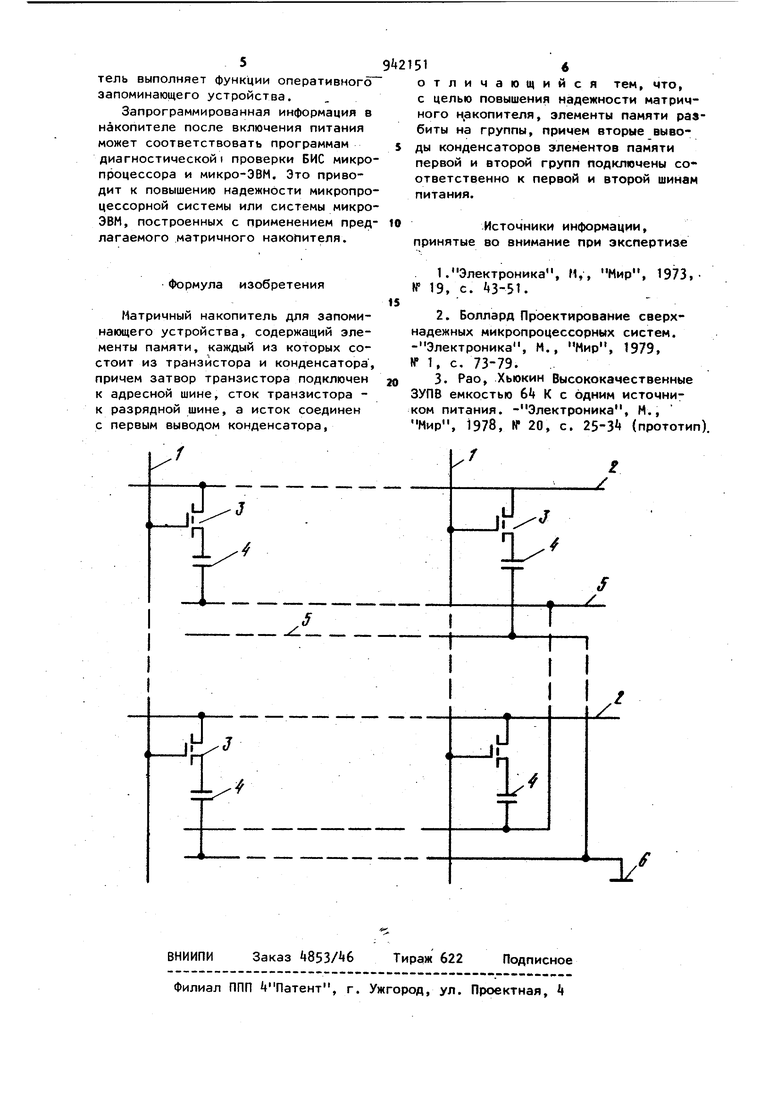

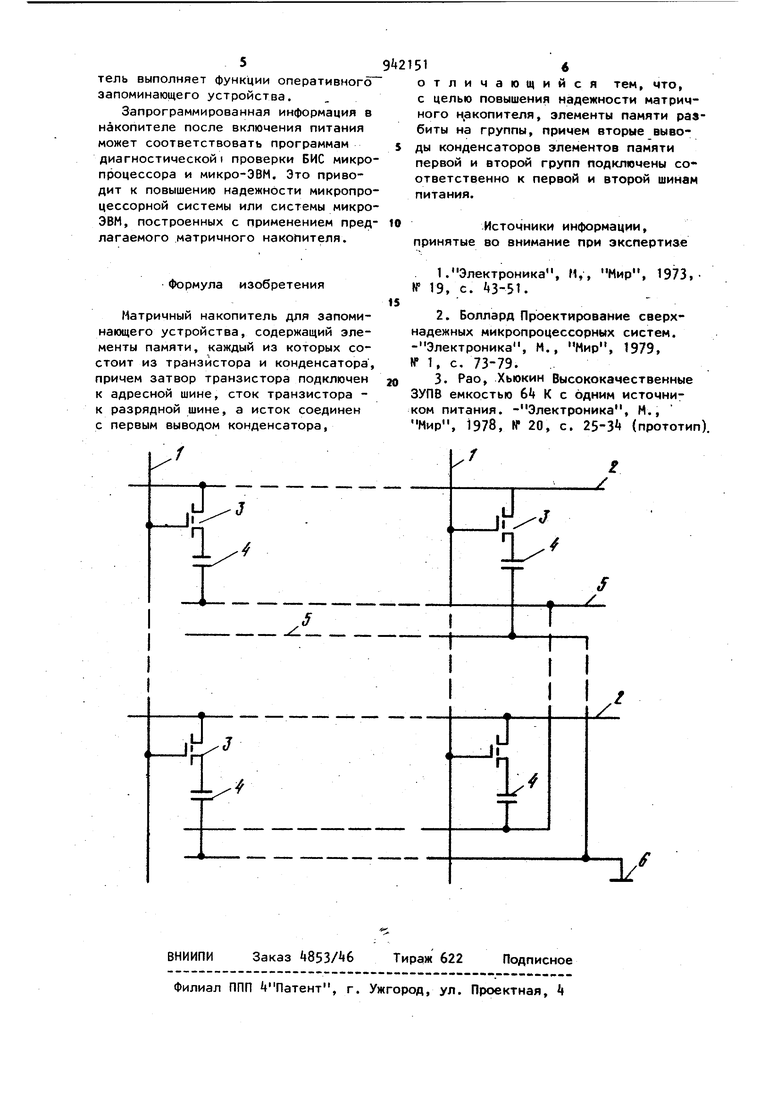

Матричный накопитель содержит на каждом пересечении адресных и разрядных шин адресный транзистор и запоминающий конденсатор, при этом стоки адресных транзисторов соединены с соответствующими разрядными шинами, истоки - с первыми выводами запоминающих конденсаторов, затворыс соответствующими адресными шинами а вторые выводы запоминающих конденсаторов подключены к шине питания. Конструктивное исполнение матричного накопителя также предполагает цикл предварительной записи информации перед ее считыванием, так как при считывании информации непосредственно после включения источника питания будет считана логическая единица со всех запоминающих элементов накопителя. Поэтому матричный накопитель может использоваться только в оперативных запоминающих устройствах 3 }, Недостатком известного устройства является низкая надежность при использовании матричного накопителя в ЗУ. Цель изобретения - повышение надежности матричного накопителя. Поставленная цель достигается тем, что матричный накопитель для запоминающего устройства, содержащий элементы памяти, каждый из которых состоит из транзистора и конденсатора, причем затвор транзистора подключен к адресной шине, сток транзистора - к разрядной шине, а исток соединен с первым выводом конденсато ра, элементы памяти разбиты на группы, причем вторые выводы конденсаторов элементов памяти первой и второй групп подключены соответственно к первой и второй шинам питания. На чертеже изображен матричный накопитель МДП-запоминающего устройства. В однотранзисторных ячейках памяти, находящихся на пересечении адресных 1 и разрядных 2 шин, стоки адресных транзисторов 3 соединены с соответствующими разрядными шинами 2 истоки их - с первыми выводами запоминающих конденсаторов 4. а затворы с соответствующими адресными шинами 1. Вторые выводы запоминающих конден саторов k ячеек, в которых после вкл чения питания олжна устанавливаться информация логической единицы, подключены к шине 5 питания, и тех ячеек, в которых после включения питания должна быть установлена информация логического нуля,- к шине 6 нулевого потенциала. Непосредственно после включения источника питания на первых выводах запоминающих конденсаторов 4 первой группы (вторые выводы конденсаторов k подключены к шине 5 питания уста-навливается высокий уровень напряжения (логическая единица . На первых выводах запоминающих конденсаторов k второй группы (вторые выводы подключены к шине 6 нулевого потенциала сохраняется низкий уровень напряжения (логический нуль). При считывании информации на выбранную адресную шину 1 подается высокий уровень напряжения и соответствующие адресные транзисторы 3 открываются, подключая первые выводы запоминающих конденсаторов k к разрядным шинам матричного накопителя 2. Если на первом выводе запоминающего конденсатора 4 установлен высокий уровень напряжения, потенциал на разрядной шине 2 получает положительное приращение и считывается информация, соответствующая логической единице. Если на первом выводе запоминающего конденсатора 4 установлен низкий уровень напряжения, потенциал на разрядной шине 2 получает отрицательное приращение и считывается информация, соответствующая логическому нулю. Таким образом, подключение второго вывода запоминающего конденсатора 4 к шине 1 питания обеспечивает непосредственно после включения питания считывание с данной ячейки информации логической единицы, а подключение второго вывода конденсатора 4 к шине нулевого потенциала 6 считывание с данной ячейки информации логического нуля. Следовательно, при соответствующем подключении вторых выводов запоминающих конденсаторов 4 к шине 5 питания и к шине 6 нулевого потенциала матричный накопитель МДП-запоминающего устройства приобретает качественно новые функции - функции по;Sстоянного запоминающего устройства с заранее запрограммированной информацией. Роль постоянно запоминающего устройства сохраняется до тех пор, пока в запоминающие ячейки не запишется новая информация. После записи новой информации матричный накопитель выполняет функции оперативного запоминающего устройства.

Запрограммированная информация в накопителе после включения питания может соответствовать программам диагностической проверки БИС микропроцессора и микро-ЭВМ. Это приводит к повышению надежности микропроцессорной системы или системы микроЭВМ, построенных с применением предлагаемого матричного накопителя.

Формула изобретения

Матричный накопитель для запоминающего устройства, содержащий элементы памяти, каждый из которых состоит из транзистора и конденсатора, причем затвор транзистора подключен к адресной шине, сток транзистора к разрядной шине, а исток соединен с первым выводом конденсатора,

g tzisi«

отличающийся тем, что, с целью повышения надежности матричного н,акопителя, элементы памяти разбиты на группы, причем вторые выводы конденсаторов элементов памяти первой и второй групп подключены соответственно к первой и второй шинан питания.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-07-07—Публикация

1980-11-05—Подача