(Б) УСТРОЙСТВО ДЕЛЬТА-МОДУЛЯЦИИ С ЦИФРОВОЙ

АДАПТАЦИЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дельта-модуляции | 1984 |

|

SU1241479A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

| Универсальный дельта-кодек | 1982 |

|

SU1078612A1 |

| Цифровой фильтр с дельта-модуляцией | 1987 |

|

SU1418908A1 |

| Цифровой фильтр с дельта-модуляцией | 1985 |

|

SU1347188A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

1

Изобретение относится к области электросвязи и может быть использовано при разработке цифровых передатчиков сигналов.

Известно устройство, содержащее дельта-модулятор, адаптивную логику, счетчик, делитель частоты, два генератора импульсов l.

Недостатком известного устройст ва является его сложность.

Известно устройство, содержащее высокочастотный дельта-модулятор, сигнальный вход которого соединен с шиной входного сигнала, первый генератор тактовых импульсов и второй генератор тактовых импульсов, выход которого соединен с счетным входом триггера, первый выход которого соединен с входом логического блока 2.

Недостатком этого устройства является его сложность и, следоьательно, его низкая надежность.

Цель изобретения - повышение надежности.

Поставленная цель достигается тем, что в устройство дельта-модуляции, содержащее высокочастотный дельта-модулятор, сигнальный аход которого соединен с шиной входного сигнала, первый генератор тактовых импульсов и второй генератор тактовых импульсов, выход которого соединен с счетным входом триггера, первый выход которого соединен с входом логического блока, введены делитель частоты импульсов, реверсивный счетчик и два элемента И, причем выходы вы15сокочастотного дельта-модулятора соединены с первыми входами элементов И, вторые входы которых соединены с соответствующими выходами триггера, информаципчный вход которого соединен

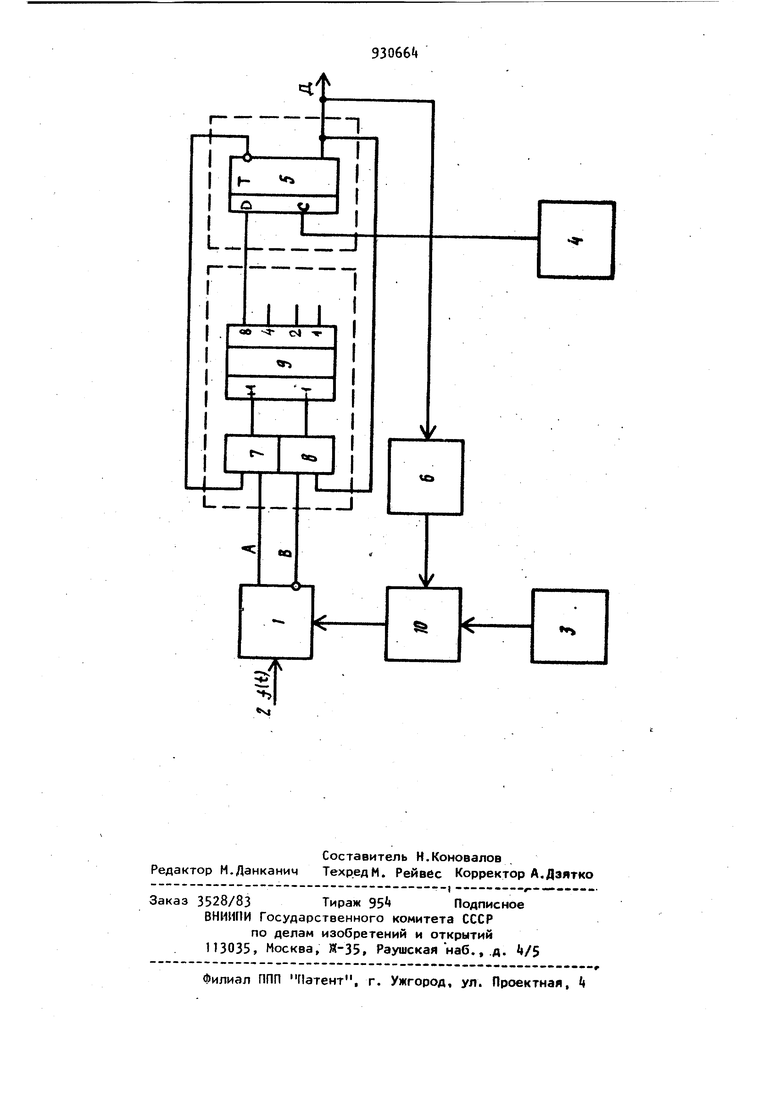

30 с выходом реверсивного счетчика, входы которого соединены с выходами соответствующих элементов И, выход логического блока соединен с управлякхцим ВХОДОМ управляемого делителя, вход которого соединен с выходом первого интегратора импульсов , а выход - с синхронизирующим входом высокочастотного дельта-модулятора. На чертеже представлены блок-схема ус тоойства дельта-модуляции с циф ровой адаптацией. Устройство содержит высокочастотн дельта-модулятор (ВДМ)1, сигналь+ный вход которого соединен с шиной 2 вхо ного сигнала, генератор 3 тактовых и пульсов и генератор Ц тактовых импульсов, выход которого соединен с счетным входом триггера 5 первый выход которого соединен с входом логического блока 6, выходы модулятора 1 соединены с первыми входами элемен тов И: 7 и oi вторые входы которых со единены с соответствующими выходами триггера F, информационный вход которого соединен с выходом реверсивного счетчика 9, входы .которого соединены с соответствующими выходами элементов И 7 и 8, выход блока 6 соединен с соответствующими выходами элементов И 7 и 8, выход блока 6 соединен с управляющим входом управляемого делителя 10, вход которого соединен с выходом генератора 3, а выход с синхрюнизирующим входом модулятора 1 . Устройство дельта-модулятора с цифровой адаптацией работает следую щим образом. Входной аналоговый сигнал f(t), поступающий на шину 2 подается на дельта-модулятор 1, работающий на высокой тактовой частоте, что обеспечивает высокое качество анало -де та преобразования. На выходе ВДМ 1 имеются две цифровые последовательности, представляющие собой прямой и инверсный дельта-сигналы, которые поступают через элементы 7 и 8 соот ветственно, на входы реверсивного счетчика 9. Причем, если последний разряд,подключенный к тактируемому триггеру 5. в момент тактирования находится в положении 1 - открыва ется элемент Вив счетчике 9 суммируются импульсы, в другом случае открывается элемент 7 и счетчик 9 вычитает импульсы. Тактирование триггера 5 осуществляется на частоте F/./OT низкочастотного генератора . Блок 6 логики управляет в зависимости от сигнала на выходе три|- гера 5 коэффициентом деления делителя 10, что позволяет производить цифровое компандирование. Таким образом, предлагаемое устройство, сохраняя параметры известного, значительно проще его. Формула изобретения Устройство дельта-модуляции с цифровой адаптацией, содержащее высокочастотный дельта-модулятор, си1- нальный вход которого соединен с шиной входного сигнала, первый генератор тактовых импульсов и второй генератор тактовых импульсов, выход которого соединен с счетным входом триггера , первый выход которого соединен с входом логического блока, отдирающееся тем, что,с целью повышения надежности, в него введены делитель частоты импульсов, реверсивный счетчик и два элемента И, причем выходы высокочастотного дельта-модулятора соединены с первыми входами элементов И, вторые входы которых соединены с соответствующими выходами триггера, информационный вход которого соединен с выходом реверсивного счетчика, входы которого соединены с выходами соответствующих элементов И, выход логического блока соединен с управляющим входом управляемого делителя, вход которого соединен с выходом первого генератора импульсов, а выход с синхронизирующим входом высокочастотного дельта-модулятора. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3699566, кл.Н 03 К 13/22, 1972. 2.Патент США № 3652957, кл. Н 03 К 13/22, 1972,

Авторы

Даты

1982-05-23—Публикация

1980-09-24—Подача