Изобретение относится к вычислиельной технике. Известен распределитель импульсов, содержащий триггеровый регистр, вспомогательные триггеры, элементы И дешифратор tl1. Недостатком известного устройства является большой объем оборудования и малое быстродействие. Наиболее близким к предлагаемому является распределитель импульсов содержащий триггерный регистр, два вспомогательных триггера, дешифратор два входных элемента И-НЕ, элемент И t2J. Недостатком известного устройства является большой объем оборудования и недостаточное быстродействие. Цель изобретения - повышение быст родействия и упрощение устройства. Поставленная цель достигается тем что в распределитель, содержащий три герный регистр, два вспомогательных триггера, дешифратор, два входных элемента И-НЕ, элемент И, причём управляющие входы входных элементов И-НЕ соединены с первым и вторым входами распределителя, выходы входных элементов И-НЕ соединены с единичными входами вспомогательных триггеров и с входами элемента И, выход которого соединен с йулевыми входами триггеров регистра, единичный выход первого вспомогательного триггера соединен с первым входом дешифратора, второй вход которого соединен с единичным.выходом второго вспомога тельного триггера, третий вход дешифратора соединен с третим входов распределителя, первый, второй и третий выходы дешифратора соединены с единичными входами соответственно первого, второго и третьего триггеров регистра, четвертый выход дешифратора соединен с нулевым входом второго триггера регистра, пятый выход дешифратора соединен с нулевыми входами первого и третьего Триггеров регистpa и первого вспомогательного триггера, шестой и седьмой выходы дешифратора соединены с единичными входами соответственно второго и третьего триггеров регистра, восьмой выход де шифратора соединен с нулевыми входами второго и третьего триггеров регистра и второго вспомогательного триггера , дополнительно введены элемент НЕ и дополнительные элементы Й-НЕ, причем вторые входы входных элементов И-НЕ через элемент .НЕ соединены с третьим входом распределите ля, первый и второй входы первого дополнительного элемента И-НЕ соединены соответственно с первым выходом дешифратора и с единичным выходом первого триггера регистра, а выход первого дополнительного элемента И-Н соединен с четвертым входом дешифрато-2о

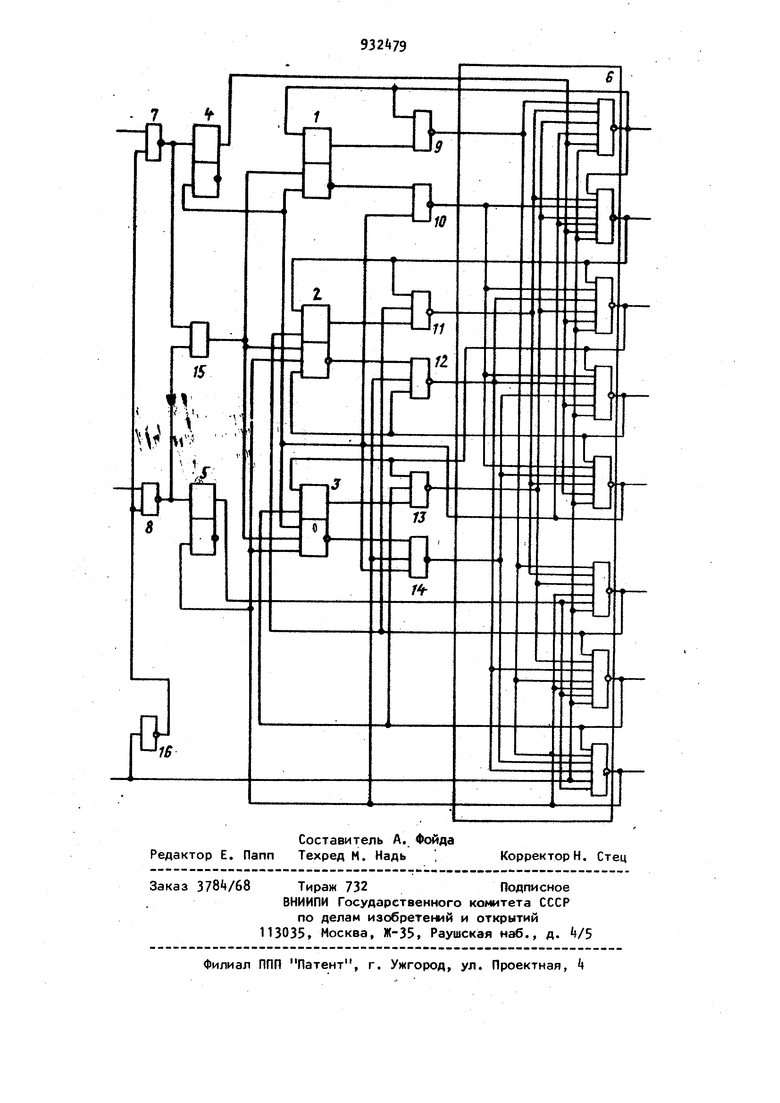

ра, первый вход второго дополнительного элемента И-НЕ соединен с нулевым выходом первого триггера регистра, а выход - с пятым входом дешифратора, пятый выход которого соединен с вторы входами второго и шестого дополнительных элементов И-НЕ, первый, второй и третий входы третьего дополнительного элемента И-НЕ соединены соответственно с вторым и шестым выходами деи1ифратора и с единичным (выходом второго триггера регистра, а выход с шестым входом дешифратора, восьмой выход которого соединен с первыми входами шестого и четвертого дополнительных элементов И-НЕ, второй и третий входы четвертого дополнительного элемента И-НЕ соединены соответственно с четвертым выходом дешифратора и с нулевым выходом второго триггера регист ра, а выход - седьмым входом дешифратора, первый, второй и третий входы пятого дополнительного элемента .И-НЕ соединены соответственно с единичным выходом третьего триггера регистра и третьего и седьмого выходов дешифратора, а выход - восьмым входом дешифратора, третий вход шестого допол нательного элемента И-НЕ соединен с нулевым выходом третьего триггера регистра, а выход - девятым входом дешифратора . На чертеже приведена блок-схема распределителя импульсов. Распределитель содержит три герный регистр, состоящий из трех триггеров 1-3, два вспомогательных триггера и 5, дешифратор 6 на восьми элемен9

держки на срабатывание на выходе его.появляется низкий потенциал, который поступает на входы второго элемента И-НЕ дешифратора 6, и элемента И-НЕ 9, подтверждая действующий в настоящий момент времени отрицательный потенциал, а также на единичный вход триггера 1 и устанавливает его в состояние 1, Низкий потенциал с нулевого выхода триггера 1 поступает на вход элемента И-НЕ 10 и на его выходе через время, равное задержке на его срабатывание, появляется высокий потенциал.

В следующий момент на третий вход поступает второй положительный импульс и на выходе второго элемента И-НЕ дешифратора 6 появляется низкий потенциал, который поступает на 94 тах И-НЕ, два входных элемента ИгНЕ 7 и 8, дополнительные элементы И-НЕ 9 1, элемент И- 15, элемент НЕ 16. Распределитель работает следующим образом. Рассматривая работу распределителя предположим, что в первоначальный момент времени на первый вход поступает Положительный импульс, который стробируется сигналом, поступаю щим с выхода элемента НЕ 16 и устанавливает триггер k в единичное со стояние и, пройдя через элемент И 15, устанавливает триггеры 1-3 в нулевое состояние. I В следующий момент на третий вход приходит положительный импульс и так как на всех входах первого элемента И-НЕ дешифратора 6 действуют положительные потенциалы, то через время завходы третьего элемента И-НЕ дешифратора 6 и элемента И-НЕ 11, поддерживая их состояние и на единичный вход триггера 2, устанавливая его в состояние 1. После окончания действия положительного импульса на третьем входе через время, равное задержке на срабатывание на выходе второго элемента И-НЕ дешифратора 6 появляется высокий потенциал, а затем низкий потенциал на выходе элемента И-НЕ 11. Третий импульс, проходящий на третий вход аналогичным образом, вызывает на выходе третьего элемента И-НЕ дешифратора 6 отрицательный импульс, который блокирует соответствующие элементы И-НЕ и переключает триггер 3 в состояние 1, 59 Четвертый импульс, проходящий на третий вход, блокирует соответствующие элементы И-ИЕ и переключает триггер 2 в состояние О. Пятый импульс, проходящий на третий вход, блокирует соответствующие элементы И-НЕ и переключает триггеры 1 , 3 и в состояние О. В следующий момент на второй вход приходит положительный импульс, который переключает триггер 5 в состояние 1 и с приходом трех положительных импульсов на третий вход аналогичным образом вырабатываются на выходах соответствующих элементов отрицательные импульсы. Минимальный период поступления тактовых импульсов на входе распреде лителя равен Т и-НЕ почти в два раза меньше, чем в прототипе, т.е. частота тактовых импульсов выше чем в прототипе. Формула изобретения Распределитель импульсов, содержащий триггерный регистр, два вспомо гательных триггера, дешифратор, два входных элемента И-НЕ, элемент И, причем управляющие входы входных эле ментов И-НЕ соединены с первым и вто рым входами распределителя, выходы входных элементов И-НЕ соединены с единичными входами вспомогательных триггеров и с входами элемента И, выход которого соединен с нулевыми входами триггеров регистра, единичный выход первого вспомогательного триггера соединен с первым входом дешифратора, второй вход которого соединен с единичным выходом второго вспомогательного триггера, третий вход дешифратора соединен с третьим входом распределителя, первый, второ и третий выходы дешифратора соединены с единичными входами соответственно первого, второго и третьего триггеров регистра, четвертый дешифратора соединен с нулевым входом второго триггера регистра, пятый выход дешифратора соединен с нулевыми входами первого и третьего триггеров регистра и первого вспомогател ного триггера, шестой и седьмой выходы дешифратора соединены с единичными входами соответственно второго и третьего триггеров регистра, восьмой выход дешифратора соединен с нулевыми входами второго и третьего 796 триггеров регистра и второго вспомогательного триггера, отличающи и с я тем, что, с целью повышения быстродействия и упрощения распределителя, он дополнительно содержит элемент НЕ и дополнительные элементы И-НЕ, причем вторые входы входных элементов И-НЕ через элемент НЕ соединены с третьим входом распределителя, первый и второй входы первого дополнительного элемента И-НЕ соединены соответственно с первым выходом дешифратора и с единичным выходом первого триггера регистра, а выход первого дополнительного элемента И-НЕ соединен с четвертым входом дешифратора, первый вход второго дополнительного элемента И-НЕ соединен с нулевым выходом первого триггера регистра, а выход - с пятым входом дешифратора, пятый выход которого соединен с вторыми входами второго и шестого дополнительных элементов И-НЕ, первый, второй и третий входы третьего дополнительного элемента И-НЕ соединены соответственно с вторым и шестым выходами дешифратора и с единичным выходом второго триггера регистра, а выход - с шестым входом дешифратора, восьмой выход которого соединен с первыми входами шестого и четвертого дополнительных элементов И-НЕ, второй и третий входы четвертого дополнительного элемента соединены соответственно с четвертым выходом дешифратора и с нулевым выходом второго триггера регистра, а выход - седьмым входом дешифратора, первый, второй и третий входы пятого дополнительного элемента И-НЕ соединены соответственно с единичным выходом третьего триггера регистра и третьего и седьмого выходов дешифратора, а выход- с восьмым входом дешифратора, третий вход шестого дополнительного элемента И-НЕ соединен с нулевым выходом третьего триггера регистра, а выход - девятым входом дешифратора. Источники информации, принятые во внимание при экспертизе 1. Майоров С.А. и Новиков Г.И. Структура ЦВМ, Л., Машиностроение, 970, с. 197, рис. 5-16. 2. Авторское свидетельство СССР № 292153, кл. G 06 F l/flt, 19б9 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Реверсивный преобразователь-распределитель импульсов | 1981 |

|

SU970696A2 |

| Система числового программного управления | 1986 |

|

SU1397879A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Реверсивный преобразователь распределитель импульсов | 1971 |

|

SU663108A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

Авторы

Даты

1982-05-30—Публикация

1973-05-28—Подача