(5 УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Устройство для контроля цифровых узлов | 1977 |

|

SU643876A2 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для диагностирования группы логических узлов | 1987 |

|

SU1520520A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых yзлов, а также интегральных микросхем. Известно устройство для контроля цифровых блоков, содержащее блок вво да, блок памяти, коммутатор, блок сравнения, блок управления, причем первый и второй выходы блока ввода соединены соответственно с первыми входами блока памяти и блока управ ления Q. Недостатком известного устройства является невозможность обнаружения всех ошибок. НаибЛее близким к предлагаемому по технической сущности является устройство для контроля цифровых узлов , содержащее блок ввода, блок Памяти, коммутатор, блок сравнения, блок индикации, блок управления. Первый выход блока ввода соединен с блоком памяти, выход которого подключен к первому входу блока сравнения и первому входу коммутатора, выходами соединенного с внешними контактами контролируемого узла, второй вход коммутатора соединен с выходом регистра настройки. Второй выход блока ввода соединен с входом блока.управления, выходы которого подключены соответственно к управлт щим входамблока ввода, блока памяти, регистра настройки и блоке индикации, соединечного с выходом блока сравнения 2. Такое устройство не позволяет контролировать правильность работы блока сравнения в процессе проверки контролируемого узла. Цель изобретения - повышение дос товерности работы устройства. Поставленная цель достигается тем, что в устройство, содержащее блок ввода, блок памяти, регистр настройки, коммутатор, блок сравнения, блок индикации, блок управления, причем первый выход

ввода подключен к первым входам блока памяти и регистра настройки, второй вход которого подключен к первому выходу блока управления, первый вход которого подключен к второму выходу блока ввода, вход которого подключен к второму выходу блока управления, третий выход которого подключен к второму входу блока памяти, выход которого подключен к первому входу коммутатора, второй вход которого подключен к выходу регистра настройки, третий вход и выход коммутатора подключены соответственно к выходу-входу контролируемого объекта , четвертый выход блока управления подключен к первому входу блока индикации, введены два элемента ИЛИ, элемент запрета, блок разрешения выдачи тестов, содержащий четыре элемента И, два элемента НЕ, два JK-триггера, формирователь стробов, причем входы первого элемента И подключены соответственно к выходу блока сравнения и к первому входу элемента запрета, второй вход которого подключен к выходу второго элемента И, первый вход которого подк.гиочен к пятому выходу блока управления, к входу формирователя стробов и к R-входам первого и второго JК-триггеров, К, Ср, J-входы первого триггера объединены и подключены к выходу первого элемента НЕ, К, Ср, J-входы второго триггера объединены и подключены к выходу второго элемента НЕ, входы первого и второго элементов НЕ подключены соответственно к выходам третьего и четвертого элементов И, первые входы которых объединены и подключены к выходу первого элемента И, вторые входы третьего и четвертого элементов И подключены соответственно к первому и второму выходам формирователя стробов, первый выход которого соединен с первым входом первого элемента ИЛИ, а второй выход - с первым входом второго элемента ИЛИ, выходы первого и второго JK-триггеров подключены соответственно к второму и третьему входам второго элемента И и к второму входу блока управления, кроме того, второй вход первого элемента ИЛИ подключен к выходу блока памяти, а выход - к первому входу блока сравнения, второй вход которого подключен к выходу второго элемента ИЛИ, второй вход

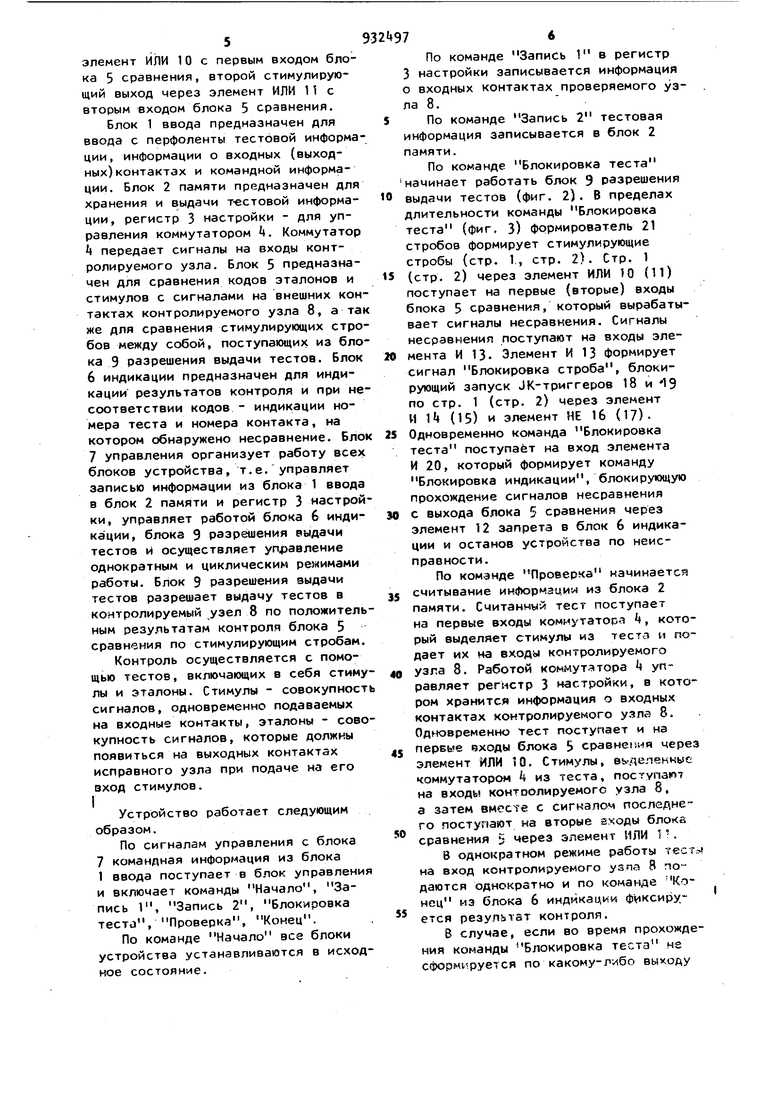

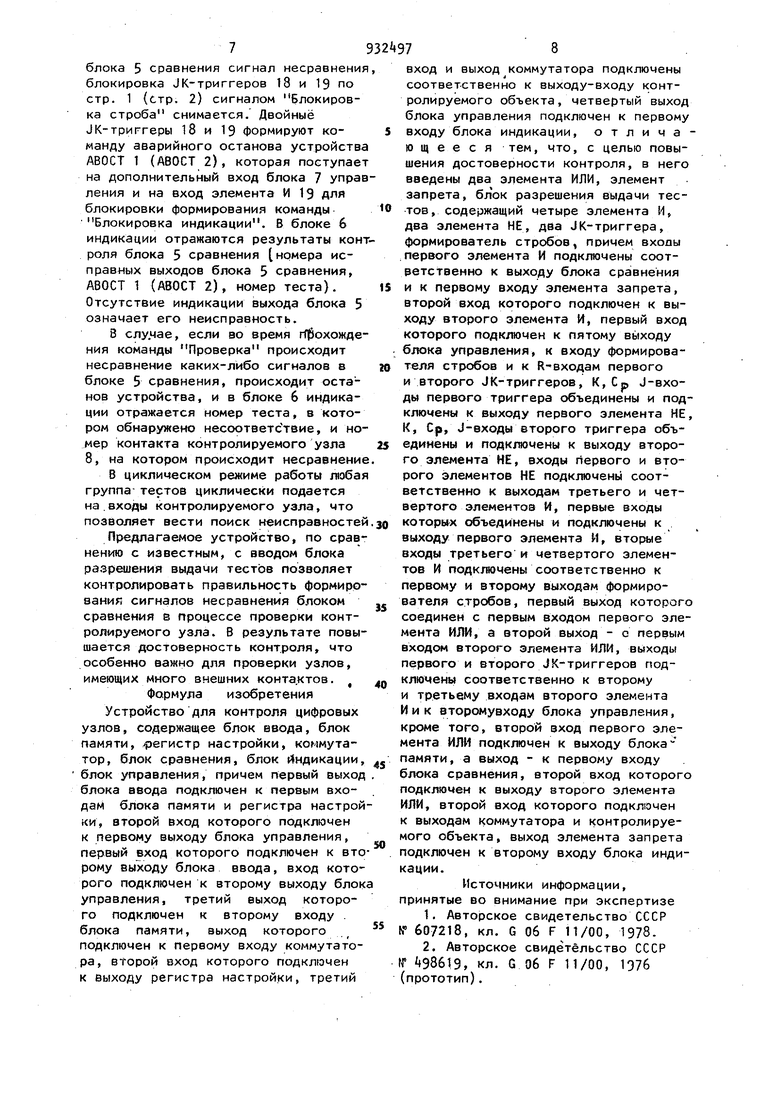

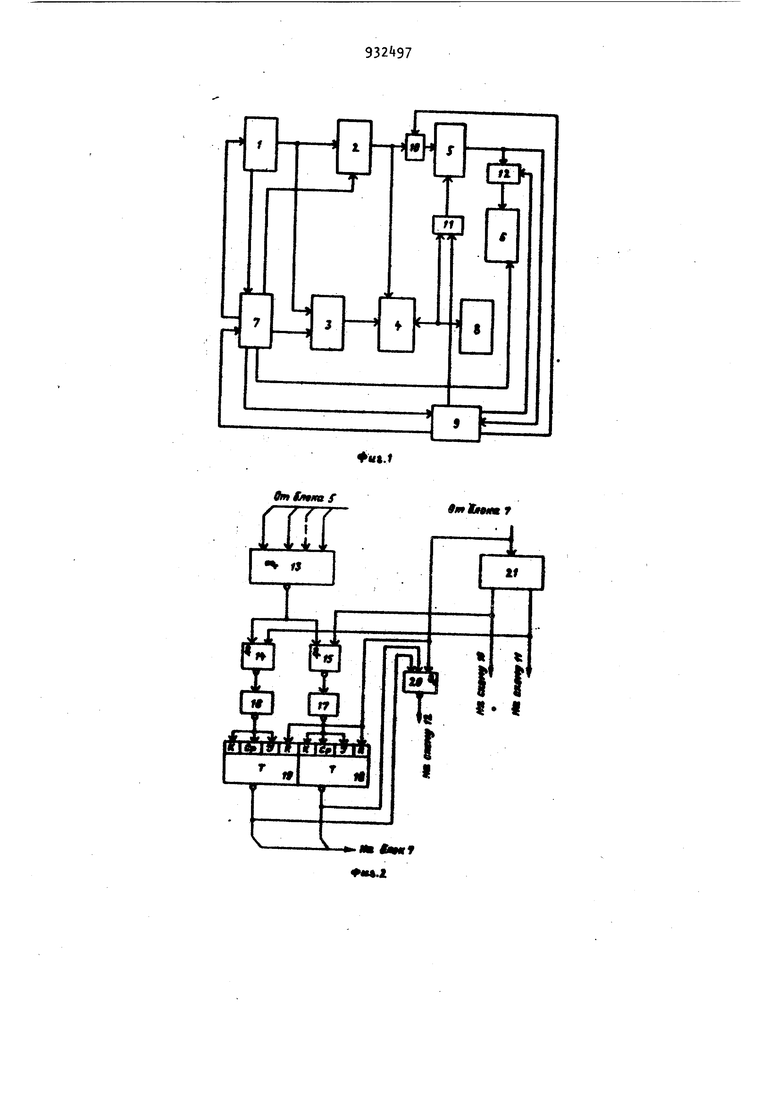

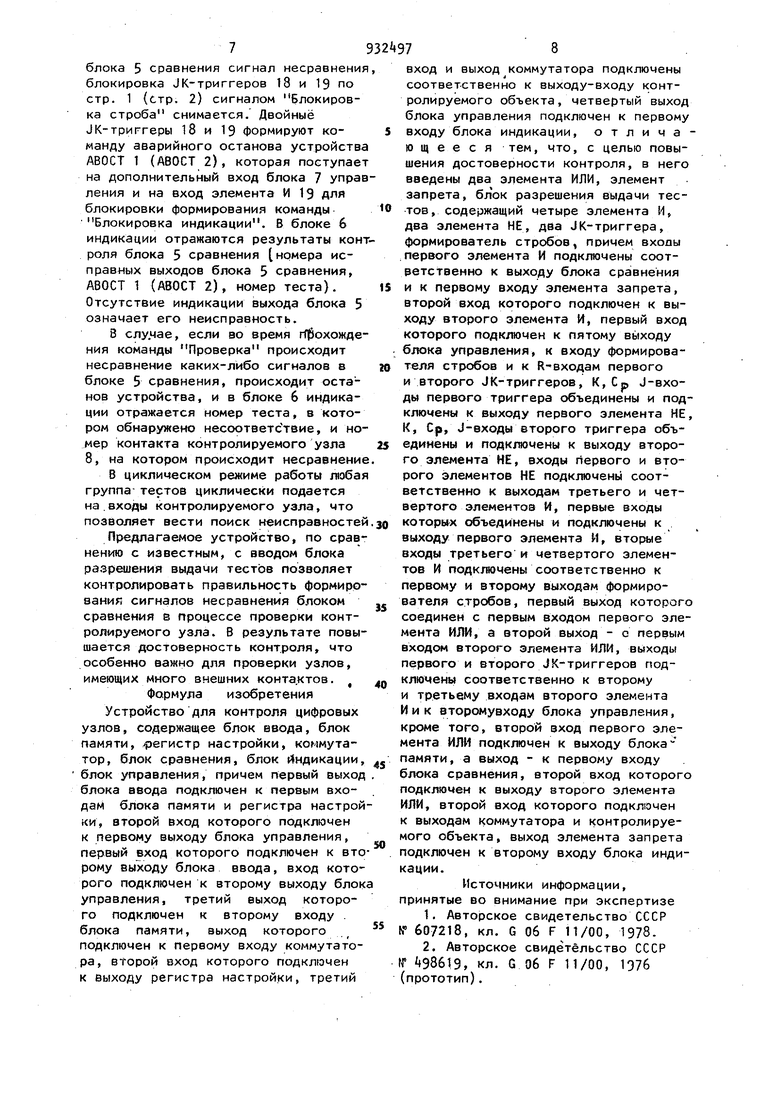

которого подключен к выходам коммутатора и контролируемого объекта, выход элемента запрета подключен к второму входу блока индикации. На фиг. 1 дана блок-схема устройства; на фиг. -2 - блок-схема блока разрешения выдачи тестов; на фиг. 3 диаграмма, поясняющая работу диспетчера стимулов.

Устройство содержит блок 1 ввода, блок 2 памяти, регистр 3 настройки, коммутатор k, блок 5 сравнения, блок .6 индикации, блок 7 управления, контролируемый узел 8, блок 9

s разрешения выдачи тестов, элементы ИЛИ 10 и 11, элемент 12 запрета.

Блок 9 разрешения выдачи тестов содержит элементы И . элементы НЕ 16 и 17, JK-триггеры 18 и 19,

элемент И 20, формирователь 21 стробов; блокировки теста 22, строб первый 23, строб второй 2, блокировка строб.а 25, блокировка индикации 26, АВОСТ 1-27 (АВОСТ 2), блокировка строба 28, АВОСТ 1-29, бло-. кировка индикации 30, позиции с характеризует исправную работу блока 5, позиции 28-30 характеризуют неисправную работу блока 5Первый вход блока 1 ввода соединен с входом блока 2 памяти и регистра 3 настройки. Выход регистра 3 настройки соединен с вторым входом коммутатора k, первый вход которого соединен с выходом блока 2 памяти и с первым входом блока 5 сравнения. Выход коммутатора соединен с внешними контактами контролируемого узла 8 и через элемент ИЛИ 11 с вторым входом блока 5 сравнения, выход которого через элемент 12 запрета соединен с входом блока 6 индикации. Второй выход блока 1 ввода соединен с входом блока 7 управления, выходы которого подключены соответственно к управляющим входам блока1 ввода, блока 2 памяти, регистра 3 настройки, блока 6 индикации. Дополнительный выход блока 7 управления соединен с первым входом бдока 9 разрешения выдачи тестов, второй вход которого соединен с выходом блока 5 сравнения. Первый управляющий выход блока 9 разрешения выдачи тестов соединен с

- дополнительным входом блока 7 управления, второй управлйюший выход с запретным входом элемента 12 запрета, первый стимулирующий выход через 5 элемент ИЛИ 10 с первым входом блока 5 сравнения, второй стимулирующий выход через элемент ИЛИ 11 с вторым входом блока 5 сравнения. Блок 1 ввода предназначен для ввода с перфоленты тестовой информации, информации о входных (выходных) контактах и командной информации. Блок 2 памяти предназначен для хранения и выдачи т-естовой информации, регистр 3 настройки - для управления коммутатором k. Коммутатор { передает сигналы на входы контролируемого узла. Блок 5 предназначен для сравнения кодов эталонов и стимулов с сигналами на внешних контактах контролируемого узла 8, а так же для сравнения стимулирующих стробов между собой, поступающих из блока 9 разрешения выдачи тестов. Блок 6 индикации предназначен для индикации результатов контроля и при несоответствии кодов - индикации номера теста и номера контакта, на котором обнаружено несравнение. Блок 25

7 управления организует работу всех блоков устройства, т.е. управляет записью информации из блока 1 ввода в блок 2 памяти и регистр 3 настройки, управляет работой блока 6 индикации, блока 9 разрешения выдачи тестов и осуществляет управление однократным и циклическим режимами работы. Блок 9 разрешения выдачи тестов разрешает выдачу тестов в контролируемый узел 8 по положительным результатам контроля блока 5 сравнения по стимулирующим стробам. Контроль осуществляется с помощью тестов, включающих в себя стимулы и эталоны. Стимулы - совокупность сигналов, одновременно подаваемых на входные контакты, эталоны - совокупность сигналов, которые должны появиться на выходных контактах исправного узла при подаче на его вход стимулов.

I

Устройство работает следующим

образом.

По сигналам управления с блока 7 командная информация из блока 1 ввода поступает в блок управления и включает команды Начало, Запись 1, Запись 2, Блокировка теста, Проверка, Конец.

По команде Начало все блоки устройства устанавливаются в исходное состояние.

теста поступает на вход элемента И 20, который формирует команду Блокировка индикации, блокирующую прохождение сигналов несравнения

с выхода блока S сравнения через элемент 12 запрета в блок 6 индикации и останов устройства по неисправности.

По команде Проверка начинается считывание информации из блока 2 памяти. Считанный тест поступает на первые входы коммутатора Ц, который выделяет стимулы из тестз и подает их на входы контролируемого узла 8. Работой коммутатора k уп0равляет регистр 3 настройки, в котором хранится информация о входных контактах контролируемого узла 8. Одновременно тест поступает и на

5 первье входы блока 5 ера в не т- я через элемент ИЛИ 10. Стимулы, выделенные коммутатором k из теста, поступают на входы контоолируемогс узла 8, а затем вместе с сигналом последнего поступают на вторые аходы блока

0 сравнения 5 через элемент ИЛИ 1.

8 однократном режиме работы тест. на вход контролируемого узла 8 подаются однократно и по команде Конец из блока 6 индикации фиксируSется результат контроля.

В случае, если во время прохождения команды Блокировка теста не сформируется по какому-л бо выходу 7 По команде Запись 1 в регистр 3 настройки записывается информация о входных контактах проверяемого узла 8. По команде Запись 2 тестовая информация записывается в блок 2 памяти. По команде Блокировка теста начинает работать блок 9 разрешения выдачи тестов (фиг. 2). В пределах длительности команды Блокировка теста (фиг, 3) формирователь 21 стробов формирует стимулирующие стробы (стр. 1, стр. 2). Стр. 1 (стр. 2) через элемент ИЛИ 10 (11) поступает на первые (вторые) входы блока 5 сравнения, который вырабатывает сигналы иесравнения. Сигналы несравненип поступают на входы элемента И 13. Элемент И 13 формирует сигнал Бгюкировка строба, блокирующий запуск J К-триггеров 18 и «19 по стр. 1 (стр. 2) через элемент И (15) и элемент НЕ 16 (17). Одновременно команда Блокировка 7 блока 5 сравнения сигнал несравнени блокировка JK-триггеров 18 и 19 по стр. 1 (стр. 2) сигналом Блокировка строба снимается. Двойные JК-триггеры 18 и 19 формируют команду аварийного останова устройств АВОСТ 1 (АВОСТ 2), которая поступае на дополнительный вход блока 7 упра ления и на вход элемента И lg для блокировки формирования команды Блокировка индикации. В блоке 6 индикации отражаются результаты кон роля блока 5 сравнения номера исправных выходов блока 5 сравнения, АВОСТ 1 (АВОСТ 2), номер теста}. Отсутствие индикации выхода блока 5 означает его неисправность. 8 слу.чае, если во время гфохожде ния команды Проверка происходит несравнение каких-либо сигналов в блоке 5 сравнения, происходит останов устройства, и в блоке 6 индикации отражается номер теста, в котором обнаружено несоответствие, и но мер контакта контролируемого узла 8, на котором происходит несраенени В циклическом режиме работы группа тестов циклически подается на.входы контролируемого узла, что позволяет вести поиск неисправносте Предлагаемое устройство, по срав нению с известным, с вводом блока разрешения выдачи тестов позволяет контролировать правильность формиро вания сигналов несравнения блоком сравнения в процессе проверки контролируемого узла. В результате повы шается достоверность контроля, что особенно важно для проверки узлов, имеющих много внешних контактов. , Формула изобретения Устройство для контроля цифровых узлов, содержащее блок ввода, блок памяти, регистр настройки, коммутатор, блок сравнения, блок индикации, блок управления, причем первый выход блока ввода подключен к первым входам блока памяти и регистра настройки, второй вход которого подключен к первому выходу блока управления, первый вход которого подключен к второму выходу блока ввода, вход которого подключен к второму выходу блока управления, третий выход которого подключен к второму входу . блока памяти, выход которого подключен к первому входу коммутатора, второй вход которого подключен к ВЫХОДУ регистра настройки, третий 7 вход и выход коммутатора подключены соответственно к выходу-входу контролируемого объекта, четвертый выход блока управления подключен к первому входу блока индикации, отличающееся тем, что, с целью повышения достоверности контроля, в него введены два элемента ИЛИ, элемент запрета, блок разрешения выдачи тестов, содержащий четыре элемента И, два элемента НЕ, два JK-триггера, формирователь стробов, причем входы первого элемента И подключены соответственно к выходу блока сравнения и к первому входу элемента запрета, второй вход которого подключен к выходу второго элемента И, первый вход которого подключен к пятому ВЬ1ХОДУ блока управления, к входу формирователя стробов и к R-входам первого и второго JK-триггеров, К, Ср J-BXOды первого триггера объединены и подключены к выходу первого элемента НЕ, К, Ср, J-8xoды второго триггера объединены и подключены к выходу второго элемента НЕ, входы первого и второго элементов НЕ подключень соответственно к выходам третьего и четвертого элементов И, первые входы которых объединены и подключены к выходу первого элемента И, вторые входы третьего и четвертого элементов И подключены соответственно к первому и второму выходам формирователя стробов, первый выход которого соединен с первым входом первого элемента ИЛИ, а второй выход - с первым входом второго элемента ИЛИ, выходы первого и второго JK-триггеров подключены соответственно к второму и третьему входам второго элемента Иик второмувходу блока управления, кроме того, второй вход первого элемента ИЛИ подключен к выходу блока памяти, а выход - к первому входу блока сравнения, второй вход которого подключен к выходу второго элемента ИЛИ, второй вход которого подключен к выходам коммутатора и контролируемого объекта, выход элемента запрета подключен к второму входу блока индикации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 607218, кл. G Об F 11/00, 1973. 2.Авторское свидетельство СССР ff , кл. G Об F 11/00, 1Э76 (прототип).

-т4

Hmfofim f

АотХммк t

Mi Awf «.2

LJ

2J

a

26 27

2« 25 30

Фи.г.3

Авторы

Даты

1982-05-30—Публикация

1980-01-16—Подача