(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Устройство для тестового контроля блоков радиоэлектронной аппаратуры | 1980 |

|

SU905887A1 |

| Устройство для контроля цифровых узлов | 1974 |

|

SU498619A1 |

| Устройство для контроля логическихблОКОВ | 1978 |

|

SU813430A1 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU932497A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1003090A1 |

| Устройство для контроля цифровыхблОКОВ | 1979 |

|

SU796860A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1518906A2 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1247898A2 |

1

Изобретение относится к вычислительной технике и может быть использовано для контроляцифровых узлов, устройств вычислительной техники, а также интегральных схем и является усовершенствованием известного устройства, описанного в авт. св. № 498619.

В основном авт. св. № 498619 описано устройство для контроля цифровых узлов, содержащее блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, блок управления Ш

Первый выход блока ввода соединен с блоком памяти, выход которого подключен к первому входу блока сравнения и к первому входу блока коммутатора, выходами соединенного с внешними контактами контролируемого узла, второй вход коммутатора соединен с регистром настройки. Второй выход блока ввода соединен с входом блока управления, выходы которого подключены соответственно к управляющим входам блока ввода, блока памяти, регистра наст-

ройки и блока индикации, соединенного с выходом блока сравнения.

Такое устройство не позволяет контролировать временной промежуток между моментом сигналов на входные контакты коммутационного узла и моментом выдачи сигналов с контролируемого узла.

Целью изобретения является повышение достоверности работы устройства.

Это достигается тем, что в предложенное устройство введен дешифратор режимов, первый вход которого подключен к дополнительному выходу блока управления, второй вход соединен с дополнительным выходом блока ввода, а выход подключен к дополнительному входу блока, управления.

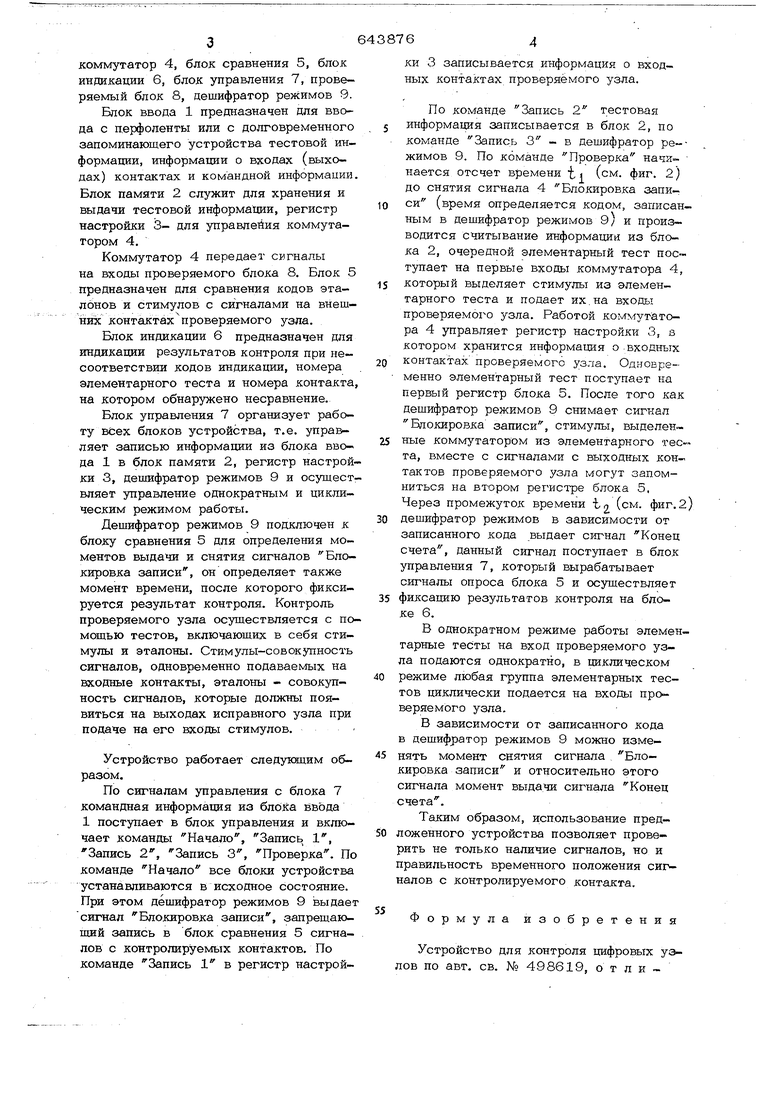

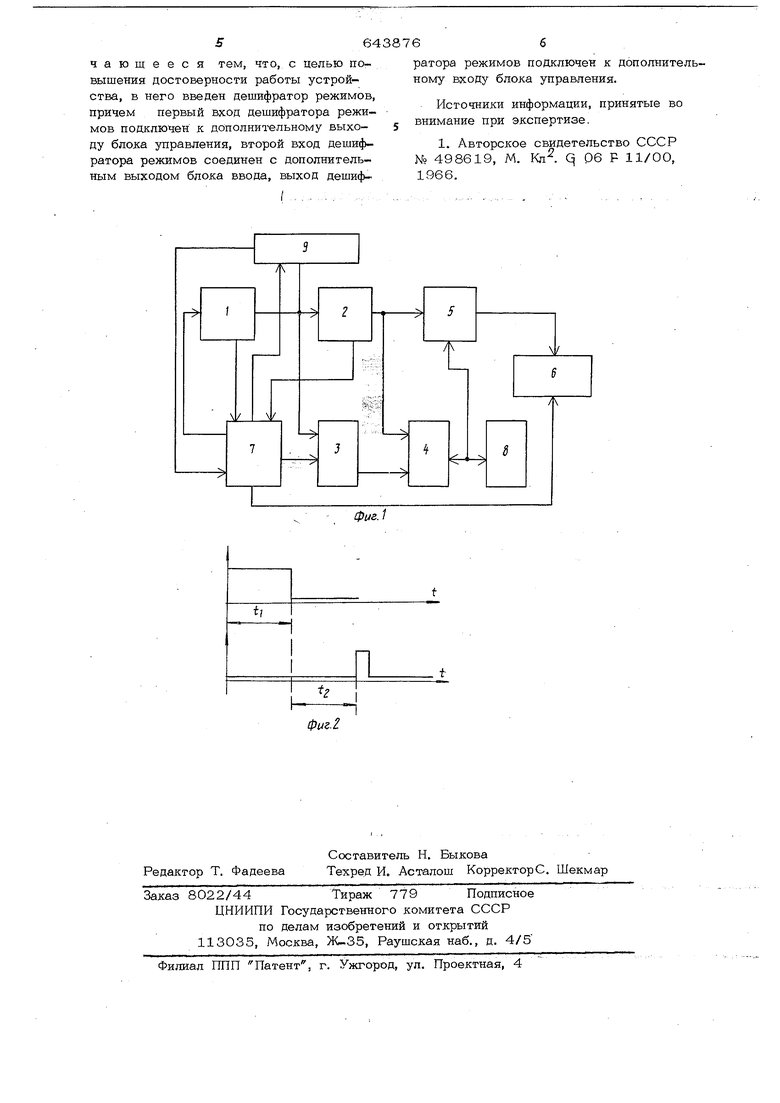

На фиг. 1 дана структурная схема предлагаемого устройства; на фиг. 2 диаграмма, пояснякшая работу устрой. ства.

Устройство содержит блок ввода 1, блок памяти 2, регистр настройки 3,

коммутатор 4, блок сравнения 5, блок индикации 6, блок управления 7, проверяемый блок 8, дешифратор pexcHivfOB 9.

Блок ввода 1 предназначен для ввода с перфоленты или с долговременного запоминающего устройства тестовой информации, информации о входах (выходах) контактах и командной информации. Блок памяти 2 служит для хранения и выдачи тестовой информации, регистр настройки 3- для управлейия коммутатором 4.

Коммутатор 4 передает сигналы на входы проверяемого блока 8. Блок 5 предназначен для сравнения кодов эталонов и стимулов с сигналами на внешних контактах проверяемого узла.

Блок индикации 6 предназначен для индикации результатов контроля при несоответствии кодов индикации, номера элементарного теста и номера контакта, на котором обнаружено несравнение.

Блок управления 7 организует работу Bfcex блоков устройства, т.е. управляет записью информации из блока ввода 1 в блок памяти 2, регистр настройки 3, дешифратор режимов 9 и осуществляет управление однократным и циклическим режимом работы.

Дешифратор режимов 9 подключен к блоку сравнения 5 для определения моментов выдачи и снятия сигналов Блокировка записи, он определяет также момент времени, после которого фиксируется результат контроля. Контроль проверяемого узла осуществляется с помощью тестов, включающих в себя стимулы и эталоны. Стимулы-совокупность сигналов, одновременно подаваемых на входные контакты, эталоны - совокупность сигналов, которые должны появиться на выходах исправного узла при подаче на его входы стимулов.

Устройство работает следующим образом.

По сигналам управления с блока 7 командная информация из блока йвода 1 поступает в блок управления и включает команды Начало, Записц 1, Запись 2, Запись 3, Проверка. По команде Начало все блоки устройства устанавливаются в исходное состояние. При этом дешифратор режимов 9 выдает сигнал Блокировка записи, запрещающий запись в блок сравнения 5 сигналов с контролируемых контактов. По команде Запись 1 в регистр настройки 3 записывается информация о входных контактах проверяемого узла.

По команде Запись 2 тестовая информация записывается в блок 2, по команде Запись 3 - в дешифратор ре-жимов 9. По команде Проверка начянается отсчет времени t, i (см. фиг. 2) до снятия сигнала 4 Блокировка записи (время определяется кодом, записанным в дешифратор режимов 9/ и производится считывание информации из блока 2, очередной элементарный тест поступает на первые входы коммутатора 4, который выделяет стимулы из элементарного теста и подает их.на входы проверяемого узла. Работой коммут&тора 4 управляет регистр настройки 3, s котором хранится информация о входных контактах проверяемого узла. Одновременно элементарный тест поступает на первый регистр блока 5. После того как дешифратор режимов 9 снимает сигнал Блокировка записи, стимулы, выделенные коммутатором из элементарного геста, вместе с сигналами с выходных контактов проверяемого узла могут запомниться на втором регистре блока 5. Через промежуток времени to (см. фиг.2) дешифратор режимов в зависимости от записанного кода выдает сигнал Коней счета, данный сигнал поступает в блок управления 7, который вырабатывает сигналы опроса блока 5 и осуществляет фиксацию результатов контроля на блоке 6.

В однократном режиме работы элементарные тесты на вход проверяемого узла подаются однократно, в циклическом режиме любая группа элементарных тестов циклически подается на входы проверяемого узла.

В зависимости от записанного кода в дешифратор режимов 9 можно изме- нять момент снятия сигнала . Блокировка записи и относительно этого сигнала момент выдачи сигнала Конец счета.

Таким образом, использование предложенного устройства позволяет проверить не только наличие сигналов, но и правильность временного положения сипналов с контролируемого контакта.

Формула изобретения

Устройство для контроля цифровых узлов по авт. св. № 498619, от личающееся тем, что, с целью повышения достоверности работы устройства, в него введен дешифратор режимов, причем первый вход дешифратора режимов подключен к дополнительному выходу блока управления, второй вход дешифратора режимов соединен с дополнительным выходом блока ввода, выход дешифратора режимов подключен к дополнительному входу блока управления.

Источники информации, принятые во внимание при экспертизе.

Авторы

Даты

1979-01-25—Публикация

1977-10-10—Подача