(54) ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1981 |

|

SU993246A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Программируемая логическая матрица | 1986 |

|

SU1381481A1 |

| Дискретно-цифровой электропривод | 1985 |

|

SU1350800A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для программного управления | 1987 |

|

SU1439535A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

I

Изобретение относится к вычнспитеп ной технике и цифровой автома-тке. Оио может исполвэзоваться в с)ВМ, вычислительных: устройствах и приборах цифровой автоматики для запоминания микропрограмм, кодопреообразования, реализации комбинационных устройств различного назначения: управляющих, арифметв- : чеоких, логических и др.

Известны устройства для запоминания Данных и кодопреобразов 1ния - программируемые логические матрицы (ПЛМ), состоящие из двух частей: подматрицы выработки логических произведений и подматрицы вьфаботки выходных слов. В первой части входные сигналы или их отрвцання селективно подсоединяются к шинам логических произведений (про межуточным шинам/ таким офазом, что определенная комбинация входных сигналов дает на одной из шин или на их некоторой совокупности сигнал, соответствующий логической единице. Информа- цвя с этих шин вводится во вторую no/v

матрицу, в которой выходные шины селективно подсоединяются к промежуточным шннам. Селективность соединений в обеих подматрицах обеспечивается программированием при помощи фотошабпоаа. Запоминание и кодообразование ининформации обеспечивается соответствующим селективным подсоединением шин в обеих подматрвдах устройства l и 2.

Недостатком устройства является невозможность программирования его в уоЛОВИ51Х эксплуатации.

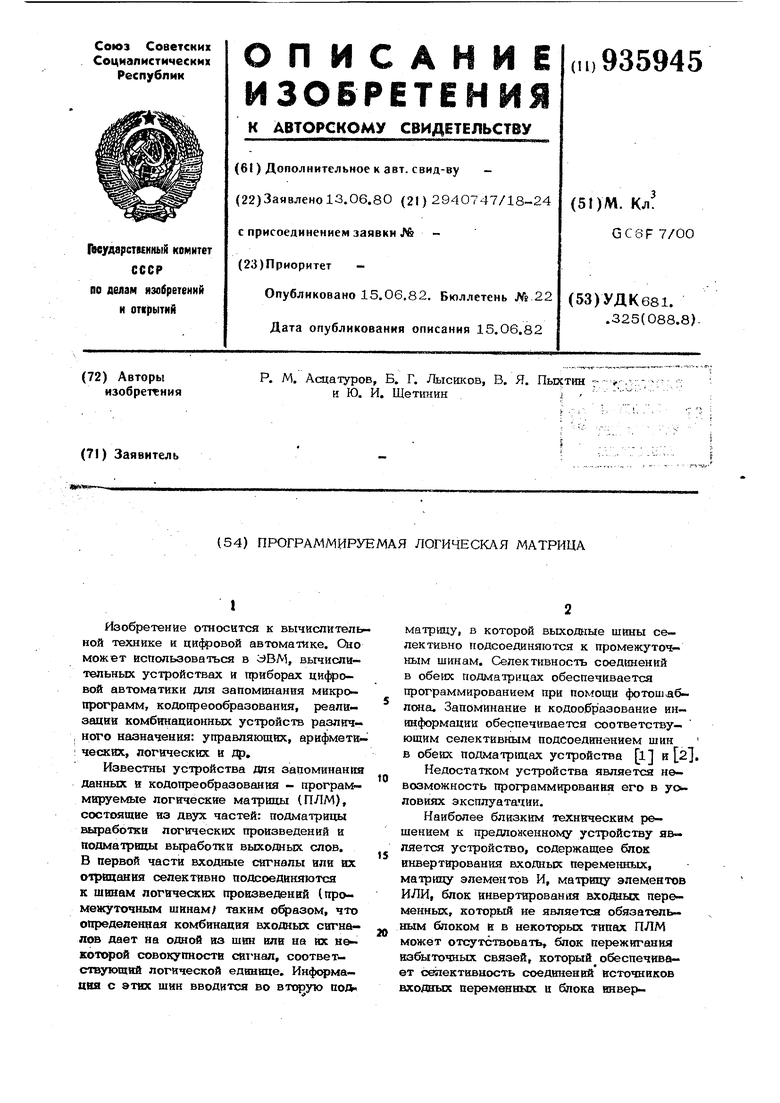

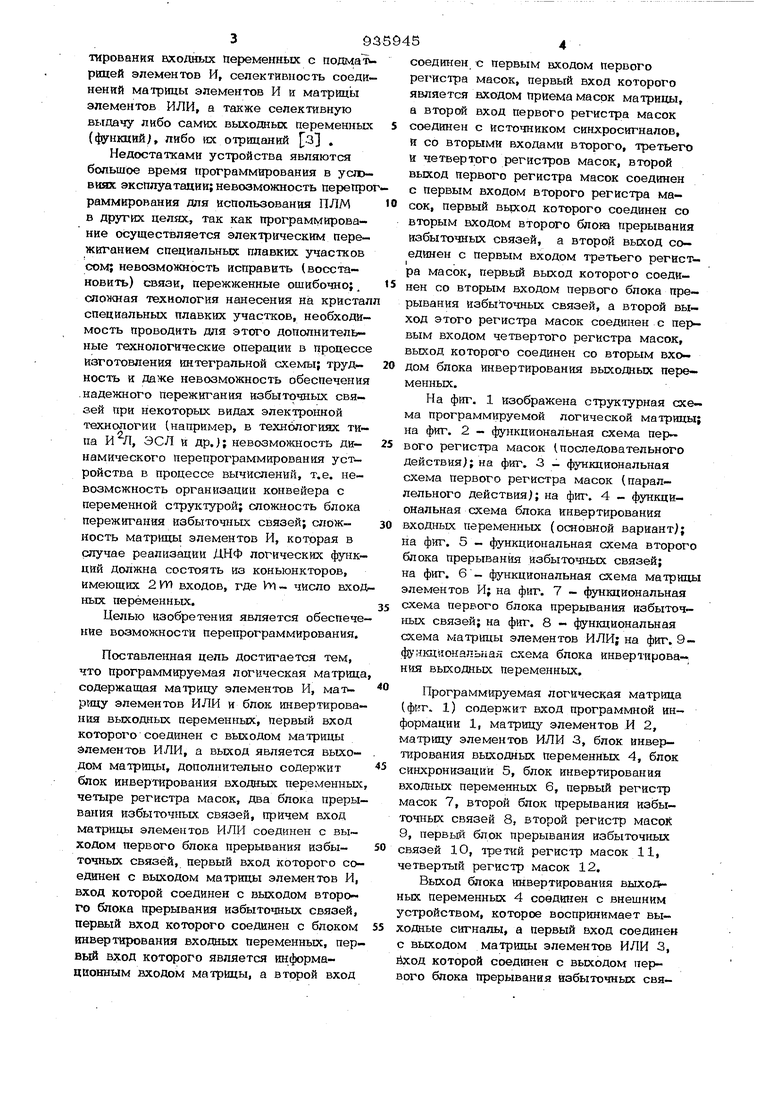

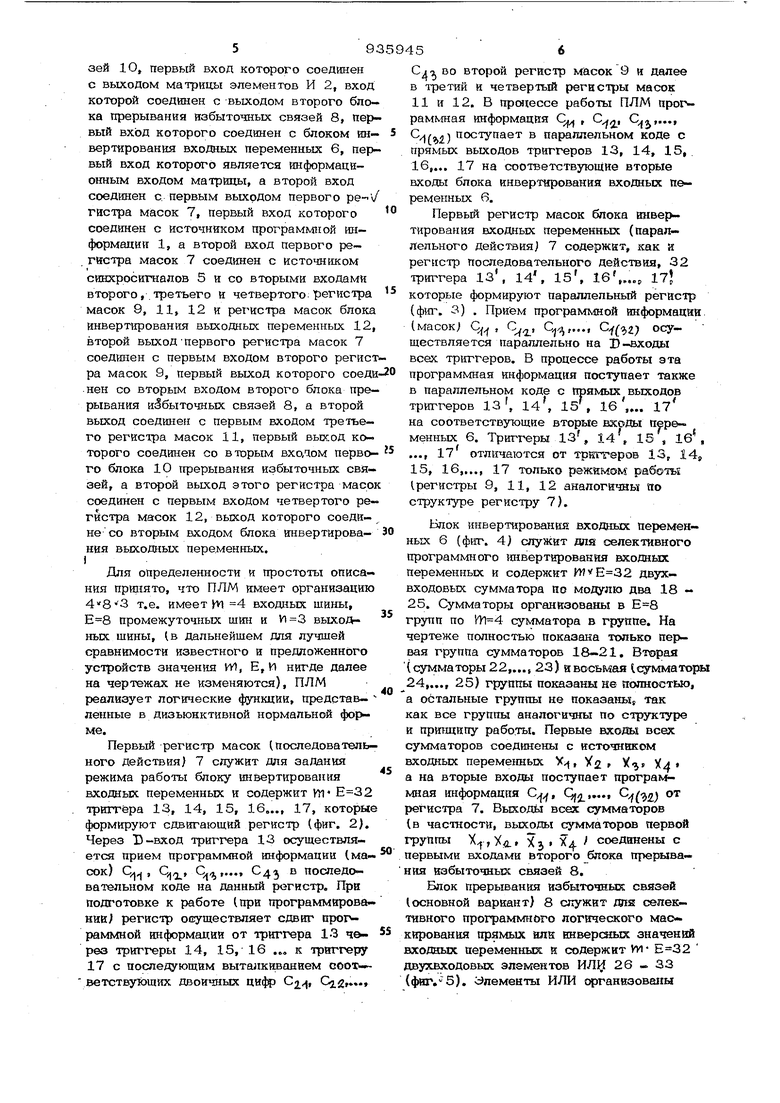

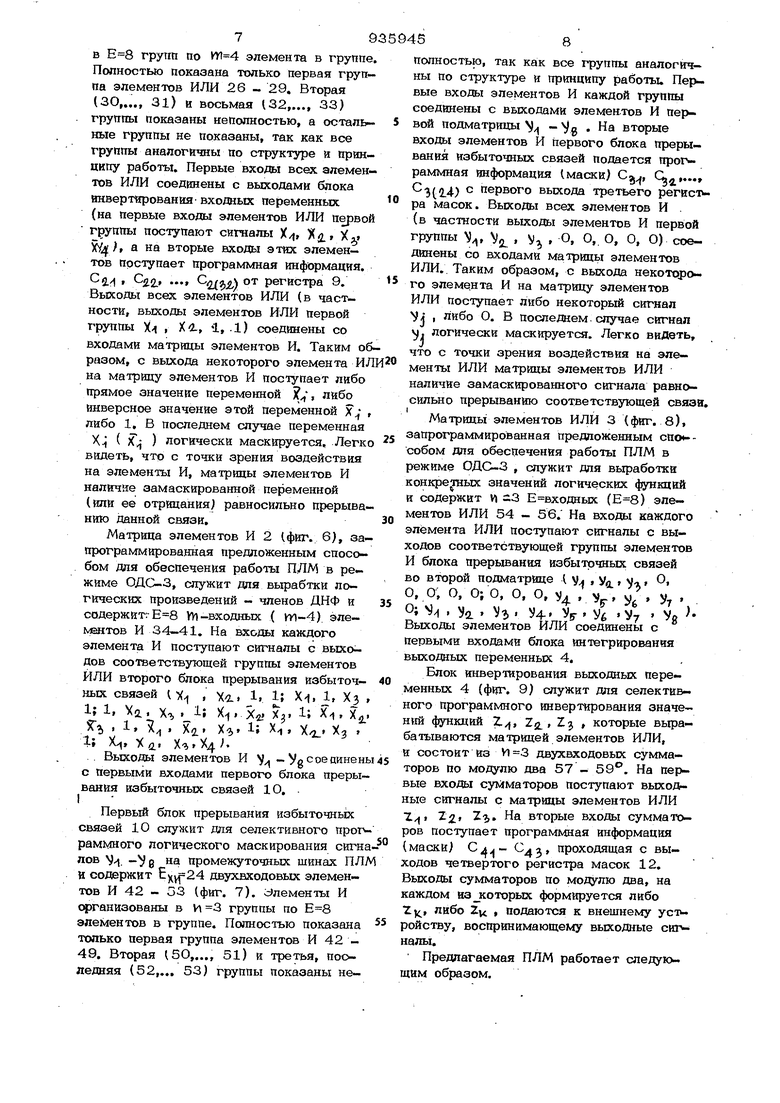

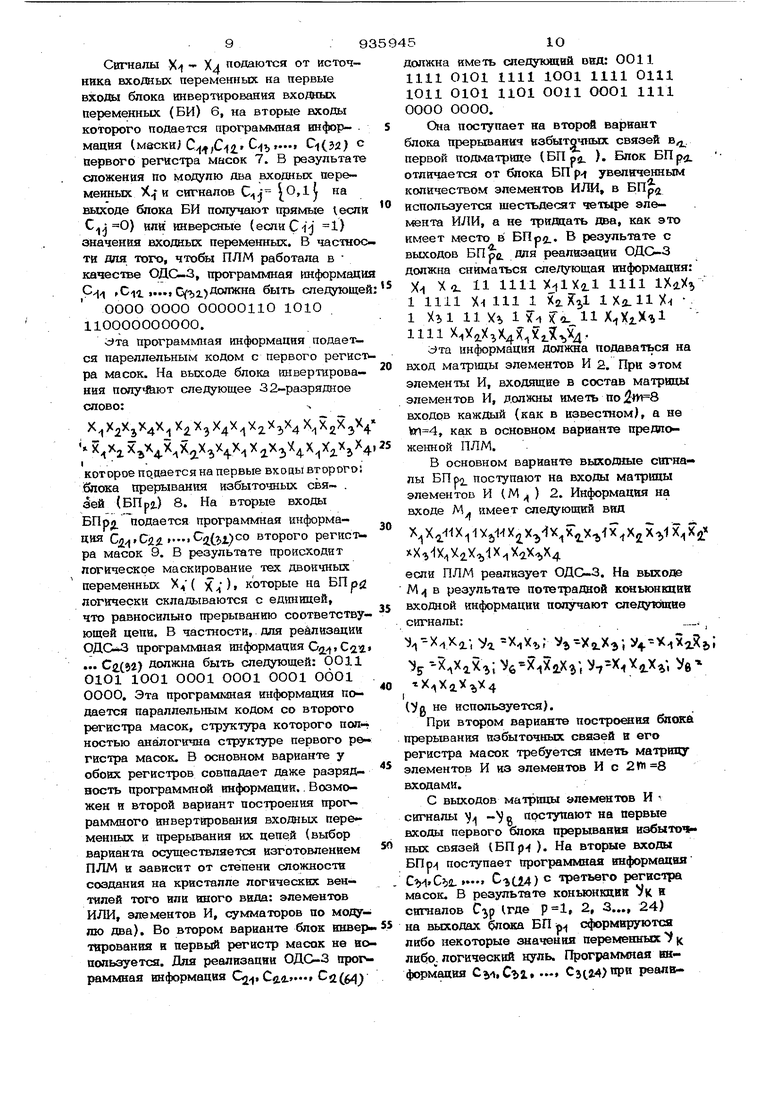

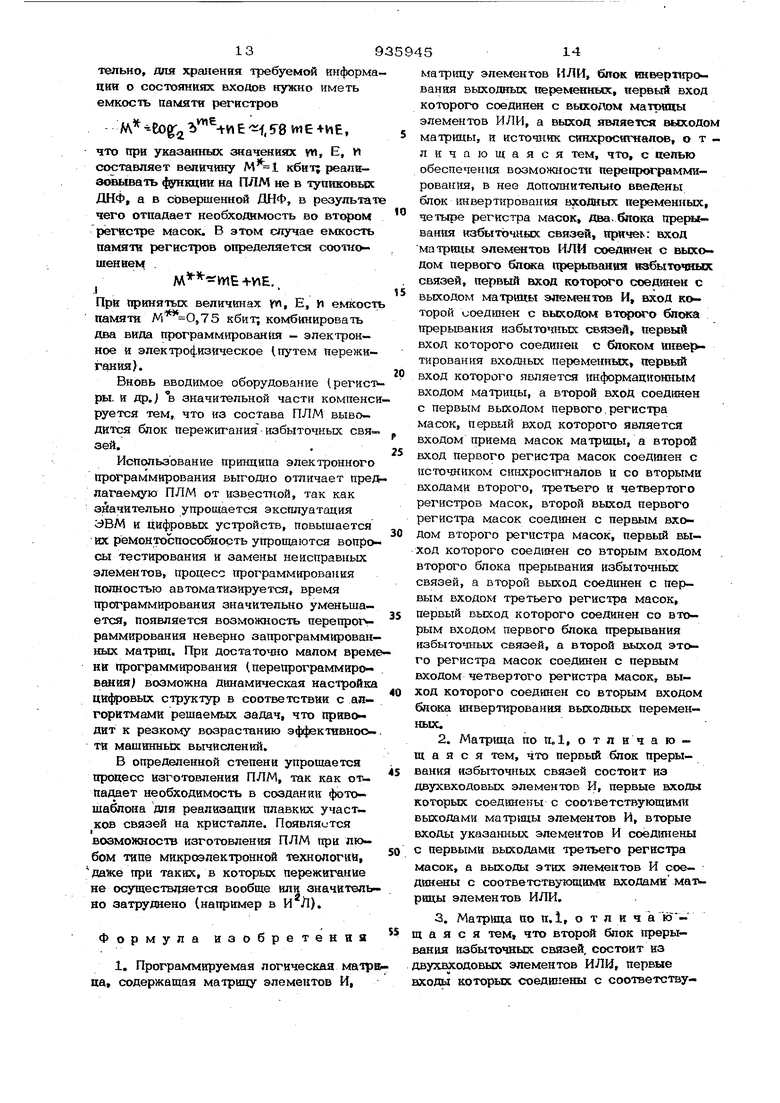

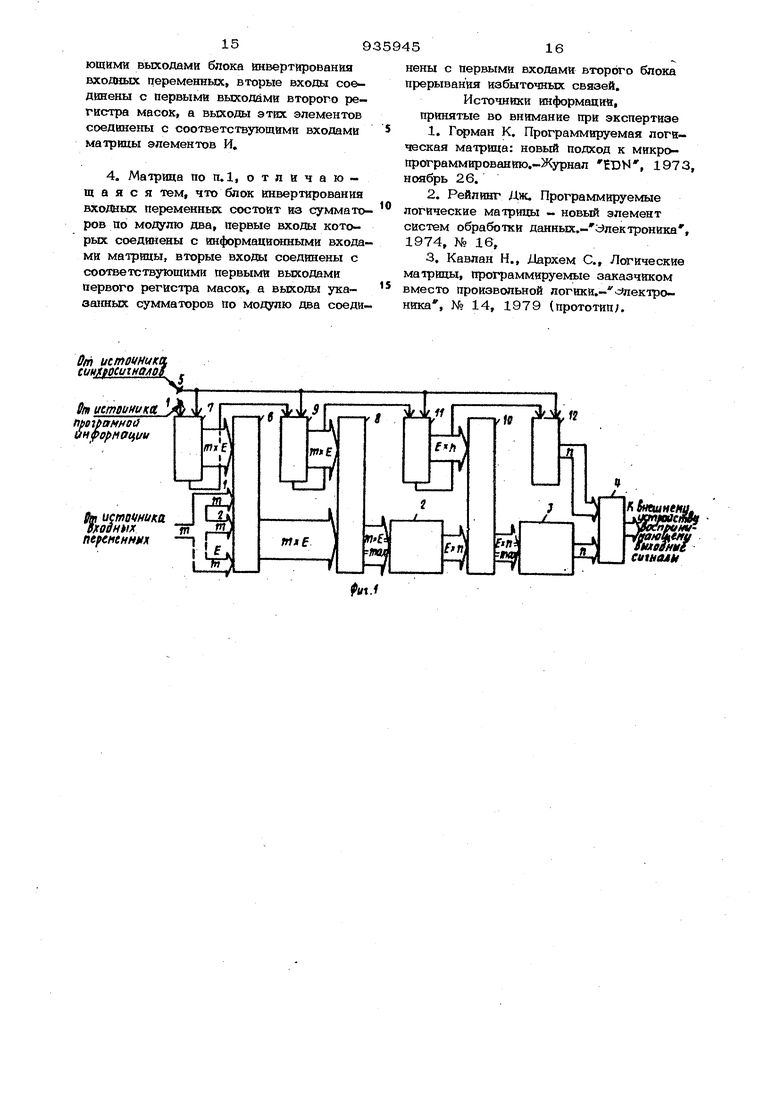

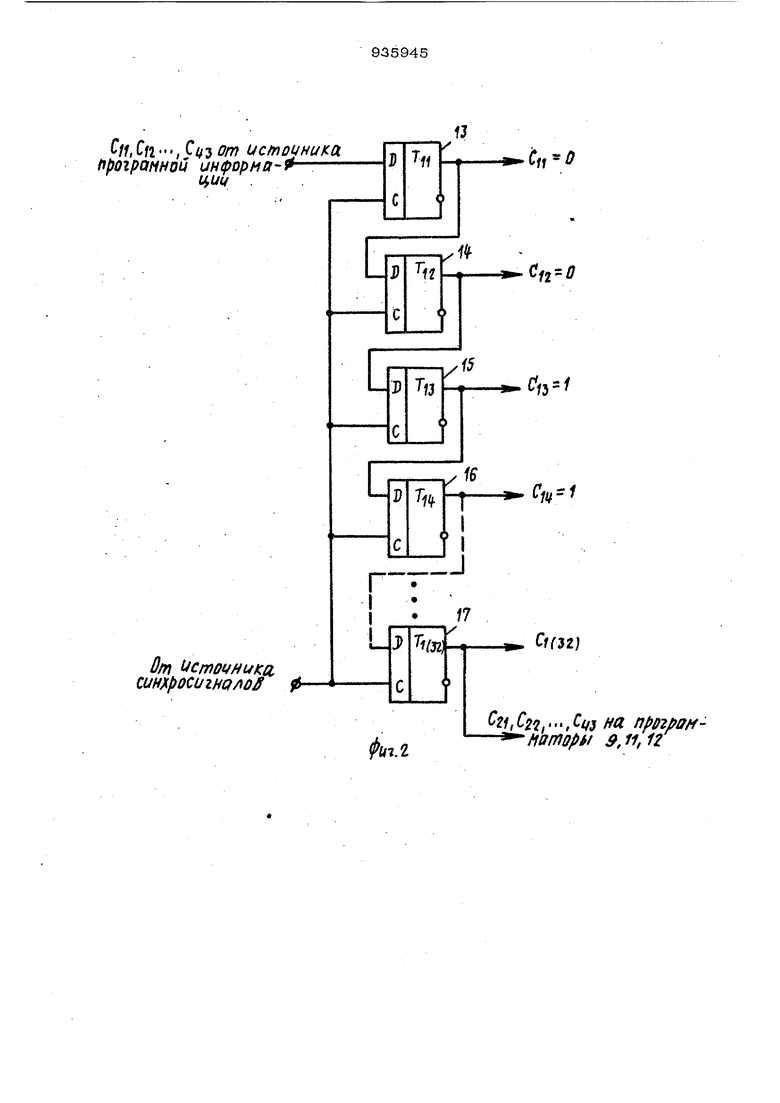

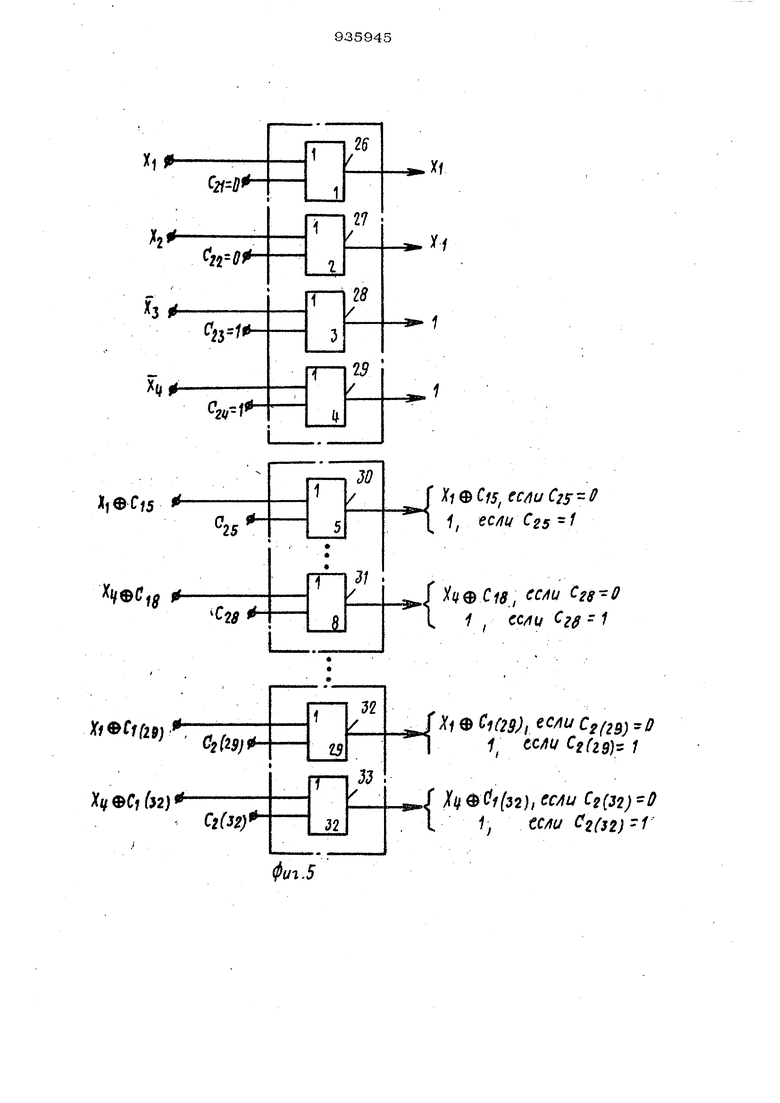

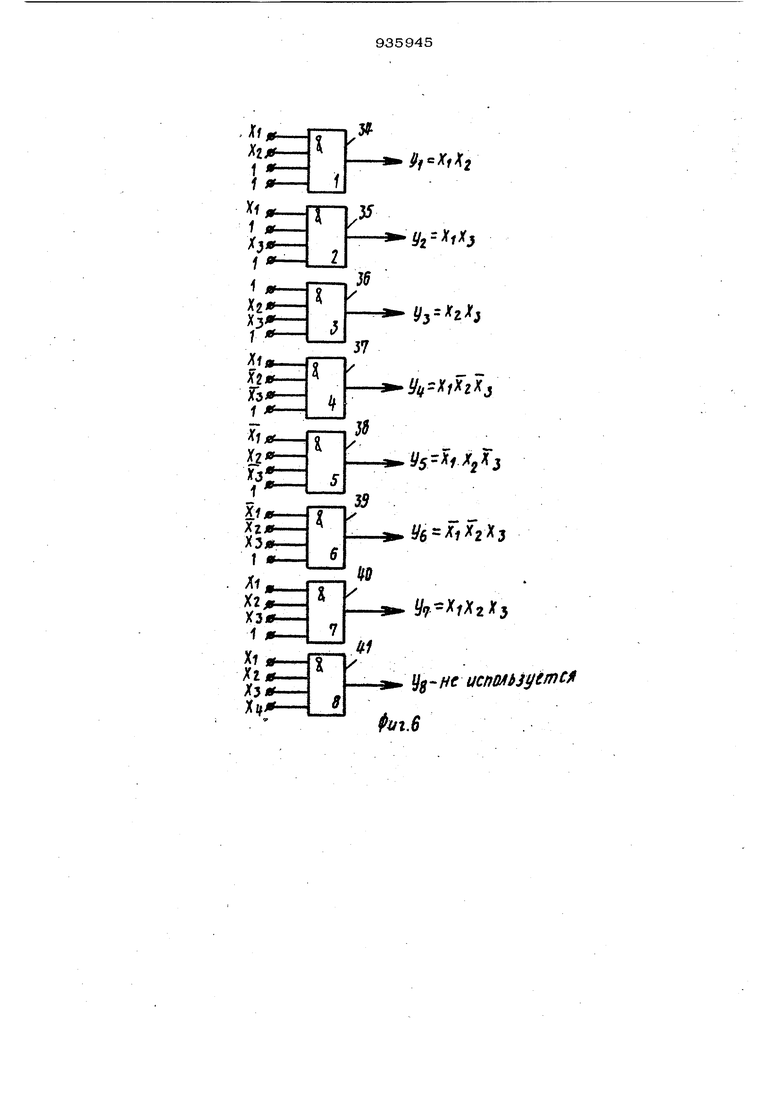

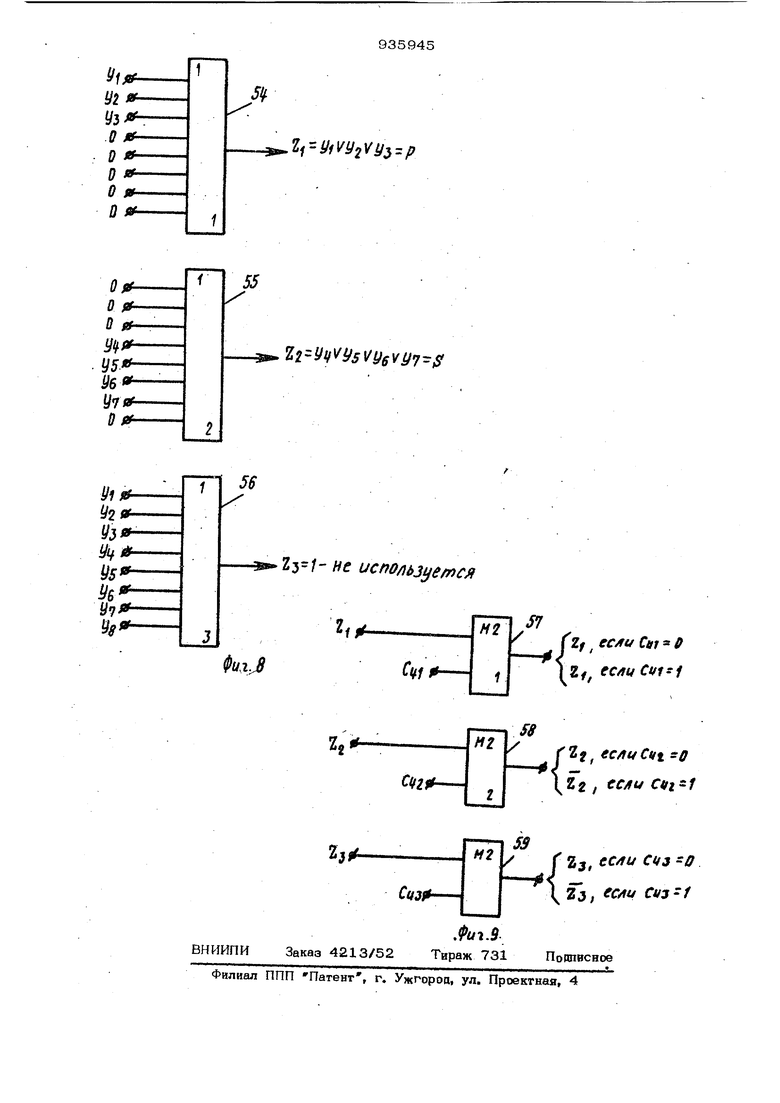

Наиболее близким техническим решением к предложенному устройству является устройство, содержащее блок инвертирования входных переменных, матрицу элементов И, матрицу элементов ИЛИ, блок инвертирования входных переменных, который не является обязательным блоком к в некоторых типах ПЛМ может отсутствовать, блок пережигания избыточных связей, который обеспечивает сстективность соединений источников входных переменных и блока инвертирования входных переменных е подмат рвщей элементов И, селективность соединений матрицы эпементов И и матрицы элементов ИЛИ, а также селективную выдачу либо самих выходных переменных (функций;, либо их отрицаний з . Недостатками устройства являются большое время программирования в усшBHsDc эксплуатации; невозможность перепро раммирования для использования ПЛМ в других целях, так как программирование осуществляется электрическим пережиганием специальных плавких участков сом; невозможность исправить (восстановить) связи, пережженные ошибочно; слочдаая технология нанесения на кристал специальных плавких участков, необходимость проводить для этого дополнительные технологические операции Б процессе изготовления интегральной схемы; трудность и Даже невозможность обеспечения .надежного пережигания избыточных связей при некоторых видах электронной технологии (например, в технологиях типа , ЭСЛ и др.); невозможность динамического перепрограммирования устройства в процессе вычислений, т.е. невозможность организации конвейера с переменной структурой; сложность блока пережигания избыточных связей; сложность матрицы элементов И, которая в случае реализации ДНФ логических функций Должна состоять из коньюнкторов, имеющих 2 YY входов, где Vn число вход ных переменных. Целью изобретения является обеспече ние возможности перепрограммирования. Поставленная цель достигается тем, что программируемая логическая матрица содержащая матрицу элементов И, мат рвду элементов ИЛИ и блок, инвертирования выходньсс переменных, первый вход которого соединен с выходом матрицы элементов ИЛИ, а выход является выходом матрицы, дополнительно содержит блок инвертирования входных переменных четыре регистра масок, два блока прерывания избыточных связей, причем вход матрицы элементов ИЛИ соединен с выходом первого блока прерывания избыточных связей, первый вход которого соединен с выходом матрицы элементов И, вход которой соединен с выходом второ го блока прерывания избыточных связей, первый вход которого соединен с блоком 55 инвертирования входных переменных, первый вход которого является информационным входом матрицы, а второй вход соединен с первым входом первого регистра масок, первый вход которого является входом приема масок матрицы, а второй вход первого регистра масок соединен с источником синхросигналов, и со вторыми входами второго, третьего и четвертого регистров масок, второй выход первого регистра масок соединен с первым входом второго регистра масок, первый вьрсод которого соединен со вторым входом второго блога прерывания избыточньк связей, а второй выход соединен с Первым входом третьего регистра масок, первый выход которого соединен со вторым входом первого блока прерывания избыточных связей, а второй выход этого регистра масок соединен с первым входом четвертого регистра масок, выход которого соединен со вторым входом блока инвертирования выходных переменных. На фиг. 1 изображена структурная схема программируемой логической матрицы; на фиг. 2 - функциональная схема пер- вого регистра масок (последовательного действия); на фиг. 3 - функциональная схема первого регистра масок (параллельного действия); на фиг. 4 - функциональная схема блока инвертирования входных переменных (основной вариант); на фиг. 5 - функциональная схема второго блока прерывания избыточных связей; на фиг. 6 - функциональная схема матрицы элементов И; на фиг. 7 - функциональная схема первого блока прерывания избыточных связей; на фиг. 8 - функциональная схема матрицы элементов ИЛИ; на фиг. 9- функциональная схема блока инвертирования выходных переменных. Программируемая логическая матрица (фиг. 1) содержит вход программной информации 1, матрищ элементов И 2, матрицу элементов ИЛИ 3, блок инвертирования выходных переменных 4, блок синхронизации 5, блок инвертирования входных переменных 6, первый регистр масок 7, второй блок прерывания избыточных связей 8, второй регистр масок 9, первый блок прерывания избыточных связей 1О, третий регистр масок 11, четвертый регистр масок 12. Выход блока инвертирования выходных переменных 4 соединен с внешним устройством, которое воспринимает выходные сигналы, а первый вход соединен с выходом матрицы элементов ИЛИ 3, ёход которой соединен с выходом первого блока прерывания избыточных связей 10, первый вход которого соединен с выходом матрицы элементов И 2, вход которой соединен с выходом второго блока прерывания избыточных связей 8, первый вход которого соединен с блоком ин- вертирования входных переменных 6, первый вход которого является информационным входом матрицы, а второй вход соединен с. первым выходом первого гистра масок 7, первый вход которого соединен с источником программной информации 1, а второй вход первого регистра масок 7 соединен с источником синхросипшлов 5 и со вторыми входами второго,.третьего и четвертого регистра масок 9, 11, 12 и регистра масок блока инвертирования выходных переменных 12, второй выход первого регистра масок 7 соединен с первым входом второго регист ра масок 9, первый выход которого соеди ней со вторым входом второго блока прерывания и5быточньк связей 8, а второй выход соединен с первым входом третьего регистра масок 11, первый выход которого соединен со вторым входом перво го блока 10 гферывания избыточных связей, а второй выход этого регистра масок соединен с первым входом четвертого регистра масок 12, выход которого соединесо вторым входом блока инвертирова- кия выходных переменных, I Для определенности и простоты описания при11ято, что ПЛМ имеет организацию 4 83 т.е. имеет И1 4 вход1 Ы С шины, промежуточных шин и выходных шины, (в дальнейшем для лучшей сравнимости известного н предлокенного устройств значения W, Е, И нигде далее на чертежах не изменяются), ПЛМ реализует логические функции, представ- ленные в дизъюнктивной нормальной форуме. Первый регистр масок (последовательного действия) 7 служит для задания режима работы блоку инвертирования входных переменных и содержит vvi« триггера 13, 14, 15, 16..., 17, которые формируют сдвигаюш;ий регистр (фиг. 2). Через Б-вход триггера 13 осуществляется прием программной информации (масок) О| , С, С,..., С43 последовательном коде на данный регистр. При подготовке к работе (при программировании регистр осуществляет сдвиг программной информации от триггера 1-3 ч&рез триггеры 14, 15, 16 .., к триггеру 17 с после огющим выталкиванием cootw ветствующих двоичных С, Cj./;,..., Сда ВО второй регистр масок 9 и далее в 1ретий и четвертый регистры масок 11 и 12. В npcMiecce работы ПЛМ програмкшая информация С , , С. ,..., ) поступает в параллельном коде с прямых выходов триггеров 13, 14, 15,. 16,... 17 на соответствующие вторые входы блока инвертирования входных переменных 6. Первый регистр масок блока инвертирования входных переменных (параллельного действия) 7 содержит, как и регистр последовательного действия, 32 триггера 13, 14, 15, 16,..., 17 которые формируют параллельный регистр (фиг. 3) . Прием программной информации (масок) С , С, Qj,..., C() осуществляется параллельно на D-входы всех триггеров. В процессе работы эта программная информация поступает также в параллельном коде с прямых выходов триггеров 13, 14, 154 16,... 17 на соответствующие вторые входы переменных 6. Триггеры 13, 14, 15 , 16 , ..., 17 отличаются от триггеров 13, 14, 15, 16,..., 17 только режимом работы (регистры 9, 11, 12 аналогичны «о структуре регистру 7). Блок инвертирования входных Переменных 6 (фиг. 4) служит для селективного программного инвертирования входных переменных и содерхскт двухвходовых сумматора по модулю два 18 25. Сумматоры организовань в групп по сумматора в группе. На чертеже полностью показана только первая группа сумматоров 18-21. Вторая (сумма торы 2 2,..., 23) а восьмая I сумма торы 24,..., 25) группы показаны не полностью, а остальные группы не показаны так как все группы аналогичны по структуре и притщипу рабо.ты. Первые входы всех сумматоров соединены с источником входных переме1шых У,У2 Vf-j У а на вторые входы поступает програм мная информация С, Qj. -ffJi) регистра 7. Выходы всеж сумматоров (в частности, выходы сумматоров первой группы Х, Xfl., Хз 4 соединены с первыми входами второго блока прерывания избыточных связей 8, Блок прерывания избыточных связей (основной вариант) 8 служит дан селективного программного логического маокированкя прямых нлв инверсных значений входных переменных и содержит Wi- ДБЗР71:входовых элементов ИЛИ 26 33 {(Jmr,). Уламенты ИЛИ организованы в групп по элемента в группе Полностью показана только первая группа элементов ИЛИ 26 - 29. Вторая (30,,,., 31) и восьмая 132,..., 33) группы показаны неполностью, а остальные группы не показаны, так как все группы аналогичны по структуре и прин нипу работы. Первые входы всех элементов ИЛИ соединены с выходами блока инвертирования- входных переменных (на первые входы элементов ИЛИ первой группы поступают сигналы X/t, Хд. Xif Щ), а на вторые входы этих элементов поступает программная информация. С2. , С,2. ,) 0 регистра 9. Выходы всех элементов ИЛИ (в частности, выходы элементов ИЛИ первой группы Х , Kt, 1, .1) соединены со входами матрицы элементов И. Таким об разом, с выхода некоторого элемента ИЛ на матрицу элементов И поступает либо прямое значение переменной , либо инверсное значение этой переменной либо 1, В последнем случае переменная Х ( JT ) логически маскируется. Легк видеть, что с точки зрения воздействия на элементы И, матрицы элементов И наличие замаскированной переменной (или ее отрицания) равносильно прерыва нию данной связи, Матрица элементов И 2 (фиг. 6), запрограммированная предложенным способом для обеспечения работы ПЛМ в режиме ОДС-3, служит для вырабтки логических произведений - членов ДНФ и содержит-Е 8 Wi-входных ( h1-4) элементов И 34-41. На входы каждого элемента И поступают сигналы с выходов соответствующей группы элементов ИЛИ второго блока прерывания избыточных связей t Х , х, 1, 1; Xl, 1, Xj 1 1 УЗ. « Х-, - X-j I Х Хз I Xjj л л « Xi Хз -- I Х/2: Xj 1 Хх, X 2. .. Выходы элементов И у -Vgсоединен с первыми входами первого блока прерывания избыточных связей Ю, . I -. Первый блок прерывания избыточных связей 10 служит для селективного прог раммного логического маскирования сигн лов V-i. -VB промежуточных шинах ПЛ И содержит Е)( двухвходовых элемен тов И 42 - 53 (фиг. 7). Улементы И организованы в и 3 группы по элементов в группе. Полностью показана только первая группа элементов И 42 49, Вторая (50,..., 51) и третья, последняя (52,,,, 53) группы показаны неполностью, так как все группы аналогичны по структуре и принципу работы. Первые входы элементов И каждой группы соединены с выходами элементов И первой подматрицы - Vg . На вторые входы элементов И Первого блока прерывания избыточных связей подается программная информация Смаски) С., С.,,,,, 3(14) первого вьиода третьего регист ра масок. Выходы всех элементов И . (в частности выходы элементов И первой группы V, Vj , V , О. О, О, О, О) соединены со входами матриць элементов ИЛИ. Таким образом, с выхода некоторого элемента И на матрицу элементов ИЛИ поступает либо некоторый сигнал Vj I либо О. В последнем случае сигнал . логически маскируется. Легко видеть, что с точки зрения воздействия на элементы ИЛИ матрицы элементов ИЛИ наличие замаскированного сигнала равносильно прерыванию соответствующей свяэа. Матрицы элементов ИЛИ 3 (фиг. 8), запрограммированная предложенным спо-собом для обеспечения работы ПЛМ в режиме ОДС-З , служит для выработки конкре пных значений логических функций и содержит VI -3 Е входньк () элементов ИЛИ 54 - 56. На входь каждого элемента ИЛИ поступают сигналы с выходов соответствующей группы элементов И блока прерывания избыточных связей во второй подматрице ( V f УО. О, О, О, О; О, О, О, V4 . у Уу О; VH , Va V3 V4- V V6 V7 Vg Выходы элементов ИЛИ соединены с первыми входами блока интегрирования выходных переменных 4. Блок инвертирования выходных переменных 4 (фиг. 9) служит для селектив кого программного инвертирования значений функций Z/J, Zj2, 1з которые вьфабатываются матрицей элементов ИЛИ, и состоит из VI 3 двухвходовых сумматоров по модулю два 57 - 59. На первые входы сумматоров поступают выходные сигналы с матрицы элементов ИЛИ Z IZ -j,. На вторые входы сумматоров поступает программная информация (маски) ЛА- проходящая с выходов четвертого регистра масок 12, Выходы сумматоров по модулю два, на каждом нз которых формируется либо t, либо Z|i , подаются к внешнему уст ройству, воспринимающему выходные сиг налы. Предлагаемая ПЛМ работает следующим образом. 9. 9 Сигналы X-t - Хд подаются от источника входных переменных на первые входы блока инвертирования входных переменных (БИ) 6, на вторые входы которого подается арограммная инфор- . мааня (маски) ,. С-),,..., С|(Э2) первого регистра масок 7. В результате сложения по модулю два входных переменных Х и сигналов C.j Д на выходе блока БИ получеиот прямые 1если 0} или инверсные {еслиС11 1) значения входных переменных. В частное ти для того, чтобы ПЛМ работала в качестве ОДС-З, программная информаци fC-ii ,...,Cf),z) быть следующей 0000 ОООО 00000110 1010 НОООООООООО. программная информация подается пареллельным кодом с первого регист ра масок. На выходе блока инвертирования полуШют следующее 32-разрядное 1 2 . 3 4 2... которое подается на первые вкоиы второго; блока прерывания избыточных свя- . Зей (БПр2.) 8. На вторые входы . подается программная информация Cjj.C-iiL «C/i(l.)co второго регистр ра масок 9. В результате происходят логическое маскирование тех двоичных переменных XV ( X)i которые на БПрй логически складываются с единицей, что равносильно прерыванию соответствующей цепи. В частности, для реализации ОДС-3 программная информация С., Саа. ... С(52) должна быть следующей: ООН О1О1 10О1 О001 ОО01 ООО1 Об01 ОООО, Эта программная информация подается параллельным кодом со второго регистра масок, структура которого полностью аналогична структуре первого регистра масок. В основном варианте у обоих регистров совпадает даже разрядность программной информации.. Возможен и второй вариант построения программного инвертирования входных переменных и прерывания их цепей (выбор варианта осуществляется изготовлением ПЛМ и зависит от степени сложности создания на кристалле логических вен- тилей того или иного вида: элементов ИЛИ, элементов И, сумматоров по моду-; лю два). Во втором варианте блок внвертирования и первый регистр масок не нопользуется. Дня реализации ОДС-З программная информация . Са.4..«ч Cfi(y 45 долкна иметь следующий ввя: ООН 1111 01О1 1111 1001 1111 0111 1011 01О1 Ц01 ООН ОО01 1111 0000 ОООО. Она поступает на второй вариант блока прерывания избыточных связей в первой подматрице (БПро. ) Блок БПр/i. отличается от блока БП p-j увеличенным количеством элементов ИЛИ, в БПр, используется шестьдесят четыре элемента ИЛИ, а не тридцать два, как это имеет место в БПр.. В результате с выходов БПрс. для реализации ОДС-3 должна сниматься следующая информация: X 1. И 1111 .1 1111 IXjtX 1 1111 Хн 111 1 XiXo, lXa.llX 1 11 у 1 ifo. 11 1111 С1ХгХ Х4Х,Хг.Хд. информация должна подаваться на « матрицы элементов И а. При этом элементы И, входящие в состав матрады элементов И, должны иметь по входов каждый (как в известном), а не , как в основном варианте предпоже1шой ПЛМ. В основном варианте выходные сигналы БПр2. поступают на входы матрицы элементов И (М ) 2. Информация на входе М имеет следующий вид 1 Xj, Х Xj ),,. если ПЛМ реализует ОДС-З. На выхода М | в результате потетрадной коньюнкдин вхоШой информации получают следукяцие сигналы: . .( Vi x,xt,; .Ь 5 , Vg ,,У4 (Va не используется). При втором варианте построения блока прерывания избыточных связей в его регистра масок требуется иметь матрицу элементов И из элементов И с входами. С выходов матрювм элементов И сигналы -VJg поступают на первые входы первого блока прерывания иабыточн ных связей (БПр ). На вторые входы БПр.) поступает программная информация С). « ) с третьего регистра масок. В результате коньюнкцвв VK в сигналов 1где р 1, 2, 3..., 24) ца выходах бло1ка БП л сформируются либо некоторые значения переменныхif либо, логический нуль. Программная кнформация , С-м, ..- Сз(.2.4)фв реалазацЕги ОДС-3 должна иметь следующий ВйД: 1110 ООО 0001 1110 0000 ООО на выходе БПри сформируется следующий параллельный двоичный код: ОООО ООО 1111О ОООО 0000. Третий регистр масок полностью ана логичен по структуре первому регистру масок, отличаясь от него только разря;. ностью (он должен иметь Е)у,24 разряда). Выходные сигналы БПр/) поступают на 0ХОД матрицы элементов ИЛИ (М,) 3 В результате дизъюнкции октад двоичньк переменных на выходе М. получают сигналы, характерные для ОДС-3: . K X3Vy2X i а- 6 V7--х ,,vX X Х 1УХ 2Хъ 1 2.Х5 (не используется). Выходные сигналы М а подаются на первые входы блока инвертирования выходных переменньсс, на вторые входы которого поступает программная информация , ОФ2. 43- четвертого регнст pa масок 12. В результате сложения по модулю два сигналов Z/j, сигналов €4 ,041,04 на выходе блока инвертирования выходных переменных получают прямые или инверсные значения Z , 2 2-, в зависимости от значений сигналов 040. 4Ъ частном случае, для того, чтобы ПЛМ работала в качестве ОДС-3, программная информация должна быть нулевой ЮОО). Четвертый регистр масок полностью аналогичен по структуре первому регистру, отличаясь от него только разрядностью (он должен иметь разряда). о Поскольку возможны структуры ПЛМ, реализующее булевы функции в других ба зисах, а не только в дизъюнктивной нормальной форме, как это для определеннос ти принято на представленных чертежах . то, очевидно, возможны И другие варианты построения блоков 9, 11 и др. блоков. Так если функции реализуются в КОНЪЮНКТИВНОЙ нормальной форме, то блок 9 представляет из себя линейку элементов И, а блок 11 -линейку элементов ИЛИ. Если функции реализуются в шефферовой нормальной форме, го оба блока 9 и 11 представляют собой линейки элементов ИЛИ. Если функции реализуются в пирсовой нормальной форм то оба блока 9 и 11 представляют собой линейки элементов И и т.д. 1в принципе при проектировании ПЛМ может быть иопользован любой логический базис). Достгажение цели изобретения обусловлено введением дополнительного оборудования. В первую очередь это касается регистров масок. В основном варианте предусмотрено их последовательное соединение, чтобы обеспечить минимум до- полнителы{ых вводов в кристалл. В случае появления возможности увеличить число дополнительньи выводов nporpai мную информацию в регистры можно будет вводить последовательно-параллельно и, в предельном случае, параллельно. Это очень важное обстоятельство, пооКольку появляется возможность настраивать ци Тювые структуры под обрабатываемые алгоритмы в процессе решения задач, что должно резко увеличить эффективность вычислительных средств. Вместе с тем желательно иметь достаточно простые регистры масок, требующие небольшого количества оборудования для своей реализации. Бели реализовать ПЛМ по основному варианту, то емкость памяти регистров должна составлять 1 M2hiE-«-Eli-vn 6wn . Практически параметры современных ПЛМ примерно таковы: 6, , Утг: 8. В этом случае емкость памяти регистров 1,25 кбит. С одаой сторсйы, это не очень много, так как для обработки восьмиразрядных чисел () при помощи ЗУ требуется емкость Vi 64 кбит. Даже при резком снижении разрядности чисел до 4 бит их сложения при помощи ЗУ потребует 5. ,5 кбит. Но с другой стороны, желательно иметь у регистров масок как можно меньшую емкость памяти. В свяаи с этим можно указать неоколько путей упрощения их структур, и следовательно,. уменЙнения их памята не реализовывать возможность инвертирова-. нкя выходных сигналов, в результате чего отпадает необходимость в четвертом регистре масок (инвертирование выходных переменных не реализуется в бол1ьшин-. стве обычных ПЛМ); уменьшить число триггеров в первом и втором регистрах масок за счет уменьшения избыточности оборудования, имеющейся в реализации основного варианта. Количество всех состояний ввода у матрицъ элементов И исчисляется в принципе величиной з так как каждый вход может быть в трех состояниях: прямое значение переменной, инверсное значение переменной. Следова- тельно, дяя хранения требуемой информа ции о состояниях входов нужно иметь емкость памяти регистров A -Eogf2 %ME f,58 WE4HE, что при указанных значени$ х w, Е, 1 составляет веяичину кбит; реапк- зовывать fHsumt на ПЛМ не в тупиковых ДНФ, а в совершенной ДНФ, в результат чего отпадает необходимость во втором регистре масок. В этом случае емкость памяти регистров определяется cooTifoшением . M WE-VWE. I Прк принятых величинах ум, Е, м емкост памяти ,75 кбит; комбинировать два вида программирована - электронное и электрофизическое t путем иережигания). Вновь вводимое оборудование (регист ры. и др.) Ъ значительной части компенс руется тем, что из состава ПЛМ выводится блок пережигания избыточных свя зей. Использование принципа электронного программирования выгодно отличает пред лагаемую ПЛМ от известной, так как значительно упрощается эксплуатация УЕМ и цифровых устройств, повышается ИХ рёмонтоспособность упрощаются вопро сы тестирования и замены неисправных элементов, процесс программирования полностью автоматизируется, время программирования значительно уменьшается, появляется возможность перепрограммирования неверно запрограммирован ных матриц. При достаточно малом врем ни программирования (перепрограммирования/ возможна динамическая настройка цифровых структур в соответствии с ап- горитмами решаемых задач, что приводит к резкому возрастанию эффективно& ти машинньхх вычислений. В определенной степени упрощается процесс изготовления ПЛМ, так как отпадает необходимость в создании фотошаблона для реализации плавких участков связей на кристалле. Появляится возможноств изготовления ПЛМ при любом типе микроэлектронной технологии, даже при таких, в которых пережигание не осуществхряется вообще или значитель но затруднено (например в И Л). Формула изобретения 1, Программируемая логическая матр ца, содержащая матрицу элемеитов И, матрицу элементов ИЛИ, блок инвертирования выходных переменных, первый вход которого соединен с выходом матрицы элементов ИЛИ, а выход является выходом матрицы, и источник синхростжалов, отличающаяся тем, что, с цепью обеспечения возможности перепрограммирования, в нее дополнителысо введены блок инвертирования входных переменных, четыре регистра масок, два. блока прерывания избыточных связей, пpичe : вход матрицы элементов ИЛИ соединен с выходом первого блока прерьюанвя взбыточных связей, первый вход которого соединен с выходом матрицы элементов И, вход которой иоед1шен с выходом второго блока прерывания избыточных связей, первый вход которого соединен с блоком ииве{ тировання входных переменных, первый вход которого является информационным входом матрицы, а второй вход соединен с первым выходом первого. регистра масок, первый вход которого является входом приема масок матрицы, а второй вход первого регистра масок соединен с источником cKHXpoctn-налов и со вторыми входами второго, третьего и четвертого регистров масок, второй выход первого регистра масок соедшен с первым входом второго регистра масок, первый выход которого со вторым входом второго блока прерывания избыточных связей, а второй выход соединен с первым входом третьего регистра масок, первый выход которого соединен со вторым входом первого блока прерывания избыточных связей, а второй выход этого регистра масок соединен с первым входом четвертого регистра масок, выход которого соединен со вторым входом блока инверт{фования выходных переменных. 2.Матрица по п. 1, отличающая с я тем, что первьй блок прерывания избыточных связей состоит из двухвходовых элементов И, первые входы которых соединены с сооаветствующими выходами матрицы элементов И, вторые входь указанных элементов И соединены с первыми выходами третьего регистра масок, а выходы этих элементов И соединены с соответствующими входами ма-ррицы элементов ИЛИ. 3.Матрица по п. 1, о т л и ч а ющ а я с я тем что второй блок прерывания избыточных связей, состоит из двухвходовых элементов ИЛИ, первые входы которых соединены с соответствующнми выходами блока инвертирования входных переменных, вторые входы соединены с первыми выходами второго регистра масок, а вькоды этих элементов соединены с соответствующими входами матрицы элементов И,

-ffffmo t/ ,11,12

фи.г

Cff /

/2

l(H)

фиг.З

S Jf; Г(Г/гг/

Л#, «c/ff/ ДХ// ecAuC sП1, ec/iu ) 0 Х2, ec uCff23)1

f)(it, сс i(s2}0 (,(rc/f /rf/j ; /

(/г, Yfeff/i j (2(29)1 ) Сг(з2)

фиг.5 . Ф Cif29}, Cff29) 0 П , cc/ft/ Qr29}r / J h 1(32), fCAU C2(32) 0 i, C( CC/fU Cf2f32)f

Т

a /

X

ff

,.Гг

fXj

i/3

yif XiXzXj

ye XiXtX}

IfO

gg-Hf ucffs j f f

fiii.6

ui.7

0, sc/in % - Q

HO U/IU

.3

€CAUC(16}1

0, €CAuC()o

//шОГ; ;- D сслиСъ(1)-0

, ,////fW,ef- i/fjf2 ;f|.j

D, €СлиСз(ц/)М

5

У1ЩУУ р

55

.

Zz yifVysvygvy

если Cm - ff если

ССЛУ Citil

Авторы

Даты

1982-06-15—Публикация

1980-06-13—Подача