(Л

.4

00

со

ел

со

СП

Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЭВМ и системах управления технологическими процессами и объектами,

Цель изобретения - уменьшение объема блока, памяти и повьппение коэффициента его использования,

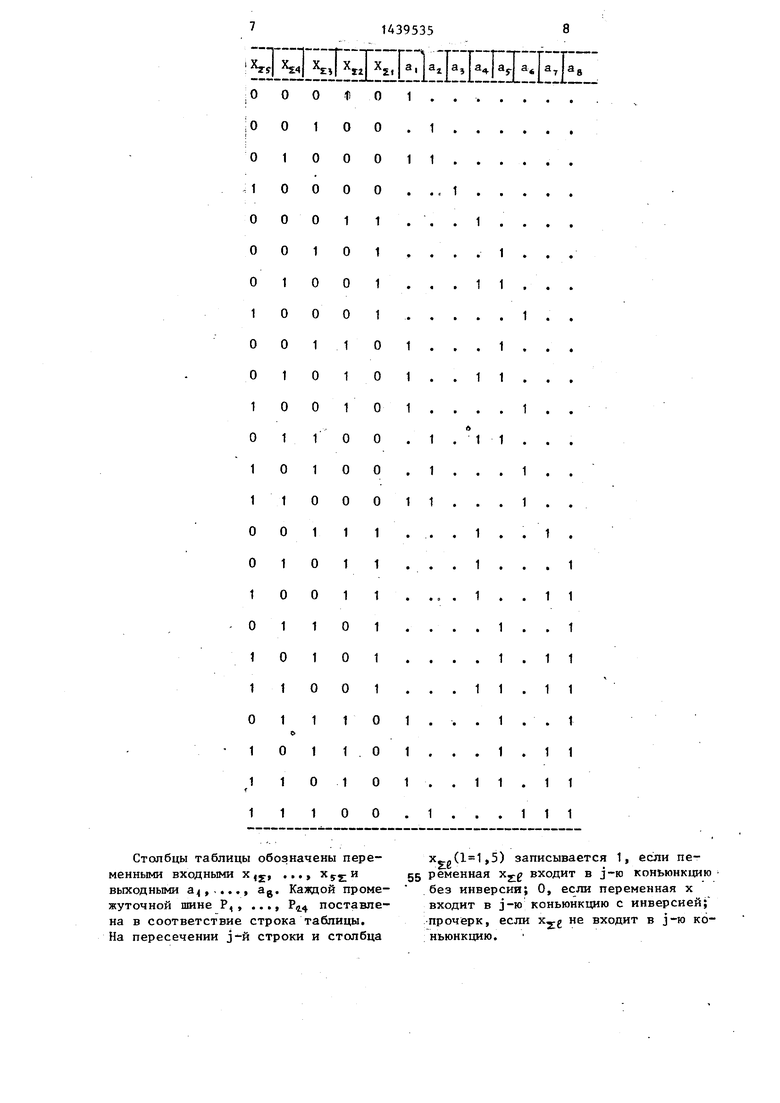

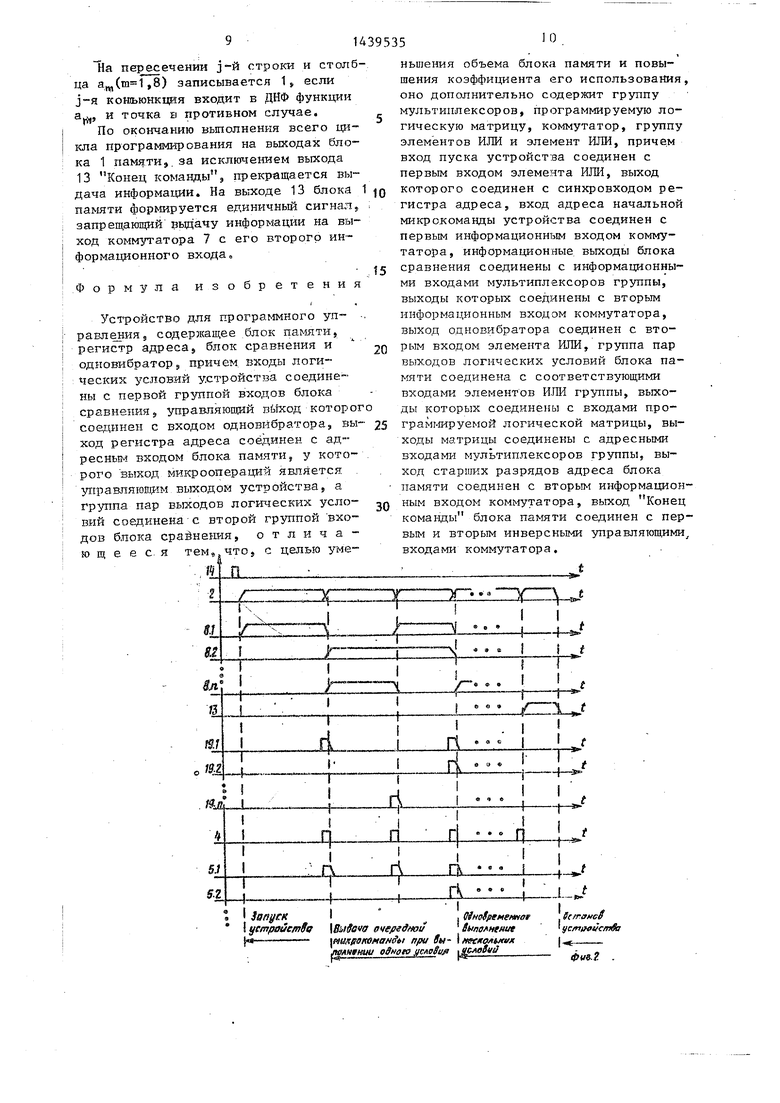

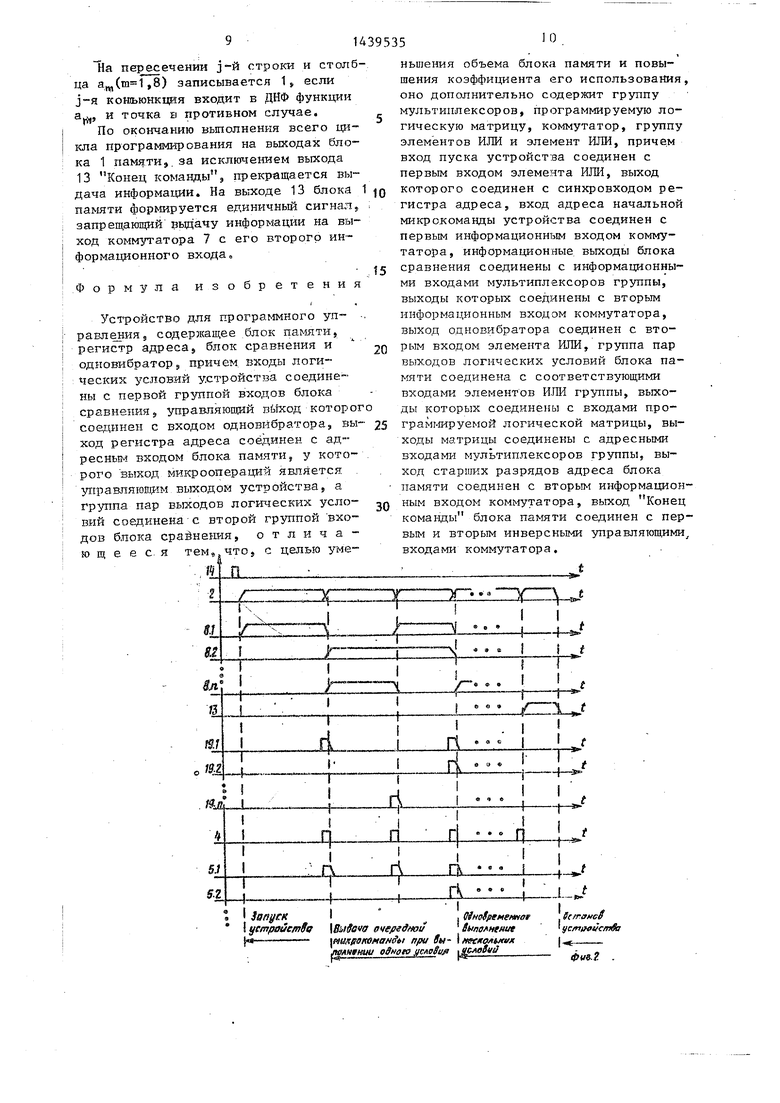

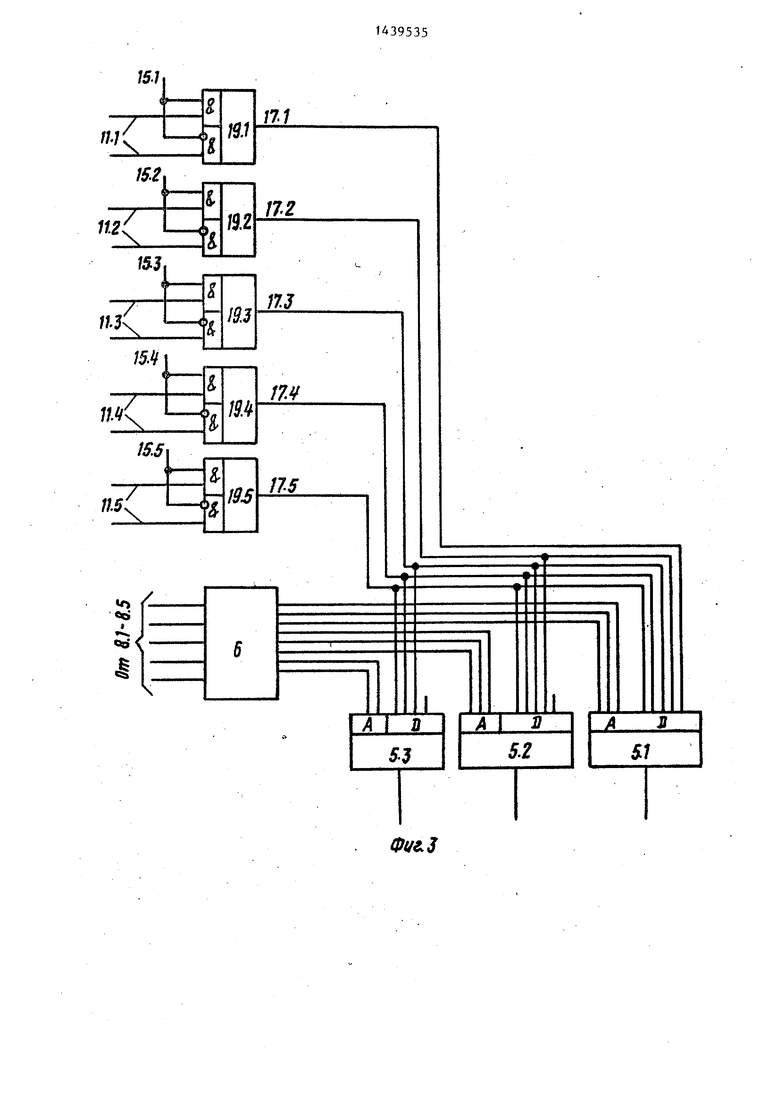

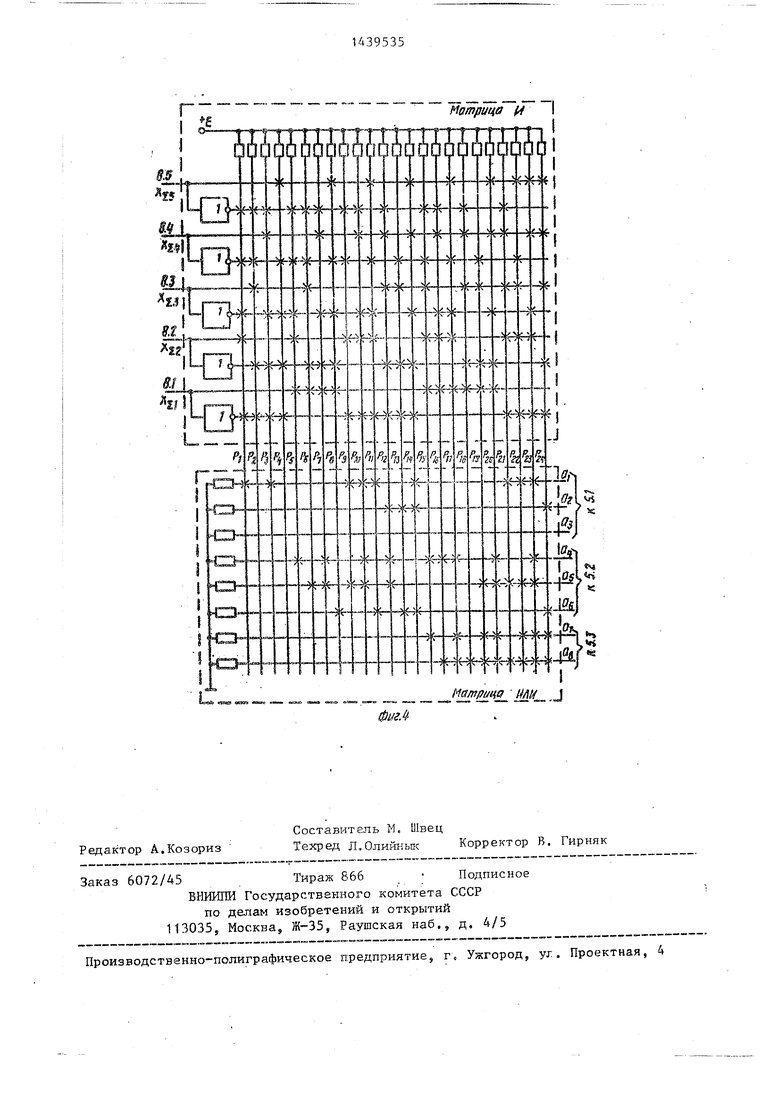

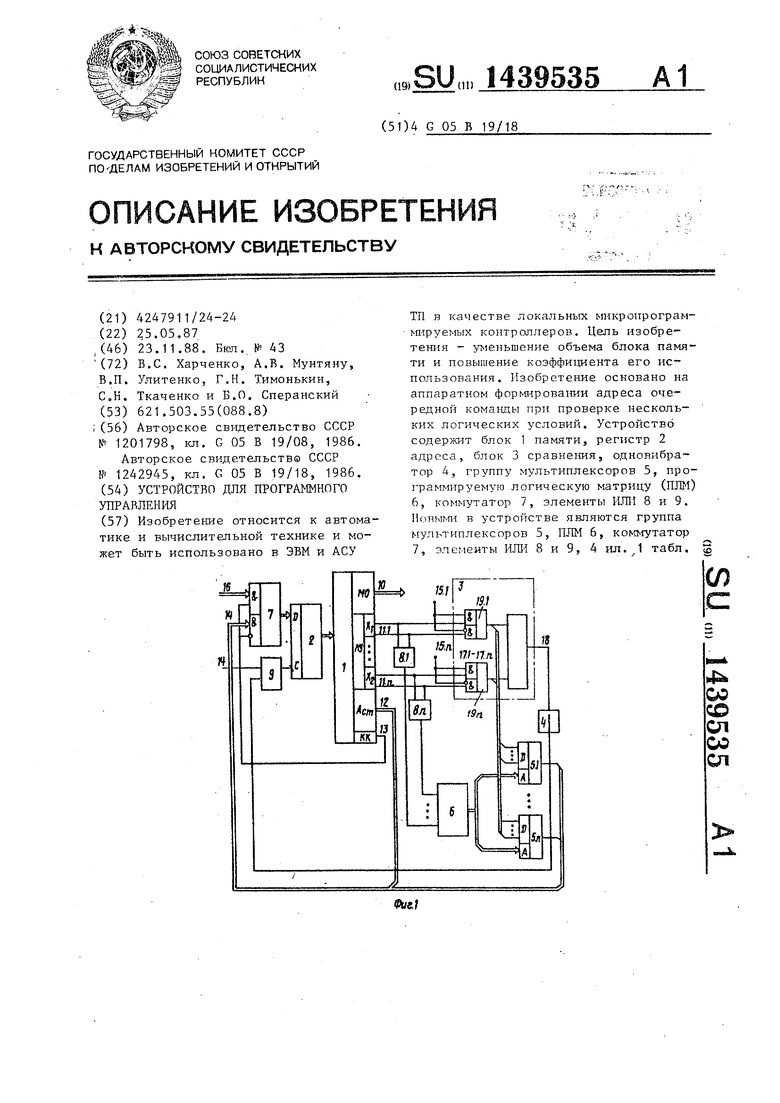

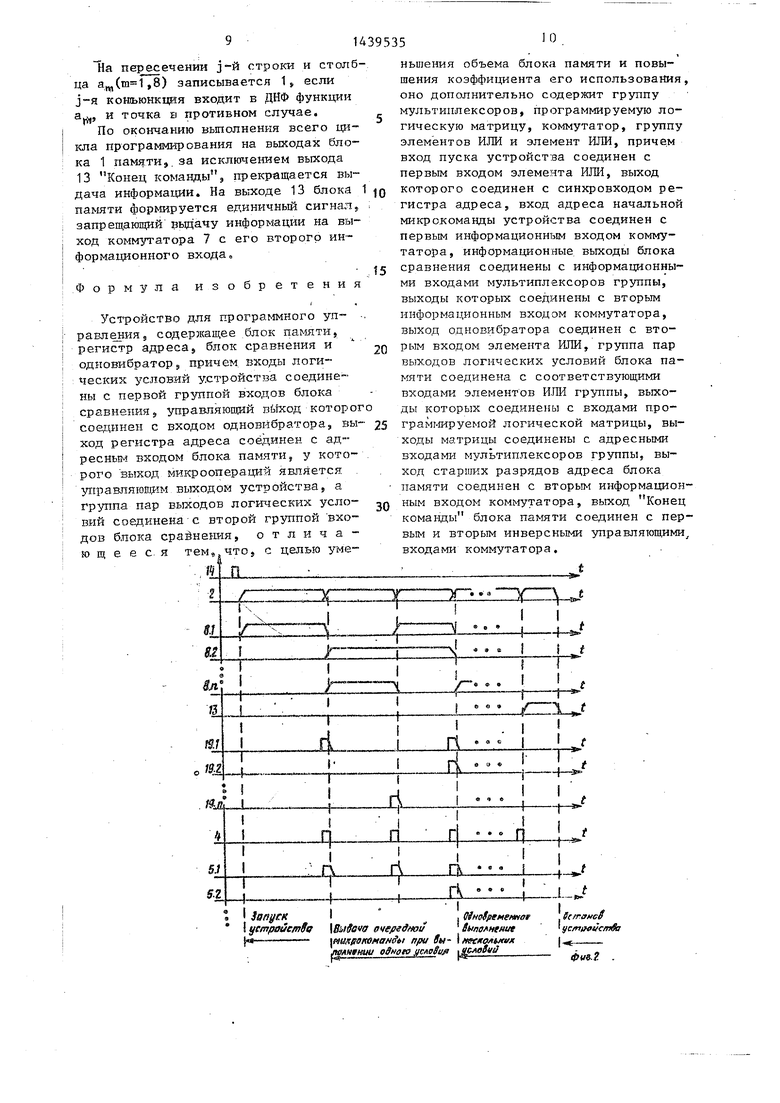

На фиг, 1 приведена функциональна схема устройства5 на фиг 2 временные диаграммы ее работы; на фиг„3 схема соединения информаидонных выходов блока сравнения с информационными входами мультиплексоров группы; .на фиг, 4 схема построения програ- мируемой логической матрицы для конкретного случая

Сущность новой дисциплины функционирования состоит в след,уюш,ем

От устройства верхнего уровня либо от оператора поступает код операции (адрес начальной михсрокоманды) и сигнал на-пуск предлагаемого устройства, ° Адрес очередной микрокоманды формируется в ходе работы устройства: стараше разряды адреса хранятся в . блоке памяти и выдаются при переходе к выполнению очередной микрокоманды;

младшие разряды формируются в ходе

I. ..

проверки логических условий

Количество младших разрядов ад реса очередной макрокоманды значительно меньше, общего количества логических условий, что достигается путем сжатия общего числа разрядов с результатами проверки логических условий до значения, соответствующего максимальному числу отогичес- ких усповий, проверяемых за один шаг пpoгpa {мнoгo управления.

Функциональная схема ус тройства (фиг. 1) содержит блок 1 памяти, регистр 2 адреса, блок 3 сравненияs од новибратор 45 группу мультиплексоров 5„1-5п, nporpstkMHpyeMyro логическую матрицу (ПЛМ) 6, комьтутатор 7, группу элементов ИЛИ .ns элемент ИЛИ 9, вькод 10 микроопераций, группу пар выходов 11,1-11,п логических условий, выход 12 старших разрядов адреса и выход 13 4сонец команды блока 1 памяти, вход 14 пуска устройст- йа, группу входов 15,1-15.п логических условий блока 3, соединенных с (k-1)-ми входами первого и второго мультиплексоров и (k-j+1)-M входом j-ro мультиплексора 5,1-5лг группы,,

0

5

0

5

0

5

0

5

0

5

где 1с 3,п, j 3,п, вход 16. адреса; начальной микрокоманды устройства, информации о иные выходы 17. 1-17,п, выход 18 блока сравнения и элементы 2И-ИЛИ 19,1-19,п.

Пример соединения информационных выходов 17,1-17,п блока 3 сравнения с информационными входами мультиплексоров группы 5,1-5,п по указанному принципу (п 5 - число различных условий, проверяемых в ходе работы устройства; п 3 - максимальное число проверя€;мых логических условий на одном шаге микропрограг-1мирования) показан на фиг, 3.

На фиг. 2-4 использованы обозначения , aj и Ру, а также показаны входные и выходные сигналы и термы для ПЛМ 6.

Назначение основных элементов асинхронного программного устройства управления (фиг, 1) состоит в следующем.

Блок 1 памяти микрокоманд предназначен для хранения микрокоманд, реализуемых устройством, и представляет собой запоминающее устройство статического типа, информация на выходе которого появляется после подачи адреса на его вход и сохраняется на выходе до снятия входного сигнала. На выходе 10 блока 1 памяти считываются сигналы микроопераций, на группе пар выходов 11,1-11 ,п считываются сигналы, определяющие ожидаемое значение х проверяемых логических условий. Если на i-й паре выходов П,1-11,п присутствует код 10, то i-e логическое условие должно быть равно единице, а если 0,1, то нулю, В случае, если некоторое логическое условие не проверяется, на соответствующей ему паре выходов группы пар выходов 1 Kill,п блока 1 присутствует код 00, При вьдаче кода 11 на.i-й паре выходов 11,1-11,п группы блока 1 значение i-ro логического условия может бьп-ь произвольным. На выходе 12 блока 1 памяти считьгеаются старшие разряды адреса очередной микрокоманды, на выходе 13 считывается сигнал Конец команды, свидетельствуюпщй об окон- чании цикла программирования.

Регистр 2 адреса предназначен для приема, .хранения и вьщачи адреса очередной микроманды. Запись адреса, поступающего на D-входы регистра 2 с выхода коммутатора 7, осуществляется по заднему фронту импульса, поступающего на его синхровход с выход элемента ИЛИ 9.

Влок 3 сравнения предназначен дпя сравнения кода логических условий, поступающего на его первую группу входов с входов 15.1-15,п устройства, и проверочного кода с выходов 11.1-11.П блока 1 памяти, поступающего на его вторую группу входов. При совпадении значений логических условий с ожидаемыми на управляющем выходе 18 блока 3 сравнения формируется единичный сигнал, а на информационных выходах 17.1-17.П блока 3 сравнения выдается код, несущий инЬ( ,+ а, У1+ ,

Ч а,у + ...+ а,у +

1А 39535

формацию о результатах проверки логических условий.

Одновибратор А предназначен для формирования сигнала перехода к очередной мIiкpoкoмaндe при поступлении на его вход единичного сигнала с выхода злемента ИЛИ 9.

Группа мультиплексоров 5.1-5.тГ предназначена для формирования младших разрядов адреса очередной ми1фо- комавды, п « п.

Выходные сигналы мультиплексоров 5.1-5.П определяются функциями

а,-у,Ч, +...+ а,1, у„ . + а, у-, + ...+ а,,, у„;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Устройство для контроля схем сравнения | 1984 |

|

SU1218386A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Асинхронное устройство для программного управления | 1987 |

|

SU1481712A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1471190A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЭВМ и АСУ ТП в качестве локальных микропрограм- шруемых контроллеров. Цель изобре- теш1я - ,т 1еньшение обьема блока памяти и повышение коэффициента его использования. Изобретение основано на аппаратном формировании адреса очередной комавды при проверке нескольких логических условий. Устройство содержит блок 1 памяти, регистр 2 адреса, блок 3 сравнения, одновибра- тор 4, группу мультиплексоров 5, программируемую логическую матрицу (ПЛМ) 6,коммутатор 7, элементы ИЛИ 8 и 9. lloны ш в устройстве являются группа мультиплексоров 5, ПЛМ 6, кo t fyтaтop 7,элементы ИШ 8 и 9, 4 ил.1 табл. §

.bk а,ук+ , + ... + .-, Уп,

где у

.у - результаты проверки логических условий; - коньюнкции сигналов а,- , поступающих на адресны входы мультиплексоров 5.1-5.Г1 с выхода матрицы 6;

. «.

/ч

а- а,

ПЛМ 6 предназначена для формирования в зависимости от количества и вида проверяемых логических условий сигналов, управляющих работой мультиплексоров 5.1-5.П группы. Коли- чество входов матрицы 6 определяется общим количеством различных условий, которые подлежат проверке.

Число ее выходов определяется из соотношения

т flog J,Z.rioi 2(1-))1.

где 1: - число информационных входов j-ro мультиплексора 5.1- 5.П rpynrfii.

Коммутатор 7 предназначен для коммутации на вход регистра 2 адреса очередной микрокоманды и осуществляе передачу на D-вход регистра 2 одного из двух адресов, поступающих на его первый и второй информационные входы соответственно адреса начальной микрокоманды и текущего адреса очередной микрокоманды,

о

5

0

5

0

5

Управление коммутатором 7 осуществляется сигналом, поступающим с выхода 13 блока 1 памяти на его первьй и второй инверсньй управляющие входы. Если на выходе 13 блока 1 нуле вой сигнал, то на выход коммутатора 7 : проходит теку111ий адрес очередной микрокоманды. Если на выходе 13 блока 1 единичный сигнал, то на выход коммутатора 7 проходит адрес начальной микрокоманды.

Группа элементов ИЛИ 8.1-8.П предназначена для формирования кода, несущего в себе информацию о количестве и видах проверяемых на каткдом этапе программного управления логических условий. Этот код, поступая на входы матрицы 6, определяется формирование сигналов на ее выходах.

Пред емое устройство управления работает следующим образом.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии, за исключением разряда блока 1 памяти, соответствующего выходу 13 блока (цепи установки исходного состояния устройства не по- казаны). Единичный сигнал с выхода. МЗ блока 1 памяти поступает на управляющие входы коммутатора 4, чем .обеспечивается коммутация на выход коммутатора А его первого информационного входа. По сигналу Пуск

с входа 14 устройства на выходе.элемента ИЛИ 9 формируется импульс, по заднему фронту которого в регистр 2 адреса записывается адрес начальной микрокоманды с входа 16 устройства По поступлению этого адреса на вход блока 1 памяти на его выходах 10 и 12 и группе пар выходов 11,,п появляется информация, соответству- клцая начальной микрокоманд-е На выходе 13 блока 1 памяти единичный сигнал отс;утствует. При работе устройства возможна одновременная проверка не более п логических условий. Проверка соответствия значений логических условий олсидаемым- осуществляется в блоке 3 сравнения группой элементов 2И-ИЛИ 19,,п„ Выходной си1 на.п элемента 2И-ИЛИ 19„1-19,п группы определяется функ дней,

y... х;. „

где ., первый (второй)- выход пары выходов 11, I 11,п грьттпы блока 1 памяти;

к.- значе €ие i-ro логическо- 1

го условрш о

По окончаш-по проверки логических условий на выходе 18 блока 3 сравнения формируется единичный сигналs по ступающий на вход одновибратора 4„ Поэтому сигналу одновибратор 4 формирует импульс, по заднему фронту которого в регистр 2 адреса заносится адрес очередной микрокомавды с второго информационного входа коммутатора 7,

Текушяй адрес очередной микрокоманды формируется следующим образом. Старшие разрядь адреса записаны в блоке 1 памяти и поступают на второй информационный вход коммутатора с выхода 12 блока 1 без изменения. Младипие разряды адреса очередной г-ш- крокоманды пос упают на второй информационный вход коммутатора 7 с выходов мультиплексоров 5.1-5.П Количество младших разрядов адреса определяется максимальным числом одновременно проверяемых логических условий п. Это достигается сжатием

п-разрядного кода, присутствующего на выходах 17.1-17.п блока 3 сравнения до п разрядов. При проверке одного любого логического условия изменяется лишь самьй младший разряд адреса, при проверке двух любых логических условий возможно изменение одного из двух либо обоих сразу

младших разрядов адреса. Аналогичным образом модификация младших разрядов происходит и далее. При проверке п логических условий возможно изменение всех разрядов адреса. Какое логическое условие оказывает

влияг-ше на модификацию того или иного младшего разряда адреса очередной микрокоманды определяется сигналами, присутствующими на адресных входах

мультиплексоров 5,Т-5.0 группы. Эти сигналы формируются ПЛМ 6 в зависимости от кода, поступающего на ее входы с выходов элементов ИЛИ 8.1-8,п группы.

На фиг, 4 представлена ПЛМ 6 для слт. чая, когда п , полученная соединением матрицы И, имеющей десять горизонтальных шин и двадцать четыре вертикальных шины, и матРИДЫ РШИ, имеющей двадцать четыре вертикальных шины и восемь горизонтальных шин. Количество горизонтальных шин матрицы И определяется удвоенным числом проверяемых логических

условий (используются прямые и инверсные значения логических условий). Количество горизонтальных шин матрицы ИЛИ обусловлено числом адресных разрядов мультиплексоров 5,1-5.п группы.

Так как п 3, следовательно, используются три мультиплексора (фиг. 3) со следующим количеством адресных разрядов: первый - три (пять информационных входов), второй - три

(пять информационных входов), третий - два (четыре информационных входа).

Число вертикальных тин обеих матриц определяется копичеством различных ковьюнкций вход ных переменных, полученных в результате совместной минимизации выходных функций.

Алгоритм работы матрицы 6 (фиг. 4) услойно изображен в виде таблицы.

Столбцы таблицы обозначены пере- (,5) записывается 1, если пеменными входными х,, .,., х -иgg ременная х входит в j-ю коньюнкцию

выходными а,-..., а. Каяздой проме- без инверсия; О, если переменная х жуточной шине Р, , ..., Р поставле- входит в j-ю конъюнкцию с инверсией; на в соответствие строка таблицы. прочерк, если не входит в j-ю к6- На пересечении строки и столбца ньюнкцию.

На пересечении j-й строки и столбца а„,(,8) записывается U если j-я конъюнкция входит в ДНФ функции а., и точка в противном случае.

По окончанию выполнения всего цикла программирования на выходах блока 1 памяти,, за исключением выхода 13 Конец команды, прекрйщается выдача информации. На выходе 13 блока памяти формируется единичный сигнал, запрещающий рьщачу информации на выход коммутатора 7 с его второго информационного входа.

.Формула изобретения

Устройство для программного уп , авленияэ содержащее .блок памяти, егистр адресаJ блок сравнения и 20 одновибратор J причем, входы логи- ческих условий устройства соединены с первой группой входов блока сравненияJ управляющий вЫход которого соединен с входом одновйбратора, вы- 25 ход регистра адреса соединен с ресньш входом блока памяти, у кото- . рого выход микроопераций является управляюпщм выходом устройства, а группа пар выходов логических уело- о ВИЙ соединена-с второй грзшпой входов блока сраёнеЕия, о т л и ч а - ю щ е е с. я тем,что, с целью уме, I Запуск I, 01нд$1яненнвг

I ycmpiKieirtSy Щ19оч1 вчерг мои Suno Htnut

|«1 ( при 8ы-

млнвтш ввнокyMoSufl ,afju lve}

Q

5

0 5 о

ньшения объема блока памяти и повышения коэффициента его использования, оно дополнительно содержит группу мультиплексоров, программируемую логическую матрицу, коммутатор, группу элементов ИЛИ и элемент ИЛИ, приче.м вход пуска устройства соединен с первым входом элемента ИЛИ, выход которого соединен с синхровходом регистра адреса, вход адреса начальной микрокоманды устройства соединен с первым информационным входом коммутатора, информационные выходы блока сравнения соединены с информационными входами мультиплексоров группы, выходы которых соединены с вторым информационным входом коммутатора, выход одновйбратора соединен с вторым входом элемента ШШ, группа пар выходов логических условий блока памяти соединена с соответствующими входами элементов И.ГШ группы, выходы которых соединены с входами про- грамг-шруемой логической матрицы, выходы матрицы соединены с адресными входами мультиплексоров группы, выход старших разрядов адреса блока памяти соединен с вторым информационным входом коммутатора, выход Конец комагады блока памяти соединен с первым и вторым инверсными управляющими входами коммутатора.

SaraHcS yc/nitfufmSa

Фив. .

Ф1/г.З

| Устройство для программного управления | 1984 |

|

SU1201798A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1242945A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-11-23—Публикация

1987-05-25—Подача