(54 ) ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1980 |

|

SU935945A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Программируемое устройство для вычисления логических функций | 1987 |

|

SU1444744A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| Программируемая логическая матрица | 1989 |

|

SU1695383A1 |

| СПОСОБ ТЕСТОПРИГОДНОЙ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2008 |

|

RU2413282C2 |

Изобретение относится к вычисли тельной технике и может использоваться в вычислительных устройствах и приборах цифровой автоматики для , микропрограмм, кодопреобразования и реализации управляющих, арифметических и логических комбинационных устройств.

Известно устройство, содержащее матрицу элементов И, матрицу элементов ИЛИ, регистры масок, блоки прерывания избыточных связей и инверторы .1.

Недостатком этого устройства является сложность организации арифметических операций.

Наиболее близким техническим решением к предлагаемо му является программируемая логическая матрица, содержащая подматрицу формирования логических произведений, подматрицу . формирования выходных слов и блок инвертирования входных переменных .

Недостатки известного устройства состоят в ограниченных функциональ- ных возможностях вследствие сложности выполнения операции сложения -И невозможности построения на его основе многоразрядного сумматора.

Цель изобретения - расширение функциональных возможностей программируемой логической матрицы путем выполнения в ней арифметических операций .

Поставленная цель достигается тем, что В: программируеглую логическую матрицу, содержащую элементы НЕ, матрицу элементов И и матрицу элемен10тов ИЛИ, выходы которой являются одними из выходов программируемой логической матрицы, а входаа подключены к выходам матрицы элементов И, входы которой соединены с выходами

15 элементов НЕ, введены логический блок и блок местного управления, выходы которого подключены к одним из входов логического блока,, другие входы которого соединены с одними

20 из входов блока местного управления и являются информационньа и входаМи программируемой логической матрицы, управляющими входами которой являются другие входы блока местного

25 управления, выходы логического блока подключены к входам элементов НЕ и являются другими выходами программируемой логической матрицы.

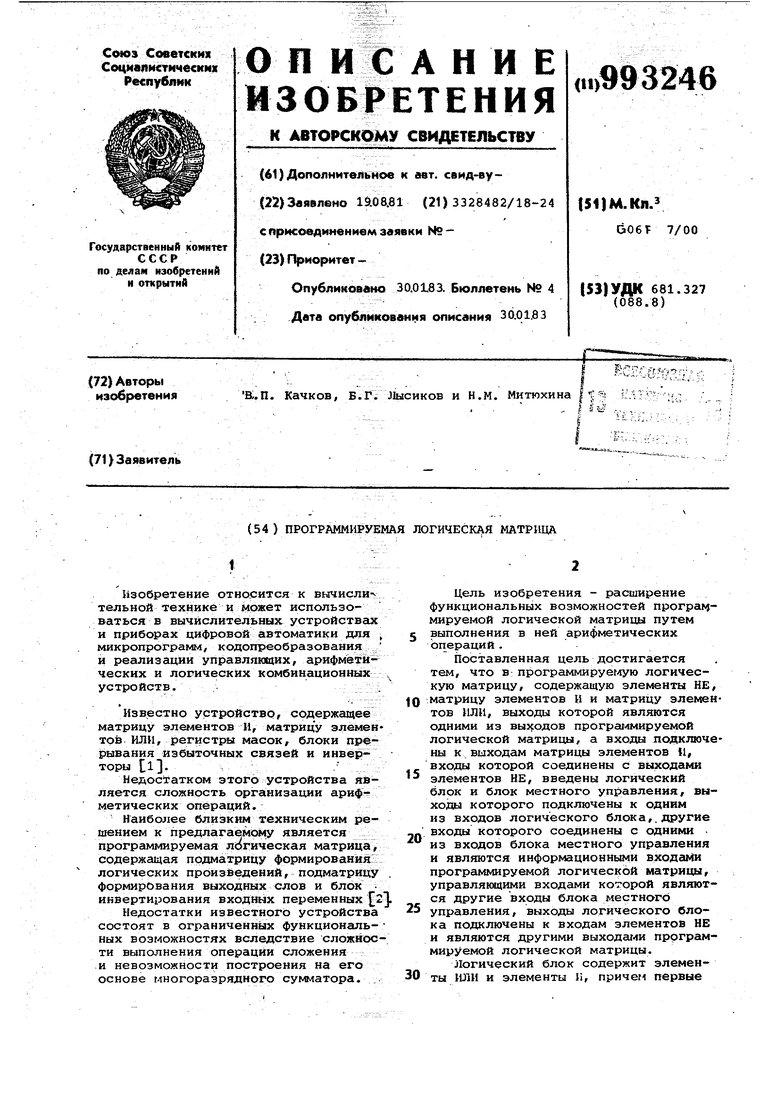

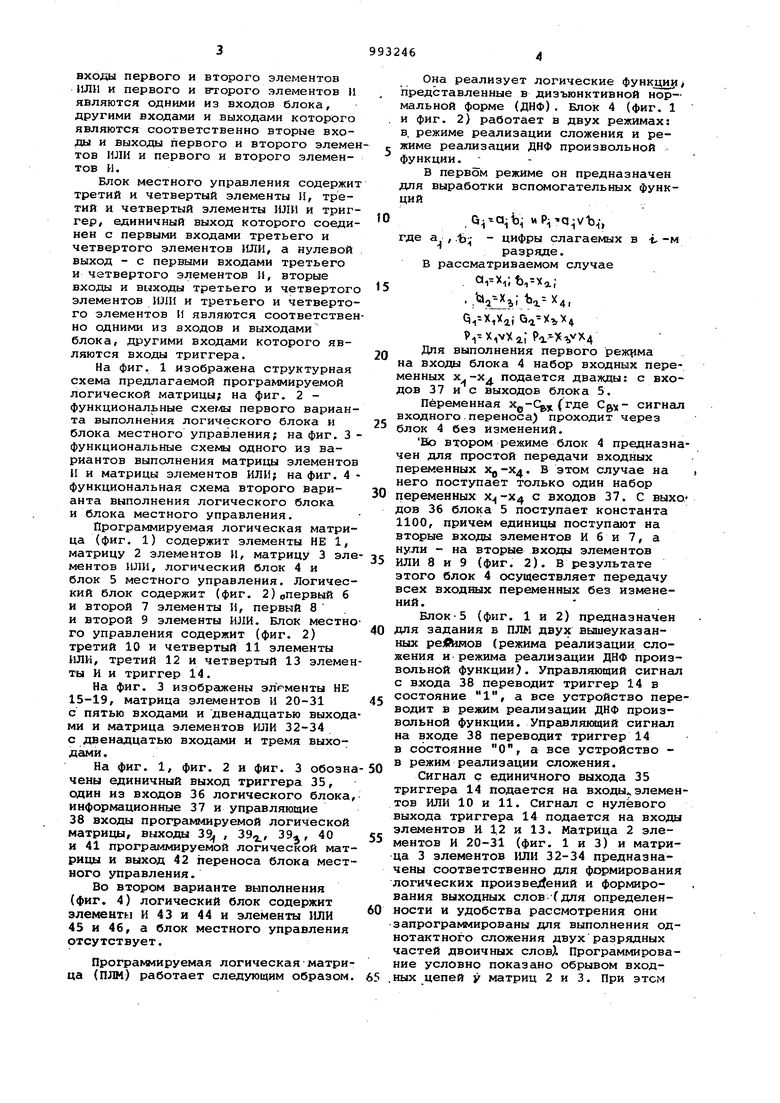

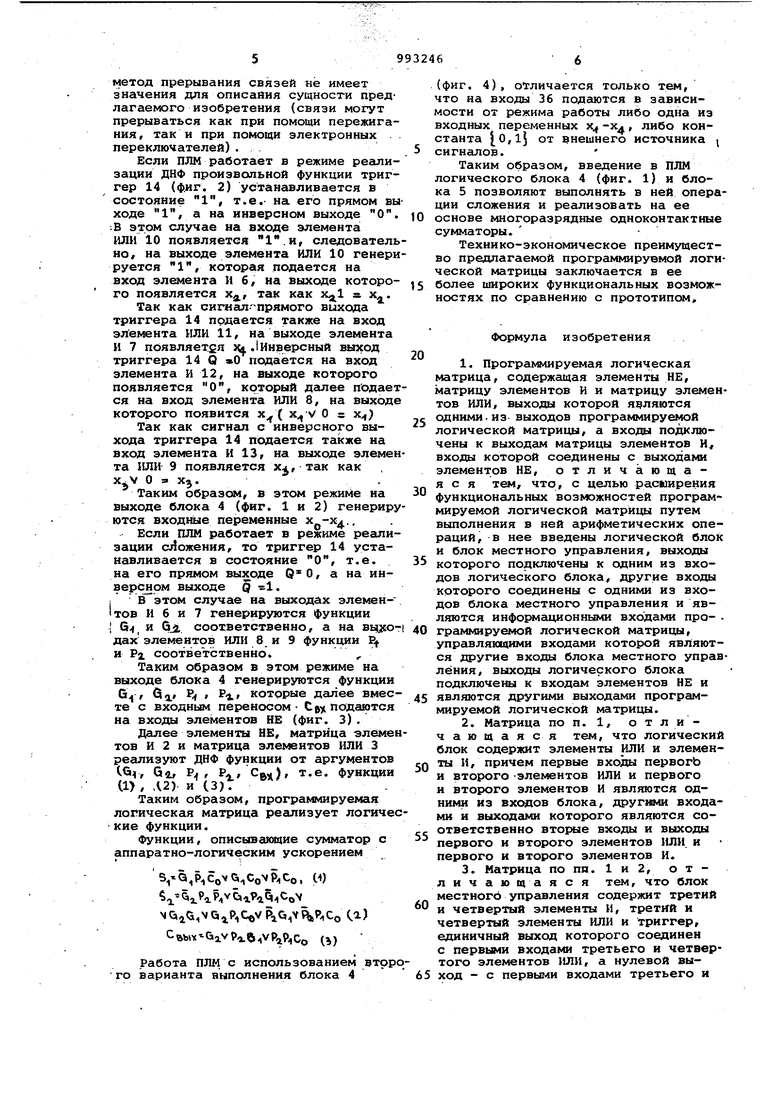

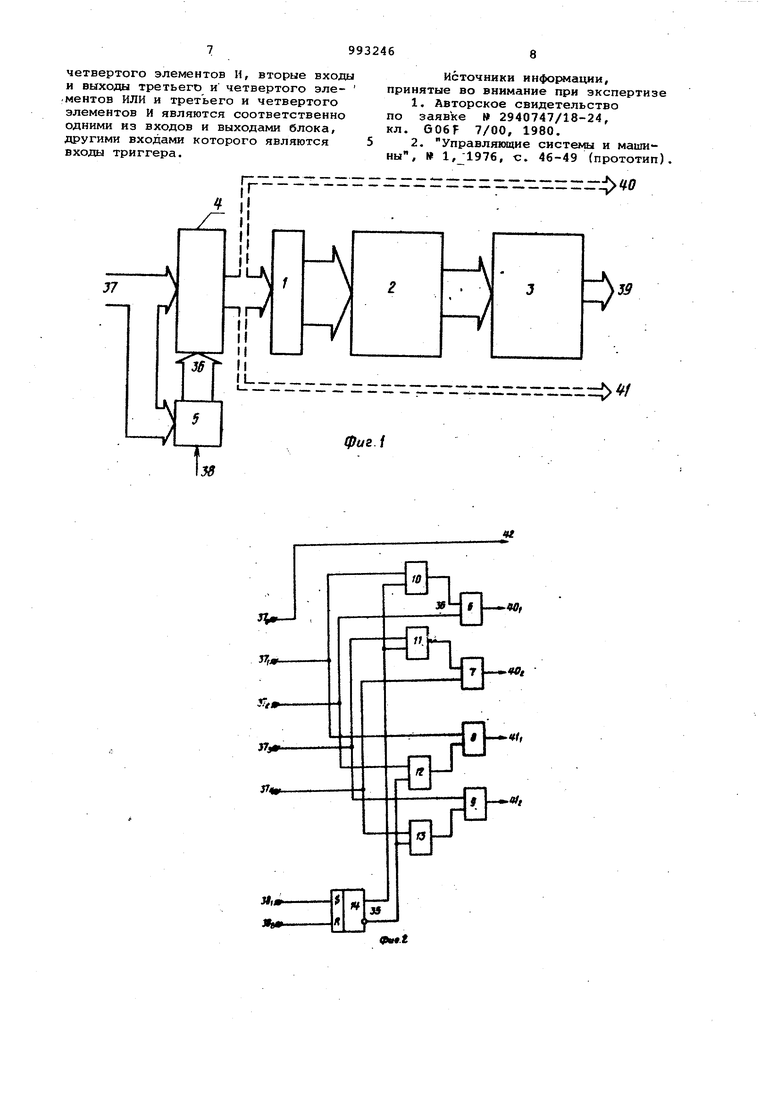

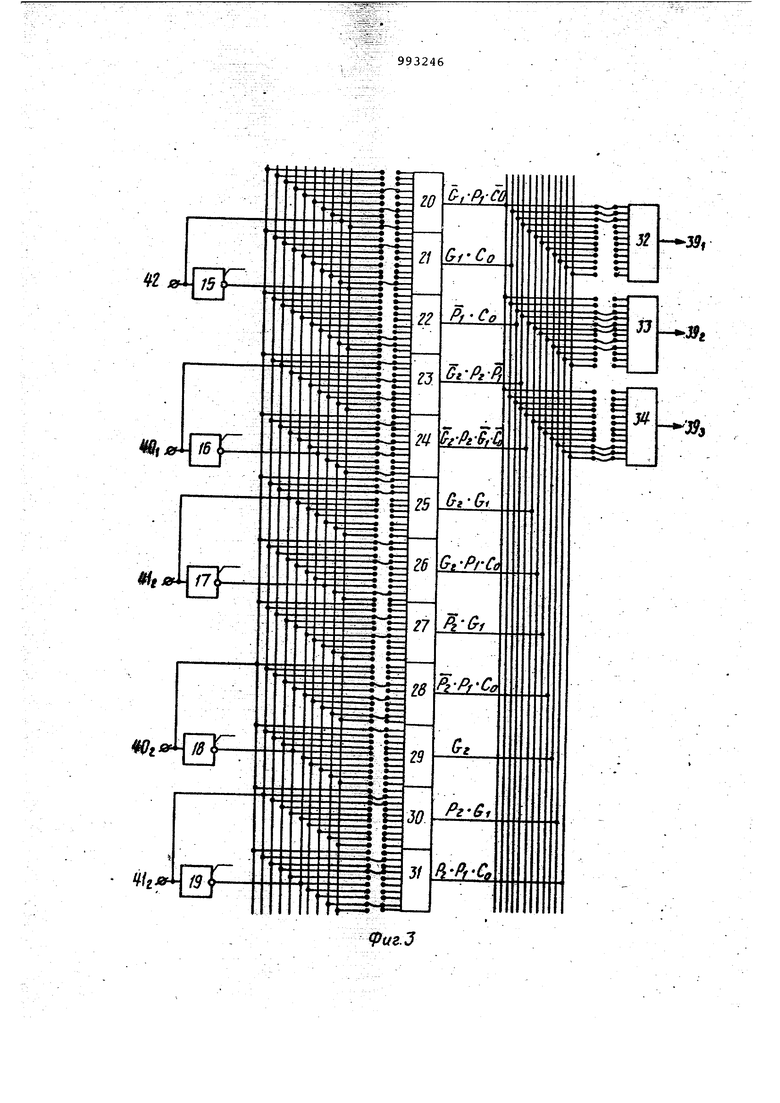

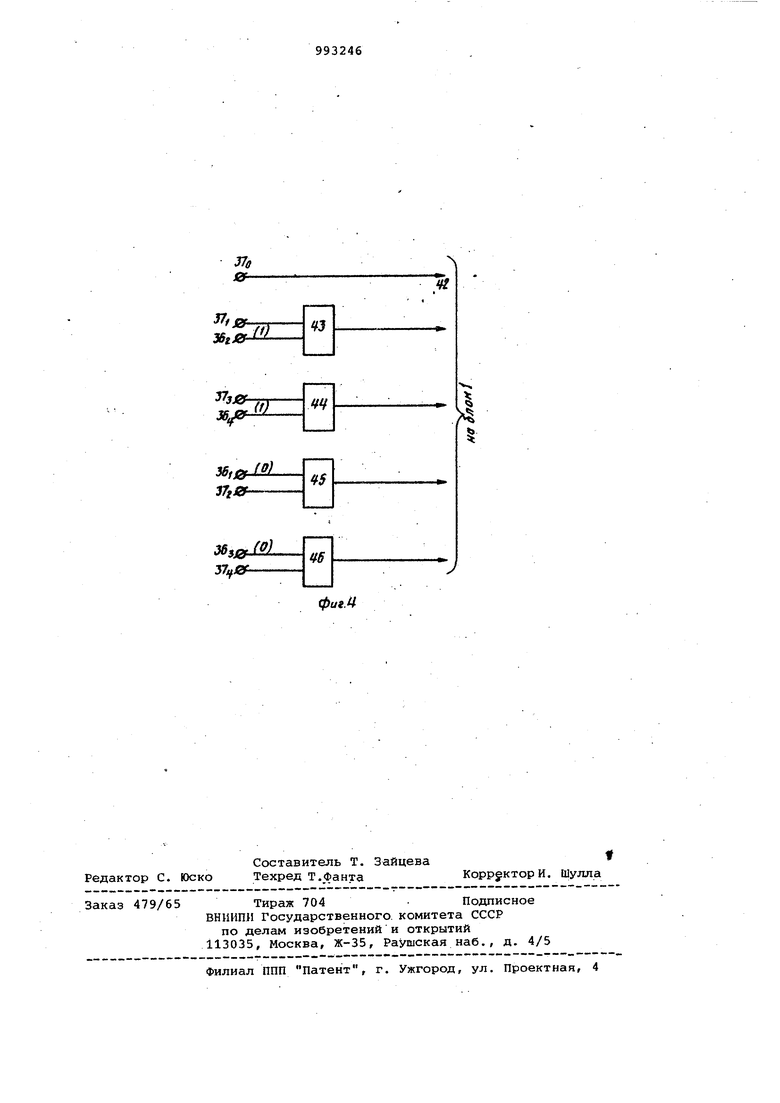

Логический блок содержит элемен30ты ИЛИ и элементы li, причем первые входы первого и второго элементов ИЛИ и первого и второго элементов 11 являются одними из входов блока, другими входами и выходами которого являются соответственно вторые входы и выходы первого и второго элемен тов ИЛИ и первого и второго элементов И. Блок местного управления содержит третий и четвертый элементы И, третий и четвертый элементы НЛН и триггер, единичный выход которого соединен с первыми входами третьего и четвертого элементов ИЛИ, а нулевой выход - с первыми входами третьего и четвертого элементов и, вторые входы и выходы третьего и четвертого элементов ИЛИ и третьего и четвертого элементов И являются соответствен но одними из входов и выходами блока, другими входами которого являются входы триггера. На фиг. 1 изображена структурная схема предлагаемой программируемой логической матрицы; на фиг. 2 функциональные схеглы первого варианта выполнения логического блока и блока местного управления; на фиг. 3 функциональные схемы одного из вариантов выполнения матрицы элементов И и матрицы элементов ИЛИ; на фиг. 4 функциональная схема второго варианта выполнения логического блока и блока местного управления. Программируемая логическая матрица (фиг. 1) содержит элементы НЕ 1, матрицу 2 зле 4ентов И, матрицу 3 эле ментов ИЛИ, логический блок 4 и блок 5 местного управления. Логический блок содержит (фиг. 2)опервый б и второй 7 элементы И, первый 8 и второй 9 элементы ИЛИ. Блок местно го управления содержит (фиг. 2) третий 10 и четвертый 11 элементы ИЛИ, третий 12 и четвертый 13 элемен ты И и триггер 14. На фиг. 3 изображены элементы НЕ 15-19, матрица элементов И 20-31 с пятью входами и двенадцатью выхода ми и матрица элементов ШШ 32-34 с двенадцатью входами и тремя выходами . На фиг. 1, фиг. 2 и фиг. 3 обозн чены единичный выход триггера 35, один из входов 36 логического блока информационные 37 и управляющие 38 входы программируемой логической матрицы, выходы 3 , 39, 39, 40 и 41 пpoгpa.lмиpyeмoй логической мат рицы и выход 42 переноса блока мест ного управления. Во втором варианте выполнения (фиг. 4) логический блок содержит элемента И 43 и 44 и элементы ИЛИ 45 и 46, а блок местного управления отсутствует. Программируемая логическая матри ца (ПЛМ) работает следующим образом Она реализует логические функции представленные в дизъюнктивной нор- мальной форме (ДНФ). Блок 4 (фиг. 1 и фиг. 2) работает в двух режимах: в, режиме реализации сложения и режиме реализации ДНФ произвольной функции. В первом режиме он предназначен для выработки вспомогательных функций .Qi-Oibi , где а , .fc- - цифры слагаемых в i, -м разряде. В рассматриваемом случае . .; 4( ( i--XiVX2.; Po.-)(vX4 Дпя выполнения первого режима на входы блока 4 набор входных переменных X.-Хд подается дважды: с входов 37 и с выходов блока 5. Переменная (где сигнал входного.переноса) проходит через блок 4 без изменений. Во втором режиме блок 4 предназначен для простой передачи входных переменных . В этом случае на , него поступает только один набор переменных с входов 37. С выхо дов 36 блока 5 поступает константа 1100, причем единицы поступают на вторые входы элементов И 6 и 7, а нули - на вторые входы элементов или 8 и 9 (фиг. 2). В результате этого блок 4 осуществляет передачу всех входных переменных без изменений. Елок-5 (фиг. 1 и 2) предназначен для задания в ПЛМ двух вышеуказанных pejftiMOB (режима реализации сложения и режима реализации ДНФ произвольной функции). Управляющий сигнал с входа 38 переводит триггер 14 в состояние 1, а все устройство переводит в режим реализации ДНФ произвольной функции. Управлякяций сигнал на входе 38 переводит триггер 14 в состояние О, а все устройство в режим реализации сложения. Сигнал с единичного выхода 35 триггера 14 подается на входы,, элементов ИЛИ 10 и 11. Сигнал с нулевого выхода триггера 14 подается на входы элементов И 12 и 13. Матрица 2 элементов И 20-31 (фиг. 1 и 3) и матрица 3 элементов ИЛИ 32-34 предназначены соответственно для формирования логических произведений и формирования выходных слов fдля определенности и удобства рассмотрения они запрограммированы для выполнения однотактного сложения двух разрядных частей двоичных слов). Программирование условно показано обрывом входных цепей у матриц 2 и 3. При этом

метод прерывания связей не имеет значения для описания сущности предлагаемого изобретения (связи могут прерываться как при помощи пережигания, так и при помощи электронных переключателей).

Если ПЛМ работает в режиме реализации ДНФ произвольной функции триггер 14 (фиг. 2) устанавливается в состояние 1, т.е.- на его прямом выходе 1, а на инверсном выходе О. .В этом случае на входе элемента ИЛИ 10 появляется 1.и, следовательно, на выходе элемента ИЛИ 10 генерируется 1, которая подается на вход элемента И 6, на выходе которого появляется х,, так как s х.

Так как сигнал-прямого выхода триггера 14 подается также на вход элемента ИЛИ 11, на выходе элемента И 7 появляется }ц, Инверсный выход триггера 14 Q 0 подается на вход элемента И 12, на выходе которого появляется О, который далее подается на вход элемента ИЛИ 8, на выходе которого появится х( О

Так как сигнал с инверсного выхода триггера 14 подается также на вход элемента И 13, на выходе элемента ИЛИ 9 появляется х, так как , О и хз..

Таким образом, в этом режиме на выходе блока 4 (фиг. 1 и 2) генерируются входные переменные х -x..

Если ПЛМ работает в режиме реализации сложения, то триггер 14 устанавливается в состояние О, т.е. на его прямом выходе Q О, а на инверс рм выходе Q «1. j в этом случае на выходах элементов И 6 и 7 генерируются функции f G, и Gjt соответственно, а на выцсодах элементов ИЛИ 8 и 9 функции Е|. и PI соответственно. ,

Таким образом в этом режиме на выходе блока 4 генерируются функции G , Оз, Р , Р, которые далее вместе с входным переносом подаются на входы элементов НЕ (фиг. 3).

Далее элементы НЕ, матрица элементов И 2 и матрица элементов ИЛИ 3 реализуют ДНФ функции от аргументов а, Р Р« См), т.е. функции Ш, Л2) иЧЗ). .

Таким образом, программируемая логическая матрица реализует логические функции.

Функции, описывающие сумматор с аппаратно-логическим ускорением

, О)

. NCjaU VQ PiCeVPiO..Co U)

,aVPa.,Co (%)

Работа ПЛМ с использованием второго варианта выполнения блока 4

, (фиг. 4), отличается только тем, что на входы 36 подаются в зависимости от режима работы либо одна из входных переменных , либо константа 0,l5 от внешнего источника

сигналов.

Таким образом, введение в ПЛМ логического блока 4 (фиг. 1) и блока 5 позволяют выполнять в ней операции сложения и реализовать на ее

основе многоразрядные одноконтактные сумматоры.

Технико-экономическое преимущество предлагаемой программируемой логической матрицы заключается в ее

более широких функциональных возможностях по сравнению с прототипом.

Формула изобретения

которого подключены к одним из входов логического блока, другие входы которого соединены с одними из входов блока местного управления и являются информационными входами про-

граммируемой логической матрицы,

управляющими входами которой являются другие входы блока местного управления, выходы логического блока подключеиы к входам элементов НЕ и

являются другими выходами программируемой логической матрищл.

и четвертый элементы И, третий и четвертый элементы ИЛИ и триггер, единичный выход которого соединен с первыми входами третьего и четвертого элементов ИЛИ, а нулевой выход - с первы1 ш входами третьего и

четвертого элементов Н, вторые входы и выходы третьего и четвертого элементов ИЛИ и третьего и четвертого элементов И являются соответственно одними из входов и выходами блока, другими входами которого являются входы триггера.

Источники информации, принятые во внимание при экспертизе

иг.З

JJo

efN.

41

31 i0.

Ж

36tjer 30HL

x

Iff)

36,0. У7г036 jS M,

Щ0.

Авторы

Даты

1983-01-30—Публикация

1981-08-19—Подача