(5) УСТРОЙСТВО ПОСТОЯННОГО ЗАПАЗДЫВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Корреляционный измеритель времени запаздывания | 1983 |

|

SU1160433A1 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Статистический анализатор конечной разности фазы | 1986 |

|

SU1328763A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Цифровой измеритель электрической энергии многофазной сети | 1988 |

|

SU1647443A1 |

| Генератор псевдослучайных узкополосныхСигНАлОВ | 1979 |

|

SU840897A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

I

Изобретение относится к автоматике и вычислительной технике.

Известно устройство, содержащее блок управления, два реверсивных счетчика, блок сравнения, два вентиля, инвертор, генератор тактовых импульсов, блок установки задержки, при этом выход генератора тактовых импульсов через первый вентиль соединен со счетными входами введенных реверсивных счетчиков, выход первого из которых соединен с управляющим входом регулируемой линии задержки и дополнительным выходом дешифратора, выход блока измерения периода через второй вентиль соединен с установочным входом второго реверсивного счетчика, выход которого соединен с входом блока сравнения, второй вход которого подключен к выходу блока установки задержки,один выход блока сравнения соединен с входами направления счета реверсивных счетчиков, другой выход - с управляющим

входом первого вентиля и через инвертор с управляющим входом второго вентиля, один выход блока управления соединен с управляющим входом второго вентиля, а другой выход - с дополнительным входом элемента HUHtl Однако это устройство характеризуется ограниченными функциональными возможностями.

Известно также устройство, содержащее запоминакщий блок, блок сравнения кодов, генератор серии импульсов, второй вентиль и триггер реверса, причем первая группа сравнения кодов соединена с выходами второго счетчика, вторая с выходами запоминающего блока, вход генератора серии импульсов подключен к входной клемме устройства, первьш вход IBTO рого вентиля подключен к выходу генератора серии импульсов, второй его вход подключен к выходу блока сравнения кодов, а выход - к счетному входу второго счетчика, С - вход

триггера реверса подключен к выходу элЕзмаята задержки, J-К-входы - к аыходу OjiOKa сравнения кодов, а выход триггера реверса соединен с икоцг - А упранле.чия второго счетчика -i запоминающего блока, вход элемента з;1даржкя соединен с выходом счетчика н одним из входов входного тригreps.j второй вход которого соединен с входной устройства Г 2,

Однако это устройство характеризуется ограниченн1 1мн функциональiibiMH аозмолчностяни, заключающимися в недостаГочном времели задер/кки.

Наиболее близким к предлагаемому является устройство, содержащее дифференцируюитую цепь, блок задержки фронта.; генератор импульсов, два веи THJiHj ,ий триггер, реверсив1й,й счегчик, суммирующий вход которого соединен с выходом генератора имггульсов че1)ез вентшгь, управляю- юш,ий вход которого подключен к источнику задерживаемых и myльcoв, вычитающий вход счетчика подключен к генератора импульсов через второй }зеач-иль, управляющий вход которого соед5-5;1ен с пулевььм выходом формирующего триггера, выходы ре- верси.вного счетчика через дешифратор нуля соед.инены с единичным входом триггера, к Hyj-iesoNry входу которого через дифференцирующую цель и блок задержки фронта подключен источник зацерхсиваемых импульсов, дополнительные вентиль, триггер и инвертор, вход дополн ггельного вентиля гюдгспючей к источнику задерживАемнлх импульсов j а выход - к управляющему входу первого венти я и к в-ходу дифференцирующей цени, к выходу которой подключен вход инвертора, выход инвертора соединен с нулевым входом доnojLHHTejibHoro триггера, единич{-)ый вход которого соединен с выходом дешифратора нуля, а выход - с управлягсщим входом дополнительного триг управляемый делитель частоты, подкл очен1й,1й сигнальным входом к выходу генератора счетных импульсов входом управления- к выходу переполнения и входу старшего разряда реBepcHBiioro счетчика, входом сброса к выходу дещифратора нуля и выходом - к сигнальным входам первого и второго вентилей ГЗ.

Однако это устройство характеризуется недостаточными фупкдиональными возможностями, заключающимися в

огра1 1ченном классе передаваемых функциональных зависимостей и недоcтaтoч {yю выдержку времвЕги,

Цель изобретения - увеличение задержки времени и расширение класса передаваемых функциональных зависимостей ,

Цель достигается тем, что в устройство постоянного запаздывания, содержащее генератор тактовых импульсов, соединенный со счетным входом счетчика импульсов, первый и второй запоминающие блоки, введены два бло- ка перемножения, два накапливающих сумматора,блок определения вспомогательных величин и комбинационный сумматор, при этом первый вход первого блока перемножения соединен с выходом счетчика импульсов, а второй вход - с входом устройства и первым входом первого накагшивающего сум iaтopa5 выход первого блока перемножения соединен с входом второго накапливающего сумматора, выходы первого и второго накапливающих сумматоров соединены с входами блока определения вспомогательных величин, Выходы блока определения вспомогательнь х величин соединены соответственно с входами первого и второго запоминающих бд-оков, выход первого запоминающего блока соединен с первым входом второго блока перемножения, второй вход второго блока перемножения соединен с выходом счетчика импульсов 5 выход второго блока перемножения соединен с первым входом комбинационного сумматора, второй вход которого соединен с выходом второго запоминающего блока, выход комбинационного сумматора соединен с выходом устройства.

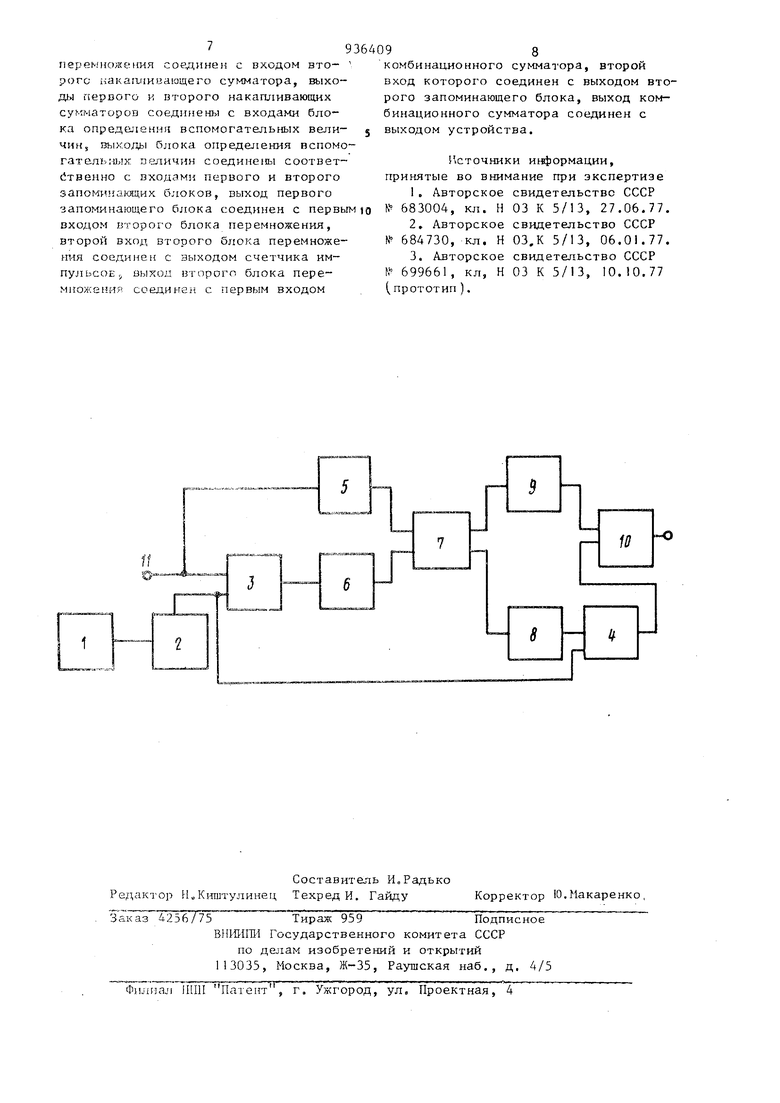

На чертеже представлена функциональная электрическая схема предлагаемого устройства постоянного запаздывания.

Устройство постоянного запаздывания содержит генератор I тактовых импульсов, счетчик 2 импульсов, первый 3 и второй 4 блоки перемножения, первый 5 и второй 6 накапливающие сумматоры, блок определения вспомогательных величин 7, первое 8 и второе 9 запоминающие устройства, комбинационный сумматор 10, и вход устройства 1 ,

Предлагаемое устройство работает следующим образом.

С выхода генератора тактовых импульсов 1 на вход счетчика импульсоь 2 поступает Р импульсов. Синхронно с тактовыми импульсам ла вход 11 устройства поступает Р значений входной функции. Таким образом, на первом накапливающем сумматоре 5 образуется величина, равная Р

Сх.,

is-i

где xi i-oe значение входной функции. На втором накапливающем сумматоре

образуется величина,С i-K.. , Полу1 1

ченные на первом и втором накапливающих сумматорах величины поступают на блок определения вспомогательных величин 7, а счетчик импульсов, первый и второй накапливающие сумматоры устанавливаются в исходное нулевое состояние. Процесс накопления для последующих значений функций повторяется. Одновременно с этим блок определения вспомогательнь х величин 7 определяет вспомогательные величины а и Ь в соответствии с ранее, полуРР

ченными значениями S К

м Р VXu-l

л

по следующим формульйым зависимостям

а Р,.. b Р

а у,

nix.Ct); р(р-1),.

Ь .

р(ри); Полученные вспомогательные величины а и Ь записываются в первые ячейки первого и второго запоминающего устройства соответственно. Следует отметить, что величины

ъ )

Р(р1и) Р(РН) PIP-U

для конкретных значений Р могут быть заранее определены и введены в блок определения вспомогательных величин при настройке устройства постоянного запаздывания, что упрощает получение вспомогательных величин а и Ь,

Запись в первое и второе запоминающее устройства последукщих значений вспомогательных величин происходит следующим образом,

На третьем этапе вычислений, определенные ранее величины а и Ь из первых ячеек первого и второго запоминающего устройства переписываются во вторые ячейки, а в первую записываются полученные новые значения величин а и Ь, На четвертом этапе вычислений полученные ранее величины а и Ь из вторых ячеек переписываются в третьи, а из первых во вторые ячейки. В освободившиеся первые ячейки записыват вновь полученные значеНИН величин а и Ь. Так процесс повторяется до заполнения всех К ячеек первого и второго запоминающих устройств.

этапе вычислений, полученные на первом этапе вычисления, значения вспомогательных величин .а и Ь. поступают на первый вход второго блока перемножения и второй вход комбинационного сумматора соответственно.

В соответствии с приведенной снемой соединений на выходах устройства будет образовываться вепичина, равная Р

0(5:1 иъ,

U-1

I

ЧТО соответствует воспроизведению входных значений функции с задержкой t , определяемой в соответствии с выражением

f Y1-p-t,

где t - период следования входных значений функции,поступающей на вход устройства.

При этом точность воспроизведения функциональной зависимости -определяется точностью кусочно-линейной аппроксимации.

Формула изoбpeтe fflя

40

Устройство постоянного запаздывания, содержащее генератор тактовых импульсов, соединенный со счетным входом счетчика импульсов, первый и второй запоминающие блоки, отличающееся тем, что, с целью увеличения времени задержки и расширения класса передаваемых функцио- нальных зависимостей, в него введены два блока перемножения, два накапливающих сумматора, блок определения вспомогательных величин и комбинационный сумматор, при этом перклй вход первого блока перемножения соединен с выходом счетчика импульсов, а второй вход - с входом устройства и первым входом первого накапливающего сумматора, выход первого блока

перемлож€ишя сое;7,инеи с входом второге 1;акашшва1ощего сумматора, выходы rsepDoro и второго накапливаюпшх сумматоров соединены с входами блока определения вспомогательных величин, выходы блока определения вспомогаталь:ш г аеличин соединены соответйтвенно с входами первого и второго запомигающих блоков, выход первого запоминаюи;его блока соединен с первы входом второго блока перемножения, второй вход второго блока перемножения соединен с выходом счетчика импульсов,, выход второго блока перемножан.ия соединен с первым входом

комбинаилонного сумматора, второй вход которого соединен с выходом второго запоминающего блока, выход комбинационного сумматора соединен с выходом устройства.

Рсточники информации, принятые во внимание при экспертизе

№ 683004, кл. Н 03 К 5/13, 27.06.77.

№ 684730, кл. Н03.К 5/13, 06.01.77.

Авторы

Даты

1982-06-15—Публикация

1980-06-06—Подача