(5) ДВУХКООРДИНАТНАЯ СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатный цифровой интерполятор | 1986 |

|

SU1315939A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Устройство для двухкоординатного управления рабочим органом | 1990 |

|

SU1815620A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Устройство для программного управления | 1981 |

|

SU976428A1 |

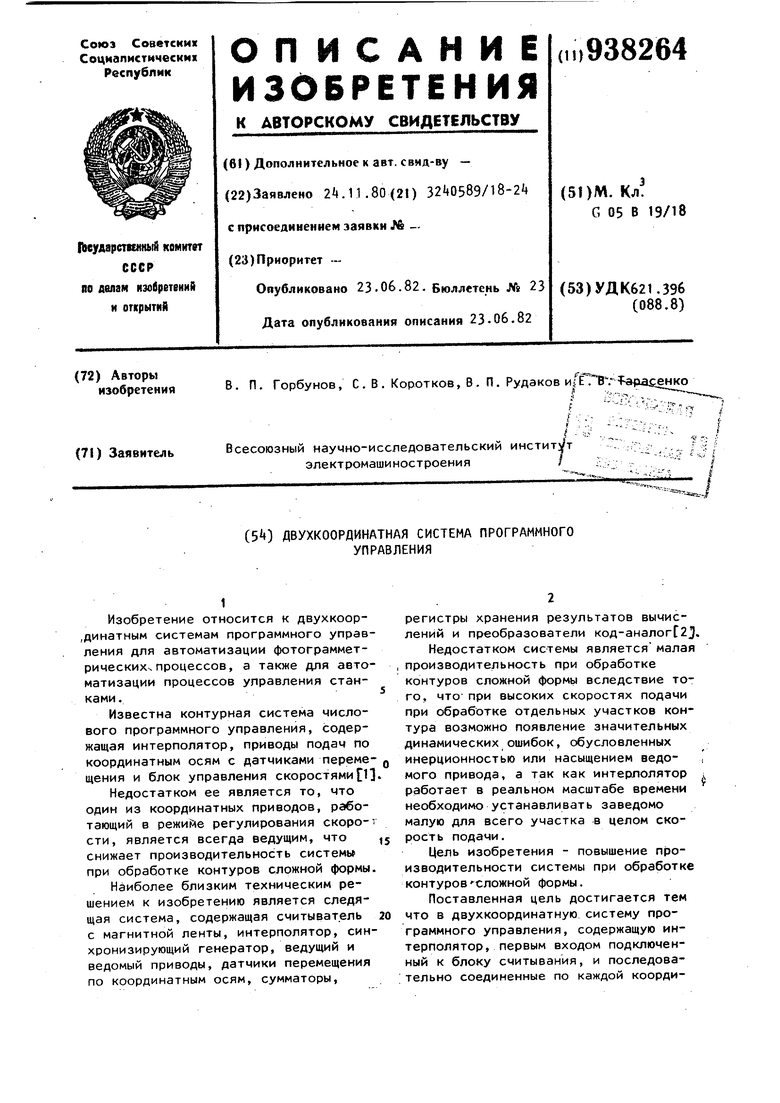

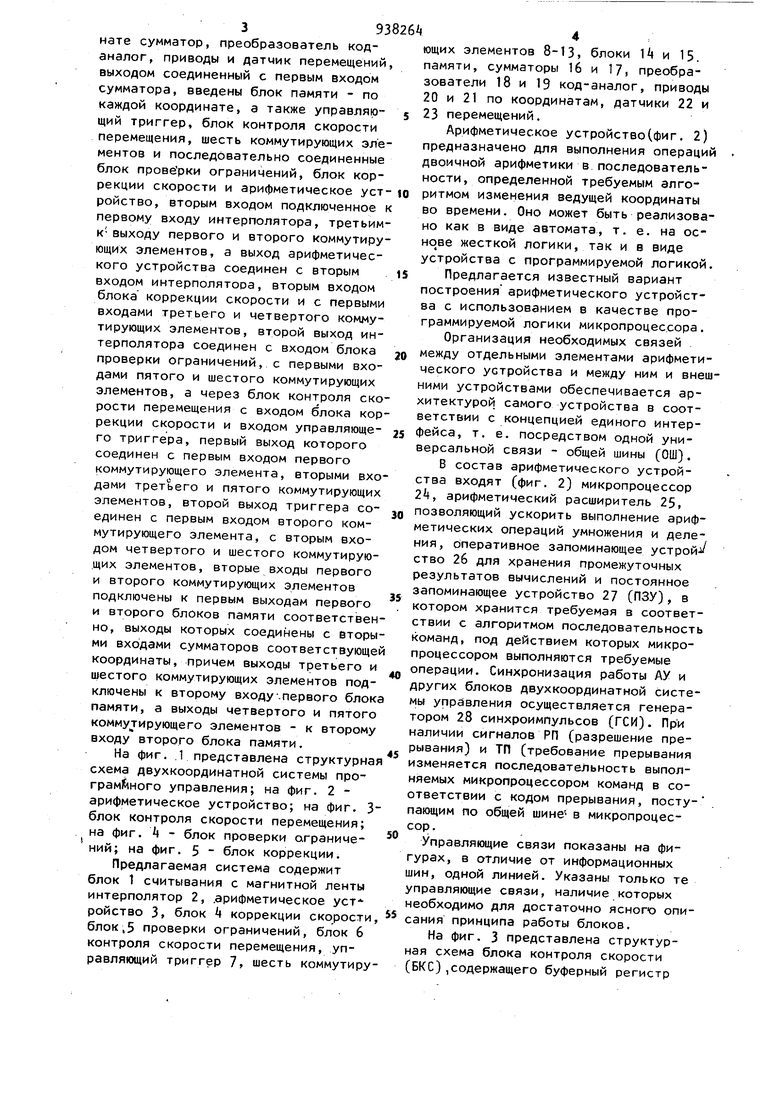

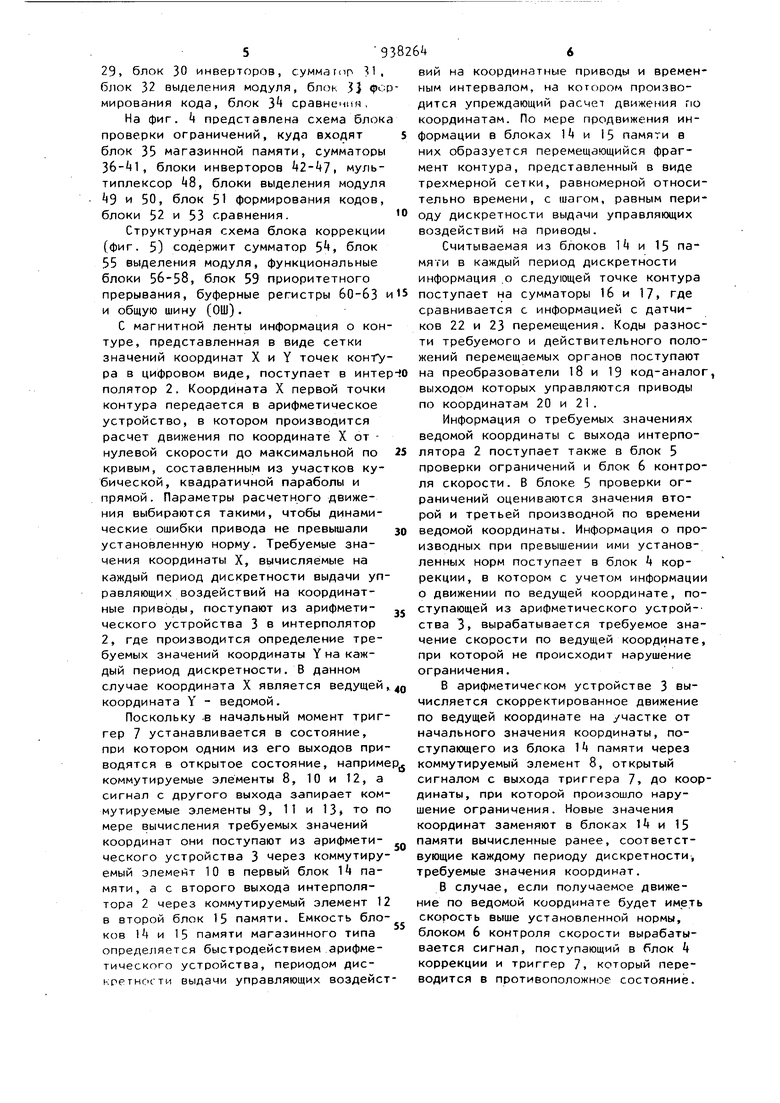

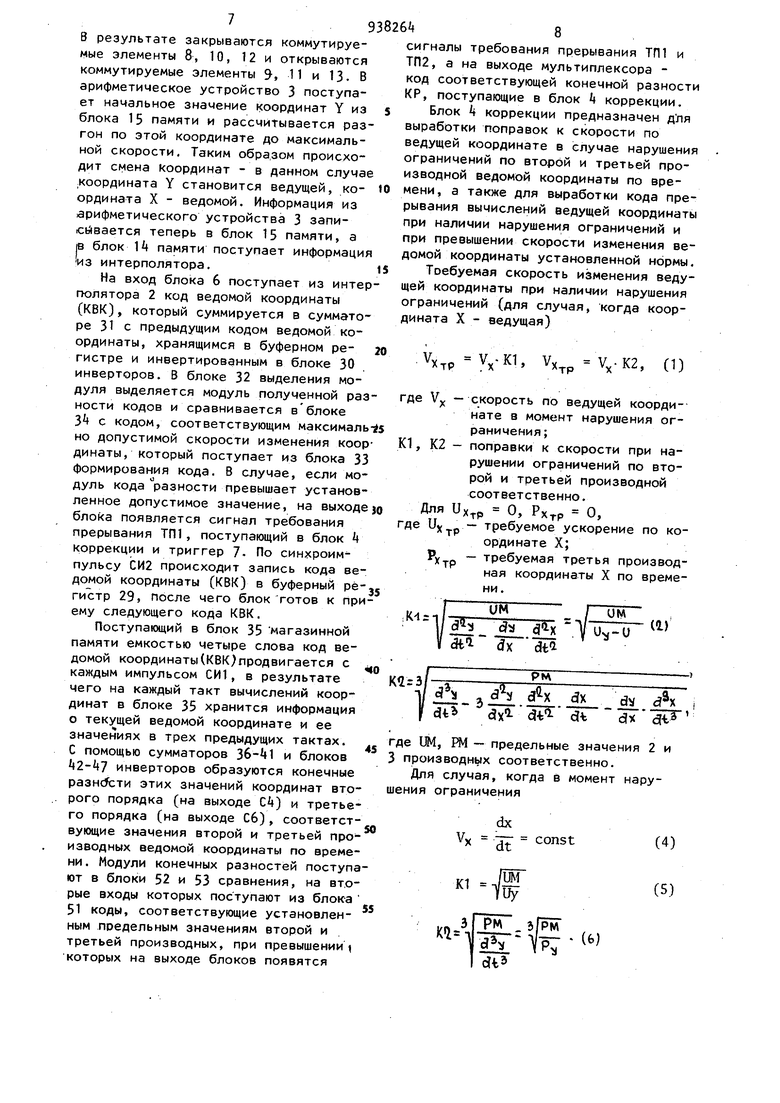

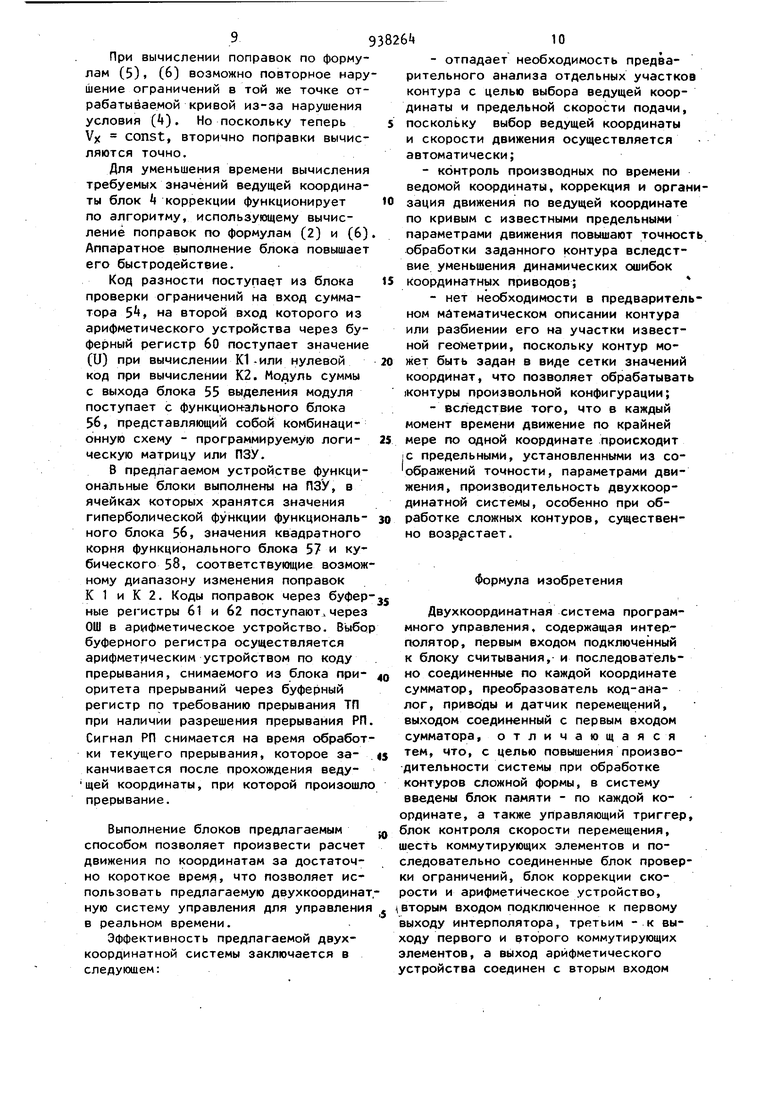

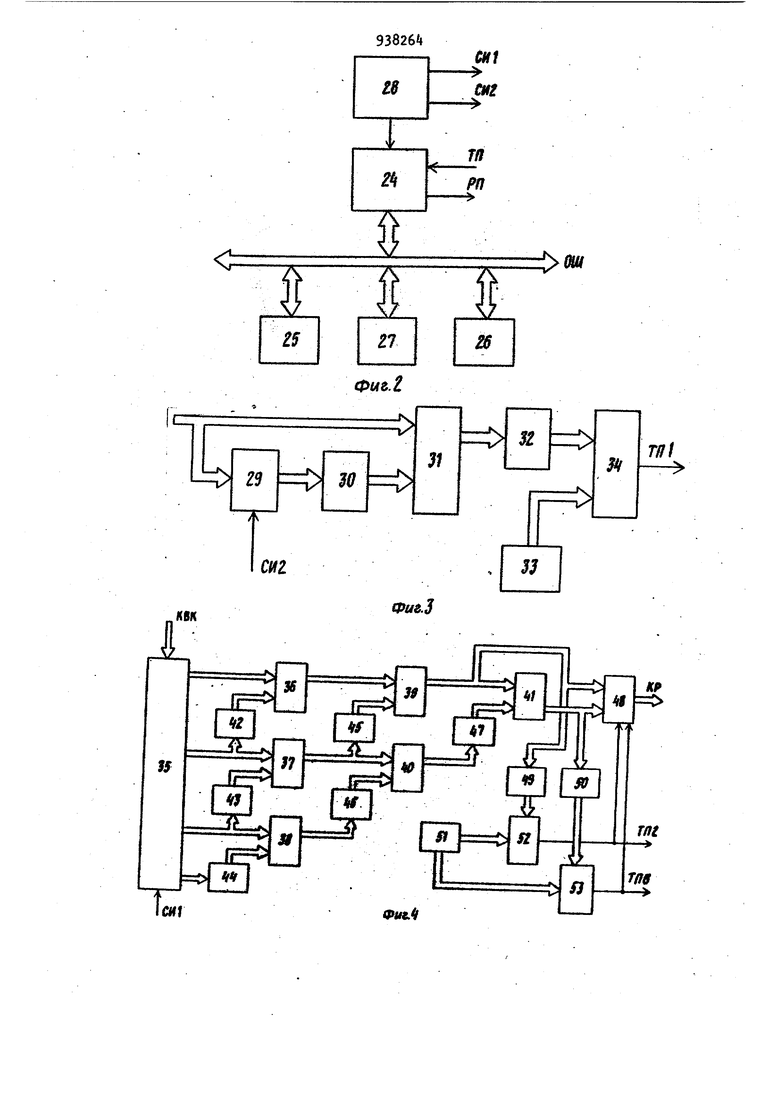

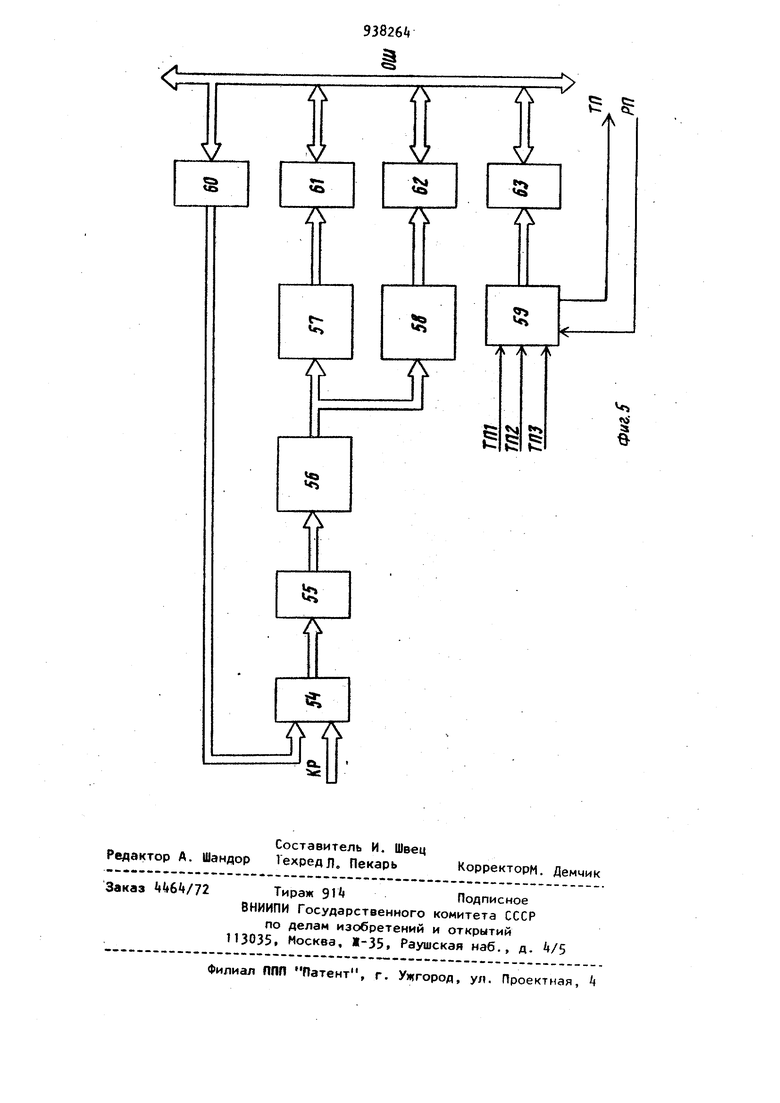

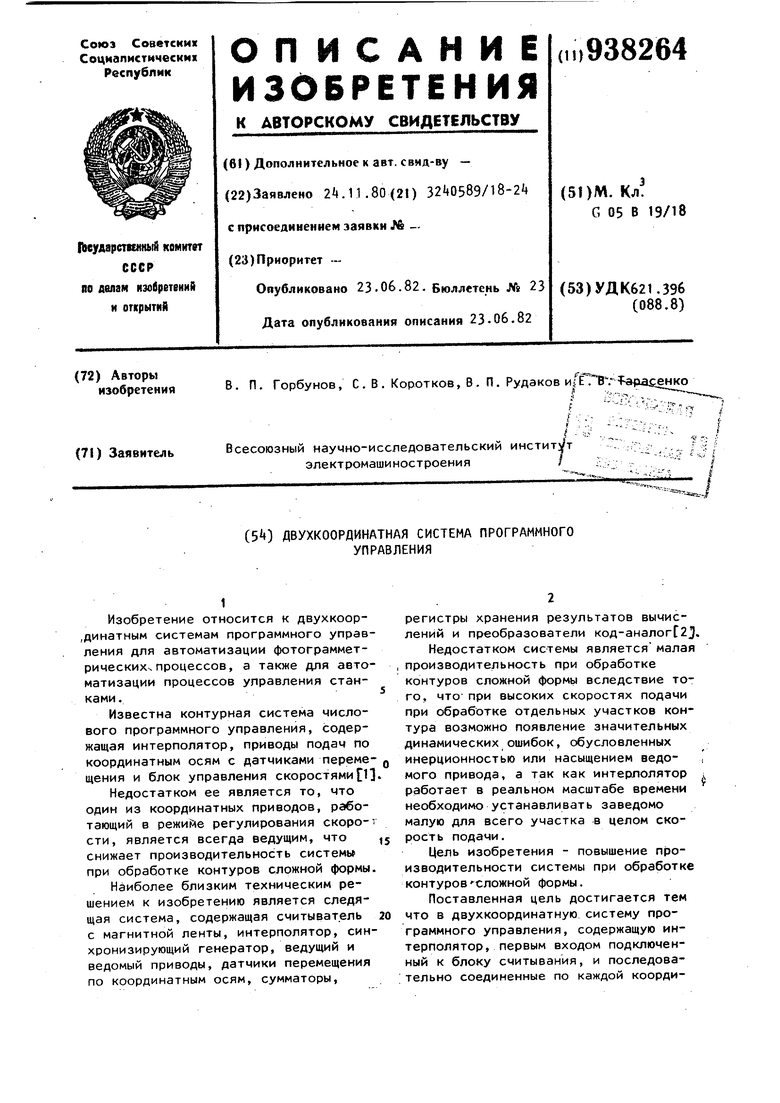

Изобретение относится к двухкоор,динатным системам программного управ ления для автоматизации фотограмметрических процессов, а также для авто матизации процессов управления станками . Известна контурная система числового программного управления, содержащая интерполятор, приводы подач по координатным осям с датчиками переме щения и блок управления скоростями I Недостатком ее является то, что один из координатных приводов, работающий в режийе регулирования скорости, является всегда ведущим, что снижает производительность системь при обработке контуров сложной формы Наиболее близким техническим решением к изобретению является следящая система, содержащая считыватель с магнитной ленты, интерполятор, синхронизирующий генератор, ведущий и ведомый приводы, датчики перемещения по координатным осям, сумматоры, регистры хранения результатов вычислений и преобразователи код-аналог 2. Недостатком системы является малая производительность при обработке контуров сложной формы вследствие того, что при высоких скоростях подачи при обработке отдельных участков контура возможно появление значительных динамических ошибок, обусловленных инерционностью или насыщением ведомого привода, а так как интерполятор работает в реальном масштабе времени необходимо устанавливать заведомо малую для всего участка в целом скорость подачи. Цель изобретения - повышение производительности системы при обработке контуровСЛОЖНОЙ формы. Поставленная цель достигается тем что в двухкоординатную систему программного управления, содержащую интерполятор, первым входом подключенный к блоку считывания, и последовательно соединенные по каждой коорди3938нате сумматор, преобразователь коданалог, приводы и датчик перемещений, выходом соединенный с первым входом сумматора, введены блок памяти - по каждой координате, а также управляющий триггер, блок контроля скорости перемещения, шесть коммутирующих элементов и последовательно соединенные блок проверки ограничений, блок коррекции скорости и арифметическое устроиство, вторым входом подключенное к первому входу интерполятора, третьимк выходу первого и второго коммутирующих элементов, а выход арифметического устройства соединен с вторым входом интерполятора, вторым входом блока коррекции скорости и с первыми входами третьего и четвертого коммутирующих элементов, второй выход интерполятора соединен с входом блока проверки ограничений, с первыми входами пятого и шестого коммутирующих элементов, а через блок контроля скорости перемещения с входом блока коррекции скорости и входом управляющего триггера, первый выход которого соединен с первым входом первого коммутирующего элемента, вторыми входами третьего и пятого коммутирующих элементов, второй выход триггера соединен с первым входом второго коммутирующего элемента, с вторым входом четвертого и шестого коммутирую.щих элементов, вторые входы первого и второго коммутирующих элементов подключены к первым выходам первого и второго блоков памяти соответствен но, выходы которых соединены с вторы ми входами сумматоров соответствующе координаты, причем выходы третьего и шестого коммутирующих элементов подключены к второму входу-.пер во го блок памяти, а выходы четвертого и пятого коммутирующего элементов - к второму входу второго блока памяти. На фиг, 1 представлена структурна схема двухкоординатной системы програм ного управления; на фиг, 2 арифметическое устройство; на фиг. 3 блок контроля скорости перемещения; на фиг. k блок проверки ограничеНИИ; на фиг, 5 блок коррекции. Предлагаемая система содержит блок 1 считывания с магнитной ленты интерполятор 2, .арифметическое устройство 3, блок t коррекции скорости блок,5 проверки ограничений, блок 6 контроля скорости перемещения, управляющий триггер 7, шесть коммутиру щих элементов 8-13 блоки 1А и 15. памяти, сумматоры 16 и 17) преобразователи 18 и 19 код-аналог, приводы 20 и 21 по координатам, датчики 22 и 23 перемещений. Арифметическое устройство(фиг, 2) предназначено для выполнения операций двоичной арифметики в последовательности , определенной требуемым алгоритмом изменения ведущей координаты во времени. Оно может быть реализовано как в виде автомата, т, е, на основе жесткой логики, так и в виде устройства с программируемой логикой. Предлагается известный вариант построения арифметического устройства с использованием в качестве программируемой логики микропроцессора. Организация необходимых связей между отдельными элементами арифметического устройства и между ним и внешними устройствами обеспечивается архитектурой самого устройства в соответствии с концепцией единого интерфейса, т, е. посредством одной универсальной связи - общей шины (ОШ). В состав арифметического устройства входят (фиг, 2) микропроцессор 24, арифметический расширитель 25, позволяющий ускорить выполнение арифметических операций умножения и деления. Оперативное запоминающее устрой- ство 26 для хранения промежуточных результатов вычислений и постоянное запоминающее устройство 27 (ПЗУ), в котором хранится требуемая в соответствии с алгоритмом последовательность команд, под действием которых микропроцессором выполняются требуемые операции. Синхронизация работы АУ и других блоков двухкоординатной системы управления осуществляется генератором 28 синхроимпульсов (геи). При наличии сигналов РП (разрешение прерывания) и ТП (требование прерывания изменяется последовательность выполняемых микропроцессором команд в соответствии с кодом прерывания, поступающим по общей шине- в микропроцессор. Управляющие связи показаны на фигурах, в отличие от информационных шин, одной линией. Указаны только те управляющие связи, наличие которых необходимо для достаточно ясного описания принципа работы блоков. На фиг, 3 представлена структурная схема блока контроля скорости (БКС),содержащего буферный регистр 29, блок 30 инверторов, сумматор 1, блок 32 выделения модуля, блок .} (рс мирования кода, блок 3 сравнения. На фиг. 4 представлена схема блок проверки ограничений, куда входят блок 35 магазинной памяти, сумматоры , блоки инверторов k2-k7, мультиплексор k8, блоки выделения модуля kS и 50, блок 51 формирования кодов, блоки 52 и 53 сравнения. Структурная схема блока коррекции (фиг. 5) содержит сумматор 5, блок 55 выделения модуля, функциональные блоки 56-58, блок 59 приоритетного прерывания, буферные регистры 60-63 и общую шину (ОШ). С магнитной ленты информация о кон туре, представленная в виде сетки значений координат X и Y точек конГу ра в цифровом виде, поступает в инте полятор 2. Координата X первой точки контура передается в арифметическое устройство, в котором производится расчет движения по координате X от нулевой скорости до максимальной по кривым, составленным из участков кубической, квадратичной параболы и прямой. Параметры расчетного движения выбираются такими, чтобы динамические ошибки привода не превышали установленную норму. Требуемые значения координаты X, вычисляемые на каждый период дискретности выдачи управляющих воздействий на координатные приводы, поступают из арифметического устройства 3 в интерполятор 2, где производится определение требуемых значений координаты Y на каждый период дискретности. В данном случае координата X является ведущей координата Y - ведомой. Поскольку -в начальный момент триггер 7 устанавливается в состояние, ПРИ котором одним из его выходов приводятся в открытое состояние, нaпpимe коммутируемые элементы 8, 10 и 12, а сигнал с другого выхода запирает коммутируемые элементы 9, 11 и 13 то по мере вычисления требуемых значений координат они поступают из арифметического устройства 3 через коммутируемый элемейт 10 в первый блок 1 памяти, а с второго выхода интерполятора 2 через коммутируемый элемент 12 в второй блок 15 памяти. Емкость блоков 1i и 15 памяти магазинного типа определяется быстродействием арифметического устройства, периодом дискретнссти выдачи управляющих воздейст ВИЙ на координатные приводы и временным интервалом, на котором производится упреждающий расчет движения по координатам. По мере продвижения информации в блоках 1 и 15 памяти в них образуется перемещающийся фрагмент контура, представленный в виде трехмерной сетки, равномерной относительно времени, с шагом, равным периоду дискретности выдачи управляющих воздействий на приводы. Считываемая из блоков 1i и 15 памяти в каждый период дискретности информация .о следующей точке контура поступает на сумматоры 16 и 17, где сравнивается с информацией с датчиков 22 и 23 перемещения. Коды разности требуемого и действительного положений перемещаемых органов поступают на преобразователи 18 и 19 код-аналог, выходом которых управляются приводы по координатам 20 и 21. Информация о требуемых значениях ведомой координаты с выхода интерполятора 2 поступает также в блок 5 проверки ограничений и блок 6 контроля скорости. В блоке 5 проверки ограничений оцениваются значения второй и третьей производной по времени ведомой координаты. Информация о производных при превышении ими установленных норм поступает в блок Ц коррекции, в котором с учетом информации о движении по ведущей координате, поступающей из арифметического устрой-ства 3, вырабатывается требуемое значение скорости по ведущей координате, при которой не происходит нарушение ограничения. В арифметическом устройстве 3 вычисляется скорректированное движение по ведущей координате на участке от начального значения координаты, поступающего из блока 1 памяти через коммутируемый элемент 8, открытый сигналом с выхода триггера 7, до координаты, при которой произошло нарушение ограничения. Новые значения координат заменяют в блоках 1 и 15 памяти вычисленные ранее, соответствующие каждому периоду дискретности, требуемые значения координат. В случае, если получаемое движение по ведомой координате будет иметь скорость выше установленной нормы, блоком 6 контроля скорости вырабатывается сигнал, поступающий в блок k коррекции и триггер 7, который переводится в противоположное состояние. В результате закрываются коммутируемые элементы 8, 10, 12 и открываются коммутируемые элементы Э, 11 и 13. В арифметическое устройство 3 поступает начальное значение координат Y из блока 15 памяти и рассчитывается разгон по этой координате до максимальной скорости. Таким обра.зом происходит смена координат - в данном случае координата Y становится ведущей, координата X - ведомой. Информация из арифметического устройства 3 записывается теперь в блок 15 памяти, а В блок 1А памяти поступает информация ИЗ интерполятора. На вход блока 6 поступает из интер гтолятора 2 код ведомой координаты (КВК), который суммируется в сумматоре 31 с предыдущим кодом ведомой координаты, хранящимся в буферном регистре и инвертированным в блоке 30 инверторов. В блоке 32 выделения модуля выделяется модуль полученной раз ности кодов и сравнивается в блоке З с кодом, соответствующим максималь но допустимой скорости изменения коор динаты, который поступает из блока 33 формирования кода. В случае, если модуль кода разности превышает установленное допустимое значение, на выходе блока появляется сигнал требования прерывания ТП1, поступающий в блок коррекции и триггер 7- По синхроим пульсу СИ2 происходит запись кода ведомой координаты (КВК) в буферный peгистр 29, после чего блок готов к при ему следующего кода КВК. Поступающий в блок 35 магазинной памяти емкостью четыре слова код ведомой координаты(КВК продвигается с каждым импульсом СИ1, в результате чего на каждый такт вычислений координат в блоке 35 хранится информация о текущей ведомой координате и ее значениях в трех предыдущих тактах. С помощью сумматоров Зб- и блоков инверторов образуются конечные разнЛти этих значений координат вто. рого порядка (на выходе С) и третьего порядка (на выходе Сб) , соответствующие значения второй и третьей производных ведомой координаты по времени. Модули конечных разностей поступа ют в блоки 52 и 53 сравнения, на вторые входы которых поступают из блока 51 коды, соответствующие установленным предельным значениям второй и третьей производных, при превышенииt которых на выходе блоков появятся игналы требования прерывания ТП1 и П2, а на выходе мультиплексора код соответствующей конечной разности Р, поступающие в блок Ц коррекции. Блок t коррекции предназначен для выработки поправок к скорости по ведущей координате в случае нарушения ограничений по второй и третьей производной ведомой координаты по времени, а также для выработки кода прерывания вычислений ведущей координаты при наличии нарушения ограничений и при превышении скорости изменения ведомой координаты установленной нормы. Тоебуемая скорость изменения ведущей координаты при наличии нарушения ограничений (для случая, когда координата X - ведущая) х,р V,-K1, V,p V,.K2, (1) где V - скорость по ведущей координате в момент нарушения ограничения;К1, К2 - поправки к скорости при нарушении ограничений по второй и третьей производной соответственно. Для О, Рхтр О, где Uy р - требуемое ускорение по координате X; требуемая третья производная координаты X по времени. I им/ им ,-и V где IM, Ш - предельные значения 2 и 3 производных соответственно. Для случая, когда и момент нарушения ограничения const о (Ь) 9 вычислении поправок по формулам (5), (6) возможно повторное нару шение ограничений в той же точке отрабатываемой кривой из-за нарушения условия С). Но поскольку теперь УХ const, вторично поправки вычисляются точно. Для уменьшения времени вычисления требуемых значений ведущей координаты блок Ц коррекции функционирует по алгоритму, использующему вычисление поправок по формулам (2) и (6) Аппаратное выполнение блока повышает его быстродействие. Код разности поступает из блока проверки ограничений на вход сумматора нэ второй вход которого из арифметического устройства через буферный регистр 60 поступает значение (U) при вычислении К1-или нулевой код при вычислении К2. Модуль суммы с выхода блока 55 выделения модуля поступает с функционального блока 56, представляющий собой комбинационную схему - программируемую логическую матрицу или ПЗУ. В предлагаемом устройстве функциональные блоки выполнены на ПЗУ, в ячейках которых хранятся значения гиперболической функции функционального блока 5б, значения квадратного Корня функционального блока 57 и кубического 58, соответствующие возмож ному диапазону изменения поправок К 1 и К 2. Коды поправок через буфер ные регистры 61 и б2 поступают,через ОШ в арифметическое устройство. Выбо буферного регистра осуществляется арифметическим устройством по коду прерывания, снимаемого из блока приоритета прерываний через буферный регистр по требованию прерывания ТП при наличии разрешения прерывания РП Сигнал РП снимается на время обработ ки текущего прерывания, которое заканчивается после прохождения ведущей координаты, при которой произошл прерывание. Выполнение блоков предлагаемым способом позволяет произвести расчет движения по координатам за достаточно короткое время, что позволяет использовать предлагаемую двухкоординат ную систему управления для управления в реальном времени. Эффективность предлагаемой двухкоординатной системы заключается в следующем: 4 -отпадает необходимость предварительного анализа отдельных участков контура с целью выбора ведущей координаты и предельной скорости подачи, поскольку выбор ведущей координаты и скорости движения осуществляется автоматически; - контроль производных по времени ведомой координаты, коррекция и организация движения по ведущей координате по кривым с известными предельными параметрами движения повышают точность обработки заданного контура вследствие уменьшения динамических ошибок координатных приводов; -нет необходимости в предварительном математическом описании контура или разбиении его на участки известной геометрии, поскольку контур может быть задан в виде сетки значений координат, что позволяет обрабатывать Контуры произвольной конфигурации; -вследствие того, что в каждый момент времени движение по крайней мере по одной координате происходит с предельными, установленными из соображений точности, параметрами движения, п|юизводительность двухкоординатной системы, особенно при обработке сложных контуров, существенно возрастает. Формула изобретения Двухкоординатная система программного управления, содержащая интерполятор, первым входом подключенный к блоку считывания, и последовательно соединенные по каждой координате сумматор, преобразователь код-аналог, приводы и датчик перемещений, выходом соединенный с первым входом сумматора, отличающаяся тем, что, с целью повышения производительности системы при обработке контуров сложной формы, в систему введены блок памяти - по каждой ко- рдинате, а также управляющий триггер, лок контроля скорости перемещения, ectь коммутирующих элементов и поледовательно соединенные блок провери ограничений, блок коррекции скоости и арифметическое устройство, вторым входом подключенное к первому ыходу интерполятора, третьим - к выоду первого и второго коммутирующих лементов, а вЫход арифметического стройства соединен с вторым входом интерполятора, входом блока коррекции скорости и с первыми входа ми третьего и четвертого коммутирующих элементов, второй выход интерполятора соединен с входом блока проверки ограничений, с первыми входами пятого и luecToro коммутирующих элементов, а через блок контроля скорос ти перемещения с входом блока коррек ции скорости и входом управляющего триггера, первый выход которого соед нен с первым входом первого коммутирующего элемента, вторыми входами третьего и пятого коммутирующих элементов, второй выход триггера соединен с первым входом второго коммутирующего элеменга, с вторым входом четвертого и шестого коммутирующих элементов, вторые входы первого и 9 12 второго коммутирующих элементов подключены к первым выходам первого и второго блоков памяти соответственно, выходы которых соединены с вторыми входами сумматоров соответствующей координаты, причем выходы третьего и шестого коммутирующих элементов подключены к второму входу первого блока памяти, а выходы четвертого и пятого коммутирующих элементов к второму входу второго блока памяти Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР (f 563668, кл. G 05 В 19/24, 1977. 2. Патент США № 3731175, кл. G 05 В 19/2, опублик. 1973 (прототип).

:

Фиъ.1

Фае.З

Авторы

Даты

1982-06-23—Публикация

1980-11-24—Подача