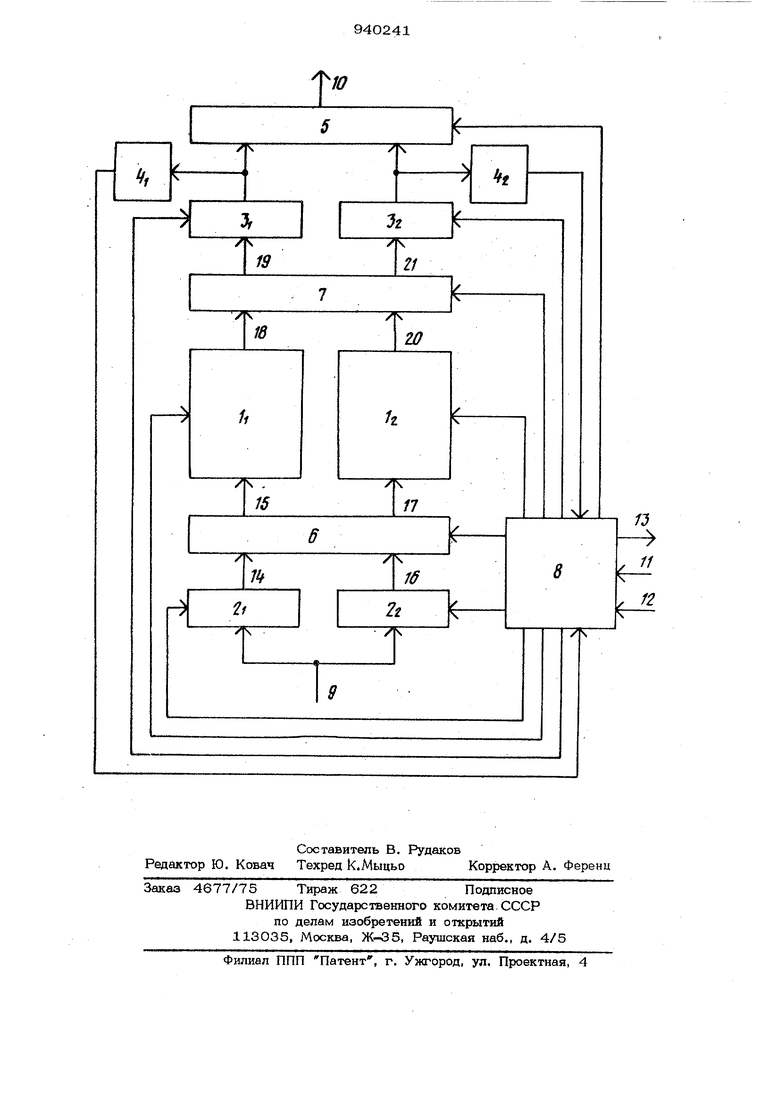

Изобретение относится к запоминающим устройствам. Известно запоминающее устройство с самоконтролем, содержащее накопитель, регистры адреса и числа, дополнительны накопитель, сумматор, элементы И и ИЛ и схему контроля по четности l . Недостатками этого устройства являются большие аппаратурные затраты и невысокое быстродействие. Наиболее близким к предлагаемому по технической сущности является запоминающее устройство с самоконтролем, содержащее блоки памяти, входы регистров адреса которых подключены к входны адресным шинам устройства, выходы регистров числа - ко входам соответствующих блоков контроля и ко входам коммутатора числа, выходы которого подключены к выходным шинам числа устройства, а вход управления - к соответствующему выходу блока управления, соединенного входами с выходами блоков контрол в этом устройстве в целях повышения быстродействия производится обнаружение ошибки путем поразрядного сравнения чисел, считанных с вуалируемых блоков памяти по адресу обращения (в устройстве блоки поразрядного сравнения объединены с коммутатором числа). При обнаружении ошибки с помощью блоков контроля локализуется неисправный блок памяти и информация на выходные шины устройства поступает с исправного блока 2 . Недостатком этого устройства {тля- ется невысокое быстродействие, ограниченное быстродействием одного из дублируемых блоков памяти. Цеяь изобретения - увеличение быст родействия устройства без ухудшения его надежностных характеристик. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее блоки памяти, регистры адреса, регистры числа, выходы которых подключены ко входам соответствующих блоков контроля и ко входам коммутатора числа, выходы которого являются выходами устройства, блок управления, одни из входов которого подключены к выходам блоков контроля, а выходы - к управляющим входам блоков памяти, регистров адреса, регистров числа, блоков контроля и коммутатора числа введены коммутатор адреса и дополнительный коммутатор числа, одни из входо JKOToporo подключены к выходам блоков памяти, а выходы - ко входам регистров числа, выходы коммутатора адреса соединены со входами блоков памяти, одни из входов - с выходами регистров адреса, другие входы коммутатора адреса и дополнительного коммутатора числа являются управляющими входами. На чертеже изображена структурная схема запоминающего устройства с самоконтролем. Устройство содержит блоки 1 и 1 j памяти, регистры 2. и 2, адреса, регистры 3j и 82 числа, блоки 4 и 4 контроля, коммутатор 5 числа, коммута- тор 6 адреса, дополнительный коммутатор 7 числа, блок 8 управления, входные адресные шины 9, выходные шины Ю числа, шину 11 обращения, шину 12 кода операции и шину 13 приема обращения В исходном состоянии на управляющие входы коммутатора 6 адреса и дополнительного коммутатора 7 числа с выходов блока 8 управления поступают управляющие сигналы, под действием которых вхо ды 14 коммутатора 6 адреса подключаются к его выходам 15, входы 16 -к выходам 17, входы 18 дополнительного коммутатора 7 числа подключаются к его выходам 19, входы 20 к выходам 2 При обращении к устройству на входы . блока 8 управления по шине 11 поступает сигнал обращения, по шине 12 сигнал кода операции, на входы регистров 2-f и 2д по шинам 9 - адрес обра;щения, на информационные входы блоков и Ij. памяти (не показаны) в случае опе рации записи - код записываемого числа Рассмотрим работу устройства при поступлении к нему последовательного потока обращений с операцией Считывание и безошибочной работе блоков 1 и 1х памяти. Под воздействием управляющих сигналов блока 8 первое обращение к устройству передается в блок памяти: адре обращения с шин 9 переписывается в регистр 2 к через коммутатор 6 поступает на адресные входы блока 1 памяти, в котором по данному адресу начинается процесс считывания информации. При этом с блока 8 по-шине 13 передается сигнал приема обращения, инициирующий формирование к устройству второго обращения. Второе обращение ввиду занятости первого блока 1 памяти передается в блок l. памяти : адрес обращения записьтается в регистр 2- и через коммутатор 6 поступает на адресные входы блока 1 памяти, в котором также начинается процесс считьшания информации. Далее с выходов блока 1. памяти считанный код числа черей коммутатор 7 поступает на входы регистра 3 и с его выходов на входы блока 4 контроля и входы коммутатора 5. При отсутствии ошибок в считанной информации блок 8 управления подключает входы коммутатора 5 к шинам Ю, после чего в блок 1 памяти передается на обработку третье обращение со считыванием. При этом считанный код числа с блока Ij памяти через коммутатор. 7 поступает на входы регистра 3 и с его выходов на входы блока входы коммутатора 5. При отсутствии ошибок в считанной информации блок 8 управления подключает входь коммутатора 5 к шинам 1О, после чего в блок 12 передается на обработку четвертое обращение со считыванием и т. д. Рассмотрим работу устройства при обнаружении ошибок в считанной информации. Пусть, например, из блока 1 памяти по некоторому адресу считывается неверная информация. Блок 4 контроля обнаружит ошибку и соответствующий сигнал поступит с его выхода на блок 8 упран - ления. Блок 8 запрещает выдачу неверной информации на шины. 1О и ожидает освобождения блока i. памяти в случае его занятости, после чего на управляющие входы коммутаторов 6 и 7 подаются управляющие сигналы, под действием которых происходит переключение выходов 17 коммутатора 6 с его входов 16 на входы 14 и переключение выходов 19 коммутатора 7 с его входов 18 на входы 20. При этом адрес, по которому считана неверная информация в блоке 1 с регис тра 2 поступает на адресные входы блока Ij. Далее производится считывание информации по этому адресу уже в блоке 1 2. памяти. Однако считанный код числа поступает не на входы регистра 32, а через коммутатор 7 на входы регистра ЗJ первого блока 1 памяти -и с его выходов(при отсутствии ошибок) через коммутатор 5 передается на шины 10. Необходимость коммутатора 7 обусловлена тем, что в регистре 32 может храниться код числа, считанный из блока 1 памяти по адресу обрашения, последовавшего за неверно обработанным в блоке l-i памяти Данный код числа в соответствии с условием сохранения порядка выдачи чисел порядку поступления обращений выдается из устройства только лишь после выдачи из регистра числа кода числа, считанного по адресу предыдзгшего обращения После обнаружения ошибки в блоке 1 памяти устройство работает аналогично. Технико-экономическое преимущество предлагаемого устройства по сравнению с известным состоит в том, что пропускная способность предлагаемого устройства практически в два раза выше. Формула изобретения Запоминающее устройство с самоконтролем, содержащее блоки памяти, регист ры адреса, регистры числа, выходы которых подключены ко входам соответствующих блоков контроля-и ко входам коммутатора числа выходы которого являют ся выходами устройства , блок управления, одни их входов которого подключены к выходам блоков контроля, а выходы.- к управляющим входам блоков памяти, регистров адреса, регистров числа, блоксю контроля и коммутатора числа, о т л и чающееся тем, что, с целью увеличения быстродействия устройства, оно содержит коммутатор адреса и дополнительный коммутатор числа, одни из входов которого подключены к выходам блоков памяти, а выхода - ко входам регистров числа, выходы коммутатора адреса соединены со входами блоков памяти, одни КЗ входов - с выходами регистров адреса, другие входы коммутатора адреса и дополнительного коммутатора числа являются управляющими входами. Источники информации, принятые во внимание при экспертизе 1.Самофалов К. Г. и др. Структурнологические методы повышения надежности запоминающих устройств. М., Машиностроение, 1976, с. 69. 2.Авторское свидетельство СССР № 696545, кл. Q11 С 29/00, 1977 (прототип).

t

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU920848A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU955210A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Устройство для контроля блоков памяти | 1979 |

|

SU790019A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU934554A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU879655A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1244726A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

Авторы

Даты

1982-06-30—Публикация

1980-12-29—Подача