Изобретение относится к импульсной технике. Известен депитепь частоты с дробным коэффшшевтом деления, .содержащий дет тель частоты с переменным коэффициентом деления, сумматоры, элемент cpaBHes ния кодов, блок квантованной задержки 1 . Недостатками делителя являются его сложность и недостаточное бъютродействне. Наиболее близким по технической сущности к предлагаемому является делитель частоты, содержащий блок деления частоты с переменным коэффициентом делеНИН, параллельный регистр, вход разреше ния записи которого соединен с шиной разрешения записи, и последовательный регистр, тактовый и информационный входы которого соединены соответственно с тактовой и информационной , а выходы соединены с информационными Ехо дами параллельного регистра, выходы которого соединены с входами блока частоты с переменным коэффициентом деления С2 Д . Данный делитель не обеспечивает аостаточного диапазона изменений коэффициента деления. Цель изобретения - расширеиие imane зона изменений коэффициента деления. Поставленная цель достигается :тем, что в делитель частоты импульсов с переменным коэффициентом деления, содержаший делитель частоты с управляемым коэффициентом деления, информационный вход которого соединен с входной шиной, а входы управления подключены к выходам параллельного регистра, первый вход которого соединен сшиной сигнала разрешения записи, а остальные входи подключены к выходам последовательного регистре, иервый вход которого соединен с шиной тактового сугвала, введены элемент И и: элемент ИЛИ, первый вход которого сое4 динен с шиной информационного сигнала, второй вход подключен к выходу элемента И, а выход соединен с вторым входам

последовательного регистра, последний выход которого соединен с первым входом элемента И, второй вход которого соединен с шиной управляющего сигнала, а первый выход последовательного регистра соединен с дополнительным вошдом управления делителя частоты с управляемым коэффициентом деления.

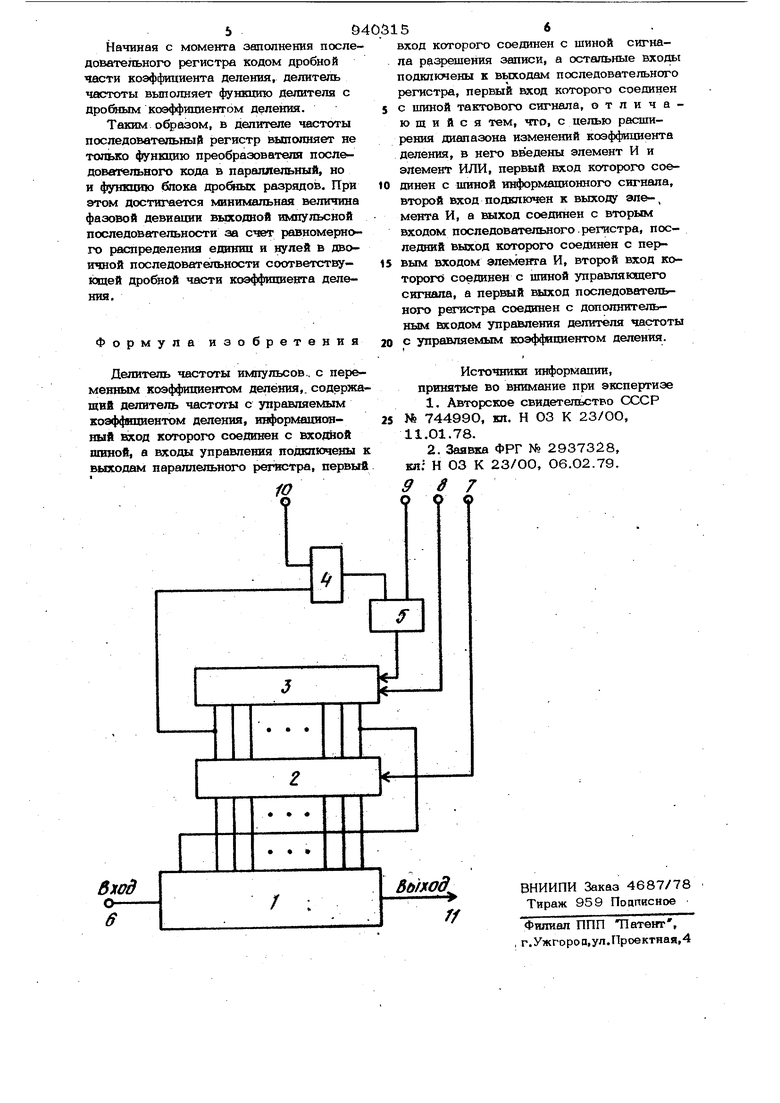

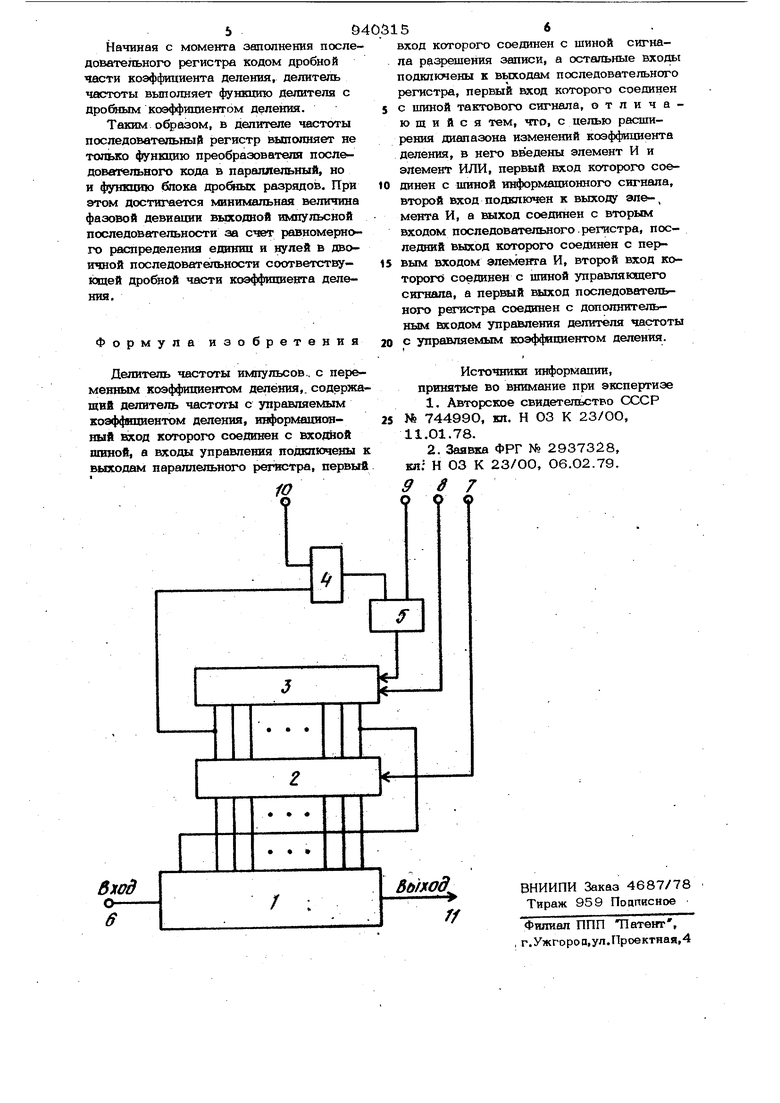

На Чертеже приведена структурная электрическая схема предлагаемого делителя.

Делитель частоты содержит делитель 1 частоты с управляемым коэффициентом деления, параллельный регистр 2, последовательный регистр 3, элемент И 4 и

элемент ИЛИ 5. На входную шину 6 подается входной сигнал, на шину 7 - сиг нал разрешения ааписр, на шину 8 - тактовый сигнал, на шину 9 - информационный сигнал, а на шину 10 - сигнал управления.

Выходной сигнал снимается с выхог- , да 11.

Делитель работает следуюишм образрм.

В режиме деления частоты по шине 8 на вход регистра 3 поступают импульс опорной частоты, которая численно равна выходной частоте делителя.

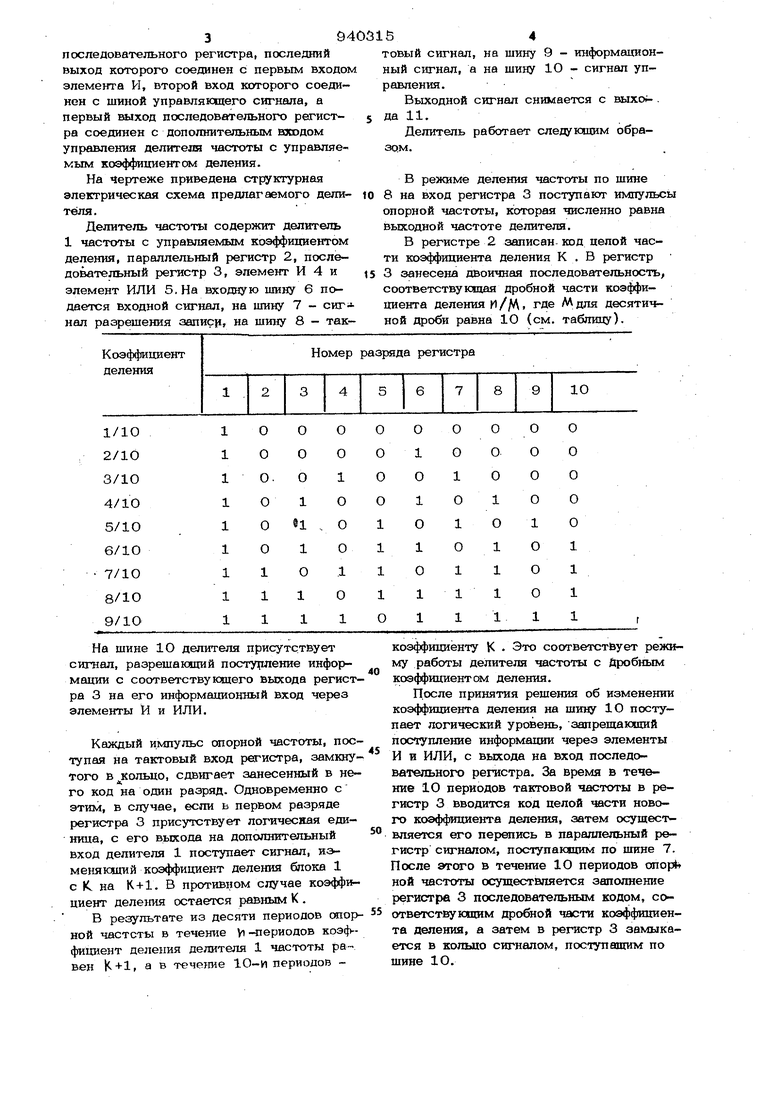

В регистре 2 записан код целой части коэффициента деления К . В регистр 3 занесена двоичная последовательность, соответствующая дробной части коэффициента деления И//А. где Мдля десятичной дроби равна 10 (см. таблицу).

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU984055A2 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1987 |

|

SU1589386A1 |

| Каскад цифрового накопителя | 1983 |

|

SU1140249A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| ЦИФРОВАЯ РЕГУЛИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2108659C1 |

| Цифровой умножитель частоты следования периодических импульсов | 1988 |

|

SU1596445A1 |

| Делитель частоты с дробнымпЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU849493A1 |

О

о о о 1

1

О О

о 1 о о о 1 о 1

1 1 1 1 1 1 1 1

о.

о

91 1 О 1 1

о

о

1

1

1 На шине Ю делителя присутствует сигнал, разрешающий посту шение информации с соответствующего выхода регист ра 3 на его информационный вход через элементы И и ИЛИ. Каждый цмпульс опорной частоты, поступая на тактовый вход регистра, замкнутогчэ в кольцо, сдвигает занесенный в него код на один разряд. Одновременно с этим, в случае, если ь первом разряде регистра 3 присутствует логическая единица, с его выхода на дополнительный вход делителя 1 поступает сигнал, измеияюш:ий коэффициент деления блока 1 с К. на К + 1. В прютивном случае коэффициент деления остается равным К . В результате из десяти периодов опорной частоты в течение Vi -периодов коэффициент деления делителя 1 частоты равен К+1, а в 1О-И периодов о о о о о 1 1 1 1

о о. о 1 о 1 1 1 1

о о о о 1 о о о 1

о о 1 о 1 о 1 1 1

о 1 о 1 о 1 о 1 1 коэффициенту К . Это соответстЬует режиму работы делителя частоты с йробным коэффициентом деления. Цосле принятия решения об изменении коэффициента деления на шину 1О поступает логический уровень, запрещающий поступление информации через элементы И и ИЛИ, с вьпсода на вход последо вательногх) регистра. За время в течение 10 периодов тактовой частоты в регистр 3 вводится код целой части нового коэффициента деления, затем осуществляется его перепись в параллельный регистр сигналом, поступающим по шине 7. После этсмго в течение 10 периодов onopi ной частоты осуществляется заполнение регистра 3 последовательным кодом, соответствующим дробной части коэффициента деления, а затем в регистр 3 замыкается в кольцо сигналом, поступащим по шине 10.

Авторы

Даты

1982-06-30—Публикация

1980-12-23—Подача