(5) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов с переменным коэффициентом деления | 1980 |

|

SU940315A1 |

| Программируемый делитель частоты следования импульсов | 1981 |

|

SU993481A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Делитель частоты следования импульсов | 1989 |

|

SU1709514A1 |

| Каскад цифрового накопителя | 1983 |

|

SU1140249A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1979 |

|

SU826343A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1277387A2 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Преобразователь частоты следования импульсов | 1988 |

|

SU1647845A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

Изобретение относится к радиосвязи и предназначено для использования в цифровых синтезаторах частоты. По основному авт. св. № известен делитель частоты следования импульсов, содержащий делитель частоты с управляемым коэффициентом деления , информационный вход которого соединен с входной шиной, а входы управ ления подключены к выходам параллельного регистра, первый вход которого соединен с шиной сигнала разрешения записи, а остальные входы подключены к выходам последовательного регистра, первый вход которого соединен с шиной тактового сигнала, элемент И, элемент ИЛИ, первый вход которого соединен с шиной информационного сигнала, второй вход подключен к выходу элемента И, а выход соединен Со вторым входом последовательного регистра, последний выход которого соединен с первым входом элемента И, второй вход которого сое- динен с шиной управляющего сигнала,, а первый выход последовательного регистра соединен с дополнительным входом I управления делителя частоты с управляемым коэффициентом деления 1. Однако известное устройство имеет недостаточно высокую точность умно; гения. Цель изобретения - повышение точности деления путем снижения амплитуды и периода фазовой девиации выходной импульсной последовательности. Поставленная цель достигается тем, что в делитель частоты следования импульсов с переменным коэффициентом деления, содержащий делитель частоты с управляемым коэффициентом деления, информационный вход которого соединен с входной шиной, а входы управления подключены к выходам параллельного регистра, первый вход которого соединен с шиной сигнала разрешения записи, а остальные входы подключены к выходам последовательного регистра, первый вход которого соединен с шиной тактового

398А

сигнала, элемент И и элемент ИЛИ, первый вход которого соединен с шиной информационного сигнала, второй вход подключен к,выходу элемента И, а выход соединен со вторым входом последовательного регистра, последний выход которого соединен с первым входом элемента И, второй вход которого соединен с шиной управляющего сигнала, введены элемент И-НЕ и дополнительные элементы ИЛИ и И, первые входы которых соединены с выходом первого разряда последовательного регистра, вторые входы - с выходом (ujSM+l.)-го разряда последовательного регистра, а вы ходы - с входами элемента И-НЕ, при этом первый ивторой дополнительные входы управления делителя частоты с управляемым коэффициентом деления соединены с выходами соответственно дополнительного элемента И и элемента И-НЕ СП.

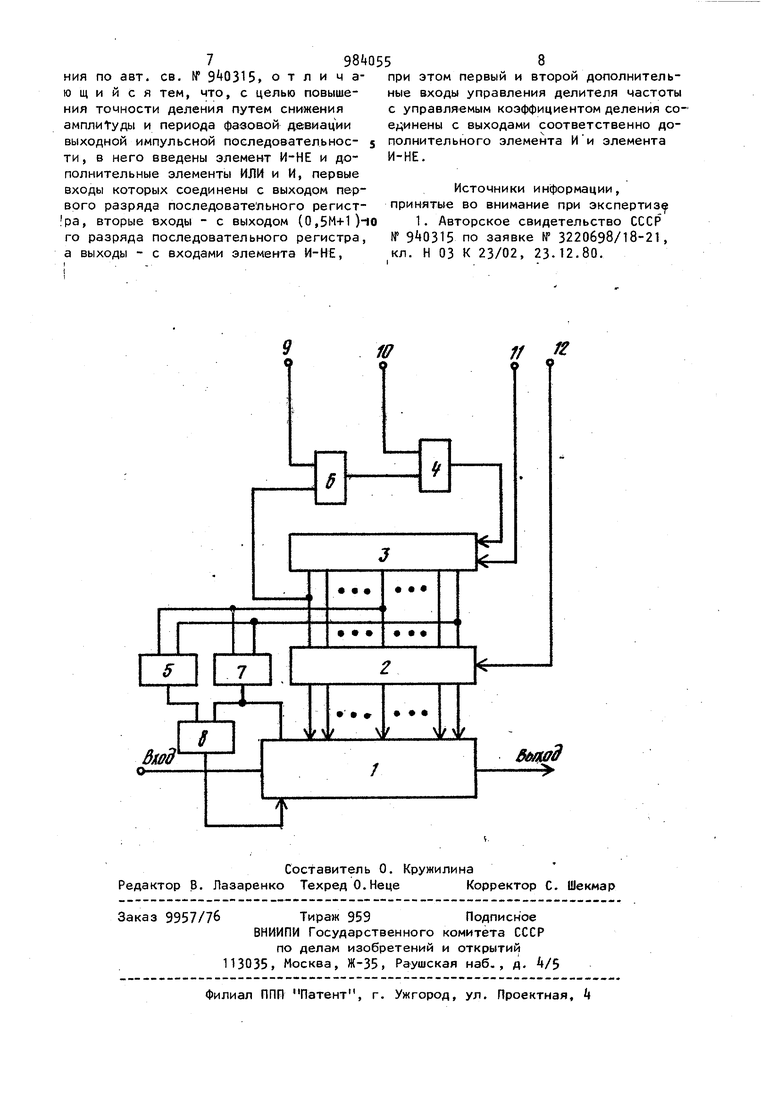

На чертеже представлена структурная схема предлагаемого устройства.

На шине 9 делителя присутствует сигнал, разрешающий поступление информации с соответствующего выхода регистра 3 на его информационный вход через элементы 6 и А.55

Каждый импульс опорной частоты,.поступая на тактовый вход -регистра 7 замкнутого в кольцо, сдвигает занесенОно содержит делитель 1 частоты с управляемым коэффициентом деления, параллельный регистр 2, последовательный регистр 3, элементы ИЛИ 4 и 5, элементы И 6 ц 7 элемент И-НЁ 8, шину 9 управляющего сигнала, шину 10 информационного сигнала, шину 11 тактового сигнала, шину 12 сигнала разрешения .записи.

i

Устройство работает следующим образом.

В режиме деления частоты по шине 11 на первый вход регистра .3 поступают импульсы опорной частоты, которая численно равна выходной частоте делителя частоты. В регистре 2 записан код целой части коэффициента деления К. В регистре 3 занесена двоичная последовательность, соответствующая дробной части коэффициента деления п/М, где М для десятичной дроби равна 10. Данные приведены в табл. 1.

Т а б л и ц а 1

ный в него код на один разряд. Если при этом в первом или в шестом разряде регистра 3 присутствует логическая единица, то элемент 5 будет находиться в единичном состоянии и сигнал с его выхода поступит через элемент 8 на вход переключения с коэффициента деления К на коэффициент К+0,5 дели5SBkQSS6

теля 1. Если же логическая единицаключит делитель 1 с коэффициента деприсутствует и .в первом и в шестомления К на коэффициент К+1 . разряде регистра 3, то в единичном В соответствии с логикой работы

состоянии будет находиться и элементэлементов на переключающие входы

присутствующий на входе элемента 7 изменяющие его коэффициент деления

запретит возникновение сигнала на вы-на величину 1 или 0,5. Данные привеходе элемента 8 в свою очередь, пере-дены в табл. 2. Из табл. 2 видно, что дробный коэффициент деления реализуется за время в течение любых пяти полных циклов деления входной частоты. После принятия решения о изменении коэффициента деления на шину 9 поступает логический уровень, запрещающий поступление информации через элементы 4 и 6 с выхода на вход регистра 3. За время в течение 10 периодов тактовой частоты в регистр 3 вводится код целой части нового коэффициента.деления, затем осуществляется его перепись в регистр 2 сигналом, поступающим по.шине 12. После чего в течение . 10 периодов опорной частоты осуществляется заполнение регистра 3 последовательным .соответствующим дробной части коэффициентом деления, а затем регистр запирается в кольцо Сигналом, поступающим по шине 9... Через пять циклов, начиная с момен та заполнения последовательного регис

Таблица2 тра кодом дробной части коэффициента деления,, делитель частоты следования импульсов выполняет функцию делителя с дробным коэффициентом деления. Таким образом, в предлагаемом делителе частоты следования импульсов с переменным коэффициентом деления последовательный регистр выполняет не только функцию преобразователя последовательного кода в параллельный, но и функцию блока дробных разрядов. При этом достигается минимальная величина амплитуды и периода фазовой девиации выходной импульсной последовательности за счет равномерного распределения управляющих воздействий на управляющие входы делителя 1 за число циклов деления входной частоты, в два раза меньшее величины знаменателя дробных разрядсзв. Формула изобретения Делитель частоты следования импульOJ с переменным коэффициентом деления по авт. ев, № 9 +0315, отличающийся тем, что, с целью повышения точности деления путем снижения амплитуды и периода фазовой девиации выходной импульсной последовательное- s ти, в него введены элемент И-НЕ и дополнительные элементы ИЛИ и И, первые входы которых соединены с выходом первого разряда последовательного регист ра, вторые входы - с выходом {0,5M+1)-io го разряда последовательного регистра, а выходы - с входами элемента И-НЕ,

о

// J 5 при этом первый и второй дополнительные входы управления делителя частоты с управляемым коэффициентом деления сое;;;инены с выходами соответственно дополнительного элемента И и элемента И-НЕ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № по заявке № 3220698/18-21, кл. Н 03 К 23/02, 23.12.80.

Авторы

Даты

1982-12-23—Публикация

1980-12-26—Подача