38 а код уменьшается на величину А и даль нейшее его изменение , происходит наёмная с разности: . Затем обычными способами осуществля ют сравнение фаз (фазовое детектировани импульсных последовательноса й: исходной .%) и потученной в результате де ления ) . Одновременно преобразуют код С( t) в аналогоеук форму и суммиру ют с результатом детектирования, чем достигается компенсация неточности детектирования, связанной с аппроксимацией дробного коэффициента N целочисленны ми: Ко и NO+ 1 Способ осуществляют устройством, содержащим делитель частоты с дроб- . ньш переменным коэффициентом деления (ДПКД), фазовый детектор, днфро-анало говьй преобразовагель (ЦАП) и сумматор Д1 JKilf состоящий иа блока упраштэния, делителя часто: ът н. накслшкпъного регистра. Ма оходы блока управлспшя поступают коды Л Q я АО г значения которых пропорц|1О гднь Ы значениям соответствующих частот Ej-j п |;с., , Блок управления вырабатывает КОД MO , : П раЕ;МЯЮЩ1тЙ OHTor-.-f nenirie, v: код d j постумающнй на 1уаформаиионпьда вход накопительного pei:-uc -pfl, К|:)омотого, блок упраплеппя осуществляе иаме ;онне кав()1та деления дожхепн перепопненин на- к:опи-1-епьг 01 о регистра, формирующех о кодовую 1Ю-с юдопате,пьлость EMKOCTI натсопитол,иг)Го регнстра выбирается, равиой Q - А с . На- выходе ДПКД образуется импульс, пая поспедовательность (DQ (-fc , частота которой в cpewieM равна частоте i . МгноБОИное ;ке значение частоты в общем .случае стличается от , так как Д{зоб™ ньй коэффициент К аппроксимирован цело чиспеннь№1И коэ4 фициентами HO , черещгющимйся во времени. Из :за этохр на выходе фазового детектора ирисуTCTi вует помеха дробности компенсация кото рых аналоговьми средствами малоэф хэк-, тивна, что является недостатком извесфного ус1ройства. Цель изобретеиня - уменьшение помех Д|зобности„ Указанная цель достигается тем, что в известном способе цифрового фазово1,о детектировании импульсных последователь ностей на неравных частотах, основанном на делении большей из сравниваемых час™ тот в дробное число разНай, где и Д, дельвэ числа, пропорЦЕюнальные соответствующим частотам fj, и-f соот 8 ветственно первой н второй импульснмх последовательност(;й, путем изменения целочисленного коэ(|ж})нциемта деления, для чего третью импульсную последователькость, полученную в реаультаа-е уменьщения частоты 0 в N раз, преобразуют в цифррвой код qdi) , возрастающий с каждым импульсом на величину с , равную числителю дроби V-J составляющей дробную часть коэфс)ициента N , пока dgd) не достигнет значения Д , равного или больщего At после чего коэффициент деления изменяют на единицу на время одного цикла деления, а код уменьшают на величину Ас и-дальнейшее его изменение происходит, начиная с разности АС, фортугаругот код c |j{i; суммированием (S{-t)и АО , получают сигнал фазового рассогласования Ф(Ь) в ииф ровом виде, поочередно запоминая мгновепные значения кодов dc(-t) i )в моменты появления импульсов второй и третьей импульсных, последовательностей ) и (7(i)таким образом, что очередное значение o(-t) существует с момента появпения очередного импу.пьса второй импульсной последовательности f(i.) до момента ).ЯБЛ.еня.я очередного импульса Т 5етьей импульсной поспедовательности ) ado(- на остальных инТ13рва лах времени преобразуют :lioд cb(i) в аналоговую форму усредилют результат П х:}обрааова шя, а в известное устройство для осуществления известного способа, содержащее цифро-аналоговый преобразователь, сумматор и делитель частоты с переменным пробным коэффициентом деления, состоящий иа блока управления, делителя частоты н накопительного ре гистра, к информационному входу которого пош лючен выход для дробной части коэфлфидиента Н блока управления, а выход переполнения накопительного регистра соединен с входом изменения коэффициента деления на единицу блока управления, к входам которого подключены шины кодов A(j и АС и вькоД ,аля целочисленной части коэффициента N блока управления подключен к первому входу делителя частоты, второй вход которого подключен к шине первой импульсной последовательности, введены блок ключей, запоминающий регистр, фильтр нижних частот, триггер, элемент ИЛИ и три элемента задержки, через первый из которых выход делителя частоты подключен к тактовому входу накопительного регистра, выход которого соединен с первым входом лока ключей и с первым входом сум58

матора, второй вход которого подключен к шине кода А о, а вькод сумматора соединен с вторым входом блока ключей, управляющие входы которого соединены с выходами триггера выход с первым входом запоминающего регистра, вькод которого через дифро-аналоговый преобразователь подключен к входу фильтра нижних-частот, а второй вход соединен с выходом элемента ИЛИ, первьп вход которого соединен непосредственно с вькодом делителя частоты и через второй элемент задержки - с первым входом триггера, второй вход которого через третий элемент задержки соединен с ши-. ной второй импульсной последовательное™ ти и вторьм входом элемента ИЛИ,

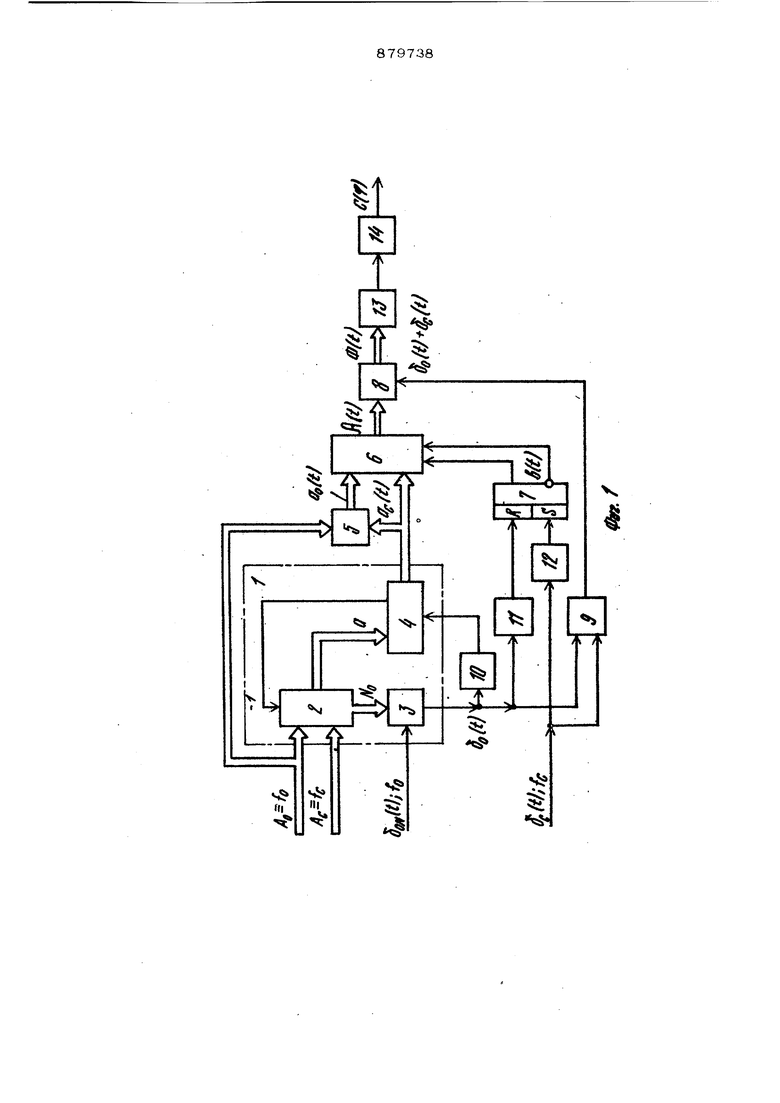

На фиг. 1 приведена схема устройства, в котором реализуется описываемьоЧ способ , на фиг, 2 временные диаграммы работы устройства.

Устройство содержит делитель 1 с дробным переменным коэффициентом деления, блок 2 управления, делитель 3 частоты, накопительньп регистр 4, cj viMaтор 5, блок 6 ключей, триггер 7, запоминающий регистр 8, элемент ИЛИ 9, первьв элемент 10 задержки, второй и третий элементы 11, 12 задерккк ЦК(1 ро-аналоговый преобразователь 13, фильт 14 нижних частот. Делитель 1 частоты с дробньш первменньЕЛ коэффициентом деления служит для получения третьей импульсной последовательности и переменного кода с( ({:), Суммирование кодов Cic.lt) и Дд осуществляется сумматором. Сформированный код совместно с кодом cj,t) поступает на блок б , управляющие входы которого подключены к выходам триггера 7, Триггер управляет ключами таким образом, что код ) передается на запоминающий регистр после прихода очередного импульса ) кода (-t) - после прихода очередного им пульса (i) , Так формируется код А (.-Ь) на информационном входе запоминающего регистра 8,;

Для получения кодаф() мгновенные значения кoдaД(t) записываются в запоминающем регистре 8 с помощью суммы последовательностей c(-t) и c(t) , выделяемой на выходе элементы ИЛИ 9 и подаваемой на тактовьш вход регистра.

Элементы задержек 10, 11, 12 введены для устранения неопределённостей при записи мгновенных значений кода A(t) в запоминающий регистр 8, Неопределенность возникает, когда момент записи в регистр попадает в интервал переходньк

86

процессов на его 11 фз;л{а;и101;;пк в:-:олз; Чтобы избенчать этого, нео6ход -:л-1о выпс;а нить следующею условия: сггл.арисэ премя задержки в эпe,feнтe ИЛИ и аапса; ипо щам perifCTpQ быть bieiifcins i:,, плюс задержки в 15акоп тельтшк1 periiCipas cyiviMaTope блока ключей и меньще плюс задержки в триггере м ключах,

С приходом на тактовый вход регист-ра 8 импульса последовательности записывается значение кода qc,(i) , которое сохраняется до прихода импульса ) после чего записывается значение кода cig(t) и т, д. Полученный таким образом

переменный кодф(й поступает i элемент 13, где преобразуется в аналоговую форму. Фильтр нижних частот выде ляет постоянную составляющую С.(1/ являющуюся результатом детектирования. Ее величина saBiicuT пкшъ от эквивалент. Ktxi разности фга нсхош ых тшз пьсных по-аледователыгос1ейсГ5(4) и

На временных диаграммах йллюстрнруюшнх работу устройства, выбрано: р --t(i3 условных едиинцехК Значея1 Я кс-дой: Д(7- iSi Ас 7 иаяменьшЕе цепыа 4 scvi3j пропорц11онапьные ссатветст-f:

суюшлм частота . г,л

6

ft 7 т. е, а 6, козфф щ;шнт N(7

1ерэд;-. ется с KO3dTJJ iiTif9HTON;

задержекгиг-/;tftiig, Пунктиром на ф.тг. 2 показан перехоШ1ый процесс в сумматоре 5,

, Из приведенных. аостроен 1Й видно, что площадь под функцией J(t) остается постоянной на каждом периоде последовательности (У (t) J т, е. помехи дробности отсутствуют.

Простота реализации способа обеспечивает высокую надежность устройств цифрового фазового детект фовання.

Формула изобретения

1, Способ цифрового фазового детектн- рования импульсных последовательностей на неравных частотах, основанный на делении большей (га сравниваемых частот

в дробное paaN-. , где Ал

Ас я /1 -. целые числа, прЬпЬршшнальпые

соответствующим частотам Q к сосгветствекно первой и второй импульсных последователь остей, путем 11змене1;кя целочисленного коэффициента делениядля чего третью импульсную последова-

тельность, полученную в результате уменьшения частоты fo в N , преобразуют в цифровой код OcU) возрастающий с каждым импульсом на величину С( , равную числителю дроби i- составляющей дробную часть коэффициенте М , пока d(v(t) не достигнет значения ) равного или большего Дс после чего коэффициент деления изменяют на единицу на время одного цикла делений, а код уменьшают на величину Дс и Дальнейшее его изменение приосходит, начиная с разности , о т л и ч а ющ и и с я тем, что, с целью уменьшения помех дробности, формируют кодd(7(t)суммированием c((.(-t) АО получают сигнал фазового рассогласования «{(t в цифровом виде, поочередно запоминая мгновенные 3Ha4eHViH кодов c(,(t) и cig (t) в моменты появления импульсов второй и третьей импульсных последовательностей ( и (У (t) таким образом, что очередное значение (-tj существует с момента появления очередного импульса второй импульсной последовательности C(t) до момента появления очередного импульса третьей импульсной последовательности 0(1 (t), а OQ (t) - на остальных интервалах времени преобразуют код ф (.-fc) в аналоговую форму и усредняют результат Преобразования.

2, Устройство для осуществления способа цифрового фазового детектирования импульсных последовательностей на неравных частотах, содермсащее цифро-аналоговый преобразователь, сумматор и де литель частоты -с переменным дробным коэффициентом деления, состоящий из блока управления, делителя частоты и накопительного регистра, к информационному входу которого подключен выход для дробной части коэс1х|)ИЦ11ента N блока управЛения, а выход переполнения накопительного регистра соединен с входом изменения коэффициента деления на единицу блока управления, к входам которого подключены шины кодов АО и АС а выходдля целочисленной части коэффициента f блока управления подключен к первому входу делителя частоты, второй вход которого подключен к первой импульсной последовательности, отличающееся тем, что в него введены блок ключей, запоминающий регистр, фильтр нижних частот,, триггер, элемент ИЛИ и три элемента задержки, через первый из которьк выход делителя частоты подключен к тактовому входу накопительного регистра, выход которого соединен с первымвходом блока ключей и с пер- вым входом сумматора, «торой вход которого подключен к шине кода AQ , и вьрход сумматора соединен с вторым входои блока ключей, управляющие входы которого соединены с выходами триггера, выход - с первым входом .запоминающего регист ра, выход которого через цифро-аналоговый преобразователь подключен к входу фильтра нижних частот, а второй вход соединен с выходом элемента ИЛИ, первьп вход которого соединен непосредственно с выходом делителя частоты и через второй элемент задержки - с первым входом триггера, второй вход которого через третий элемент задержки соединен с шиной второй импульсной последовательности и вторЬш входом элемента ИЛИ.

Источники информации, принятые-во внимание при экспертизе

1.Патент США № 2490500, кл. 250-36, опублик. 6.12.49.

2,Цифровой синтезатор, - ScjeEovctci .s №б, 1973, с. 224-225.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1978 |

|

SU771877A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

Авторы

Даты

1981-11-07—Публикация

1979-11-12—Подача