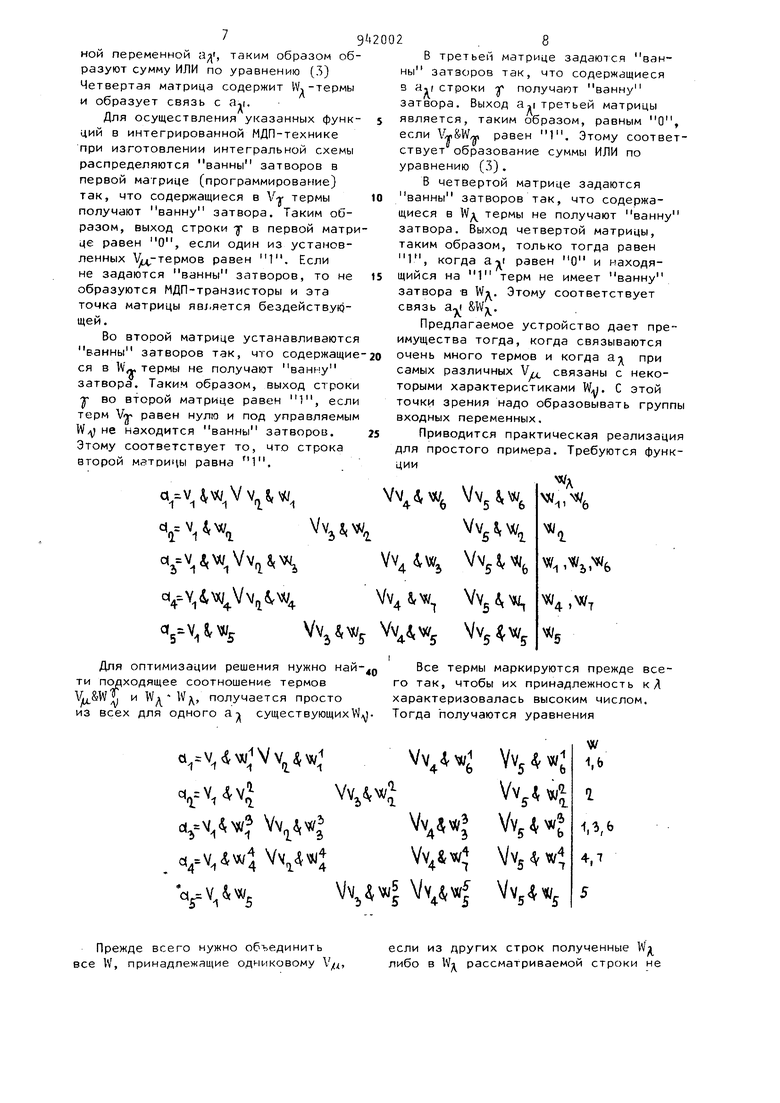

мированием может быть присвоено каждому из m выходов состояние О или 1, так что любая функция может быть задана программированием. Матрица имеет k строк и t столбцов в каждом из m блоков. В точке пересечения строк и столбцов матрицы в соо ветствии с реализуемой функцией вклю чаются интегрированные МДП-транзисторы в процессе изготовления изменением (программированием) шаблона (это соответствует О или 1). При вызове одной из k строк и одного из В столбцов на выходах а,...,а возникает информация, которая запоминается в точке пересечения строк и столбцов. Необходимо всего ячеек в памяти. Так, например, для т 15,50 и k 30 необходимо всего 18000 ячеек в пямяти. Количество блоков информации этого порядка известными средствами не может быть интегрировано совместно с добавочно требуемой логикой управления на одном чипе. Известно также устройство для образования большого количества логических связей - программируемая логи ческая матрица ПЛМ (The integrated circuits catalogue for design engineers. - Texas Instruments, 1971, July). ПЛМ состоит из двух матриц с элементами НЕ-ИЛИ. Первая матрица управ ляется инвертированной входной переменной, а вторая - выходами первой матрицы. Выходы второй матрицы обра зуют инвертированные выходные переменные а,.,.,а. При этом на выхода первой матрицы появляется р fJvTTTv .-.&Сг,. Входные переменные Е,.,., j,,входящие в выходной сигнал Р , определяются в зависимости от того, имеетс ли 8 точке пересечения между строкой и столбцом МДП-транзистор или нет (программирование).Первая матрица об разует таким образом г различных связей И из п входных переменных Е,..., ЕП- Поэтому она называется матрицей И. Выходами второй матрицы являются а-, ./.VPp ; а ...VPp , причем опять образованием или пропус канием МДП-транзисторов в точках пересечения определяется, какой терм Р входит в выходную связь ИЛИ. Поэтому вторая матрица называется матрицей ИЛИ. Чтобы получать меньше избыточности целесообразно группы входных переменных V и W бинарно кодировать к входным сигналам 8,..., е.. При этом п (Cdk + Cdl)- 2. Коэффициент 2 определяется необходимостью применения jU- Для указанного случая п 22. Практические примеры требуют 1000 и больше И-термов Pj. Таким образом, для указанного примера (Рр 1200) необходимо всего точки пересечения, которые практически не интегрируемы на одном чипе. Известные решения имеют тот недостаток, что для осуществления требуемой выходной функции из групп входных переменных затраты на логику и поверхности чипа увеличиваются таким образом, что схема неинтегрируема на одном чипе. Цель изобретения - обеспечение возможности расположения большого количества логических связей двух групп независимых входных переменных в интегрируемой МДП-технике на одном чипе путем минимизации количества логических элементов для большого количества логических связей двух групп независимых входных переменных с исключением некоторых комбинаций. Поставленная цель достигается тем, что в устройстве для вычисления логических функций двух групп из независимых входных переменных в интегрированной МДП-технике, состоящем из нескольких образованных МДПтранзисторами с каналами п- либо Р-типа матриц с элементами НЕ-ИЛИ, причем выводы истоков транзисторов соединены с корпусом, выводы стоков через резистор - с рабочим напряжением и выводы затворов - с входами матриц, а вторая и третья матрицы выполнены в виде ПЛМ, в первой матрице столбцы k соединены соответственно с одной из входных переменных V.,... ,Vi первой группы, а выводы стоков каждой строки - с одним из выходов первой матрицы, выходы первой матрицы подключены к выводам затворов транзисторов г,...,Гс первого столбца второй матрицы, остальные Е столбцов которой соединены соответственно с одной из входных переменных W,..., второй группы. Выводы стоков каждой строки соед нены с одним из выходов второй матрицы, причем последние подключены к выводам затворов транзисторов перво строки четвертой матрицы, остальные t строки которой соединены соответственно с одной из входных переменных второй группы и их выводы стоко каждого столбца - с одним из их выходов. При этом, каждый выход первой и третьей матриц соответственно подкл чен только к выводу затвора одного из транзисторов первого столбца или первой строки второй либо четвертой матрицы. Матрицы могут быть построены так же в логике на дополняющих транзисторах с элементами НЕ-И. На фиг. 1 приведена схема предла гаемого устройства; на фиг. 2 -.при мер конкретного выполнения. , Так как во множестве входных пеiременных V и W-r соответственно только по одному Уд и Wy равен 1, I все возможные входные распределения а могут быть определены уравнениями вида ад , где X 1...т; 1...k; (2) V 1..Л. При этом возникают теоретически m k t (для указанного примера 18000 возможных) уравнения для всех а 1. Практически всегда только часть из aj равна 1. Для сокращения количества уравнений предусмотрены такие логические связи, чтобы объединялись одина овые V- или W-термы. V определяется выражением вида Vy ...V v, W-Y определяется выражением вида W ... V Wg . Для определенного V или W могут отсутствовать любые термы Уд, или ; а л i является вспомогательной переменной и образуется из S-те мов вида 0 ( av И причем ГЗдЯвляется суммой термов ИЛИ, а Vy или Wy МО гут быть равными нулю. Входные переменные Ъ х образуются а X причем W ) определяется выражением вида Wj ... ... V w. , причем любые (для каждого Л другие) термы W; могут отсутствовать Таким образом, выходную переменную можно выразить в виде ал Е У„ Ш.- Ш,. (5) Л Tr-f « т л. Данное уравнение для ад имеет то преимущество, что в Vip&W/« возможно совместить все распределения входов, которые имеют одинаковое W и V, например v w V ,V v Wg V VjW VvjWjV v,,w V v(6 N , или в простом виде УЗ V v)&( Wg). При большом количестве термов (например 18000) обычно образуется много таких подгрупп. Так как для каждого а необходимо образовать свою подгруппу, преимущество еще незначительно. Поэтому для каждого Д. вводится фактор W, который из образованного множества по уравнению (6) может исключать любой терм или несколько одинаковых термов . Этим можно образовывать значительно большее количество одинаковых групп по уравнению (6), так как для любого выхода aj только некоторые содержащиеся в уравнении (6) термы должны быть соответствующими. Для приведенного примера при практической реализации получились только около 2700 необходимых элементов, так что логическая функция может быть выполнена на одном интегированном МДП-чипе. Уравнение (5) осуществляется совместным включением четырех матриц НЕ-ИЛИ. В первой матрице образуется Улч-термы (У строки, k столбцы) .Вторая матрица содержит Wл.-тepмы ( у строки, 1 столбцы) и образует связь Vy &W. Третья матрица присваивает образование связи вспомогатель7ной переменной ад , таким образом образуют сумму ИЛИ по уравнению (3) Четвертая матрица содержит 1Уд-термы и образует связь с . Для осуществления указанных функций в интегрированной МДП-технике при изготовлении интегральной схемы распределяются ванны затворов в первой матрице (программирование) так, что содержащиеся в термы получают ванну затвора. Таким образом, выход строки J в первой матри це равен О, если один из установленных -термов равен 1. Если не задаются ванны затворов, то не образуются МДП-транзисторы и эта точка матрицы яв,яeтcя бездействующей. Во второй матрице устанавливаются ванны затворов так, что содержащие ся в Wrt« термы не получают ванну затвора. Таким образом, выход строки г во второй матрице равен 1, если терм Vy равен нулю и под управляемым Wyy) не находится ванны затворов. Этому соответствует то, что строка второй матрицы равна 1,

Vv. х ч

V1

Для оптимизации решения нужно ти подходящее соотношение термов и WдWд, получается просто из всех для одного а существующих ; Все термы маркируются прежде всего так, чтобы их принадлежность кД характеризовалась высоким числом. Тогда получаются уравнения В третьей матрице задаю1ся ванны затворов так, что содержащиеся 3 а,( строки получают ванну затвора. Выход третьей матрицы является, таким образом, равным О, если V«i&W равен 1. Этому соответствует образование суммы ИЛИ по уравнению (5). В четвертой матрице задаются ванны затворов так, что содержащиеся в W термы не получают ванну затвора. Выход четвертой матрицы, таким образом, только тогда равен 1, когда av равен О и находящийся на 1 терм не имеет ванну затвора -в Wi. Этому соответствует связь а,( &Wj. Предлагаемое устройство дает преимущества тогда, когда связываются очень много термов и когда a;; при самых различных V/ связаны с некоторыми характеристиками WA. С этой точки зрения надо образовывать группы входных переменных. Приводится практическая реализация для простого примера. Требуются функции

| название | год | авторы | номер документа |

|---|---|---|---|

| Каскадное устройство ортогонального типа для сдвигов многоразрядных операндов | 1989 |

|

SU1661757A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Программируемая ассоциативная логическая матрица | 1988 |

|

SU1597934A1 |

| Матричный коммутатор | 1987 |

|

SU1429308A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Спектральный преобразователь электрических сигналов | 1976 |

|

SU690402A1 |

| Матричное коммутационное устройство | 1982 |

|

SU1075409A1 |

| МАТРИЦА ФЛЭШ-ПАМЯТИ С ВНУТРЕННИМ ОБНОВЛЕНИЕМ | 1999 |

|

RU2224303C2 |

Прежде всего нужно объединить все W, принадлежащие одниковому ,

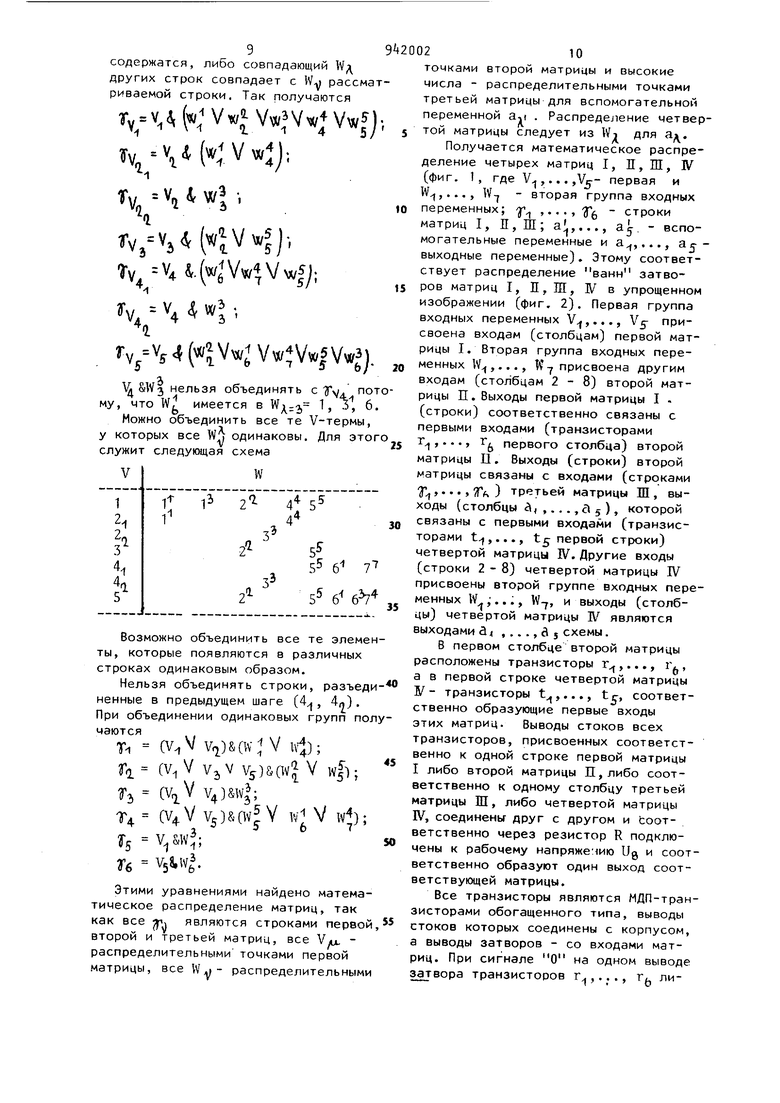

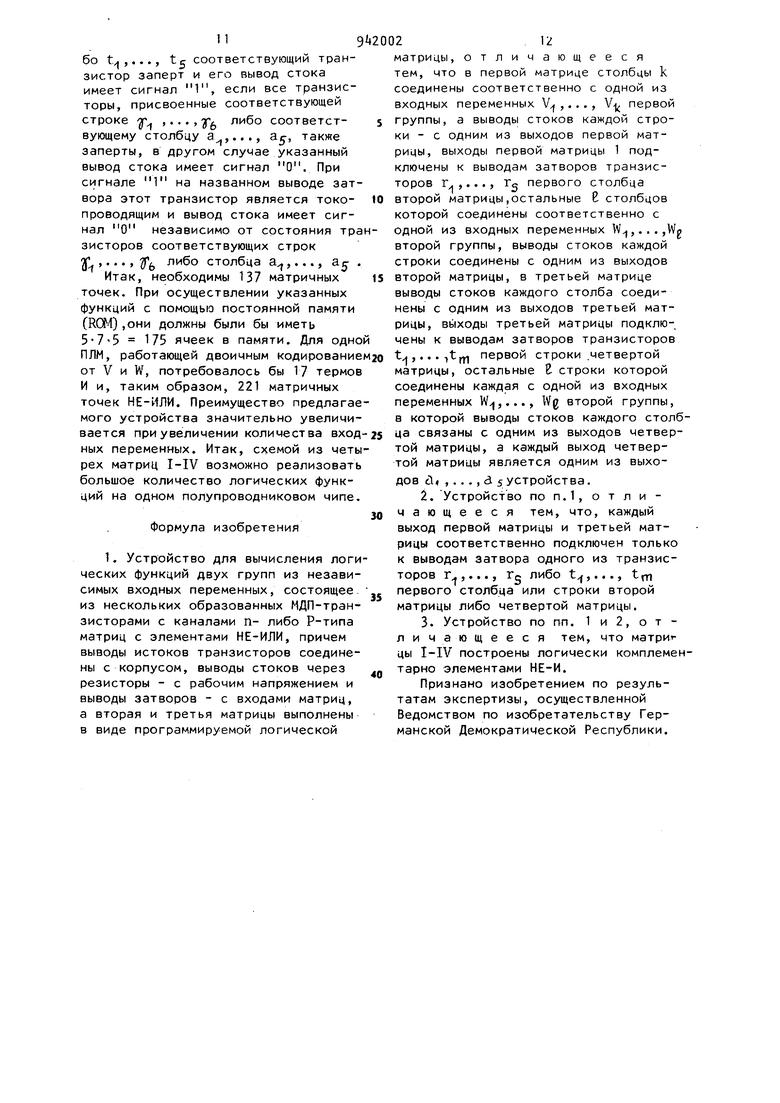

если из других строк полученные Wд либо в Wi рассматриваемой строки не содержатся, либо совпадающий W других строк совпадает с Wy рассмат риваемой строки. Так получаются r,y,a,(w;VwJVv«,Vw|Vwfj rv ; M vw:;j; rv Vj4«V j-, Х, 4.(ws Vw Vwf;i 4 3 Т -V IvC/ Vwf ,,3 VW VW|VW j. Шз нельзя объединять с Ту. пот му, что W имеется в j 3, 6 Можно объединить все те V-термы, у которых все W одинаковы. Для этог служит следующая схема Возможно объединить все те элеме ты, которые появляются а различных строках одинаковым образом. Нельзя объединять строки, разъед ненные в предыдущем шаге (4, 4п). При объединении одинаковых групп пол чаются Т ( V,)&(W, V 1ф; ( VjV V5)&(WJ V wf); Тз ( (V4V V5)&(W|V Wj V W); 5 n V58,W|. Этими уравнениями найдено математическое распределение матриц, так как все являются строками первой второй и третьей матриц, все . распределительными точками первой матрицы, все W,;- распределительными точками второй матрицы и высокие числа - распределительными точками третьей матрицы для вспомогательной переменной aj.t . Распределение четвертой матрицы следует из W-i для а. Получается математическое распределение четырех матриц I, И, Ш, IV (фиг. 1, где V ,... jVg-- первая и ,..., W-J - вторая группа входных переменных; f ,., . , J, - строки матриц I, П, Ш ; aL , могательные переменные и а,..., асвыходные переменные). Этому соответствует распределение ванн затворов матриц I, П, Ш, IV в упрощенном изображении (фиг. 2). Первая группа входных переменных V,..., Vj присвоена входам (столбцам) первой матР I- Вторая группа входных пере„енных W,..., 7 присвоена другим входам (столбцам 2-8) второй матрицы П. Выходы первой матрицы I . (строки) соответственно связаны с первыми входами (транзисторами 1 , г первого столбца) второй матрицы П, Выходы (строки) второй матрицы связаны с входами (строками tTh ) третьей матрицы Ш , выходы (столбцы , ,.. ., с 5 ) которой связаны с первыми входами (транзисторами t ,..., t первой строки) четвертой матрицы IV. Другие входы (строки 2-8) четвертой матрицы IV присвоены второй группе входных переменных IV ..., W-|, и выходы (столбцы) четвертой матрицы IV являются выходами а ,.. .,и 5 схемы. В первом столбце второй матрицы расположены транзисторы г,..., г., а в первой строке четвертой матрицы W- транзисторы t,..., tr, соответственно образующие первые входы этих матриц. Выводы стоков всех транзисторов, присвоенных соответственно к одной строке первой матрицы I либо второй матрицы П,либо соответственно к одному столбцу третьей матрицы Ш, либо четвертой матрицы JV, соединены друг с другом и соответственно через резистор R подключены к рабочему напряжению Ug и соответственно образуют один выход соответствующей матрицы. Все транзисторы являются МДП-транзисторами обогащенного типа, выводы стоков которых соединены с корпусом, а выводы затворов - со входами матриц. При сигнале О на одном выводе г лизатвора транзисторов г 1 , бо t,..., t соответствующий транзистор заперт и его вывод стока имеет сигнал 1, если все транзисторы, присвоенные соответствующей строке -jr ,... , 2Гб либо соответствующему столбцу а,..., а, также заперты, в другом случае указанный вывод стока имеет сигнал О. При сигнале 1 на названном выводе зат вора этот транзистор является токопроводящим и вывод стока имеет сигнал О независимо от состояния тр зисторов соответствующих строк У . fe либо столбца а,..., а Итак, необходимы 137 матричных точек. При осуществлении указанных функций с помощью постоянной памяти () ,они должны были бы иметь 5-75 175 ячеек в памяти. Для одно ПЛМ, работающей двоичным кодирование от V и W, потребовалось бы 17 термов И и, таким образом, 221 матричных точек НЕ-ИЛИ. Преимущество предлагае мого устройства значительно увеличивается при увеличении количества вход ных переменных. Итак, схемой из четы рех матриц I-IV возможно реализовать большое количество логических функций на одном полупроводниковом чипе Формула изобретения 1. Устройство для вычисления логи ческих функций двух групп из независимых входных переменных, состоящее из нескольких образованных МДП-транзисторами с каналами п- либо Р-типа матриц с элементами НЕ-ИЛИ, причем выводы истоков транзисторов соединены с корпусом, выводы стоков через резисторы - с рабочим напряжением и выводы затворов - с входами матриц, а вторая и третья матрицы выполнены в виде программируемой логической матрицы, отличающееся тем, что в первой матрице столбцы k соединены соответственно с одной из входных переменных V,..., V первой группы, а выводы стоков каждой строки - с одним из выходов первой матрицы, выходы первой матрицы 1 подключены к выводам затворов транзисторов г.,..., Го первого столбца второй матрицы,остальные Е столбцов которой соединены соответственно с одной из входных переменных W,.,.,Wp второй группы, выводы стоков каждой строки соединены с одним из выходов второй матрицы, в третьей матрице выводы стоков каждого столба соединены с одним из выходов третьей матрицы, выходы третьей матрицы подклю-, чены к выводам затворов транзисторов t,...-,tj| первой строки .четвертой матрицы, остальные Е строки которой соединены каждая с одной из входных переменных W,j,..., Wg второй группы, в которой выводы стоков каждого столбца связаны с одним из выходов четвертой матрицы, а каждый выход четвертой матрицы является одним из выходов и ,...,d 5 устройства. 2.Устройство по п.1, о т л и чающееся тем, что, каждый выход первой матрицы и третьей матрицы соответственно подключен только к выводам затвора одного из транзисторов г ,..., Гд либо t,..., trn первого столбца или строки второй матрицы либо четвертой матрицы. 3.Устройство по пп. 1 и 2, о т личающееся тем, что матриг цы I-IV построены логически комплементарно элементами НЕ-И. Признано изобретением по результатам экспертизы, осуществленной Ведомством по изобретательству Германской Демократической Республики. j V Vf W, y,, 3 4 S ff 7 фуг. / 9 42002 Of ffg ffj ff fff

Авторы

Даты

1982-07-07—Публикация

1978-02-21—Подача