(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Устройство для деления п-раздельных чисел | 1977 |

|

SU732868A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Матричное устройство для деления | 1983 |

|

SU1141402A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU898423A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

1

Изобретение относится к вычислитепьяой технике н может быть испопьэЬвано в 1да|( вычислительных машинах для двоичных чисел.

Известно устройство для деления чисел в двсвгчном коде без восстановл шя остатка, содержащее сумматор, логаческие схемы И, ИЛИ, схему сочетания аваков. Это устройство обладает сравнительно небольшим быстродействием, так как для определенвя П -цифр частного выпсчшяется П -одинаковых хшкпов. Каждый ШП5П состоит из двух тактов Щ.

Известно также устройство, содержа щее сумматор, счетчик, регисттра, элемеш-ы задержки я элементы И 2j .

Это устройство обладает небольшим быстродействием, так как для получения каждого разряда частного требуется сдав такт, а следовательно, для нолучения П разрядов частного - П тактов.

Известно устройство для деления, содержащее матричный сумматор, элементы И, ИЛИ, триггеры, причем первые

входы сумматоров первого ряда матрицы соединены с иганами разрядов делимого в пря:мом коде, а ко вторым входам сумматоров всех рядов матрицы лодключены шины разрядов делителя в дополни тельном коде, первые входы и выходы сумматоров предыдущего ряда матрицы через соответствующие две группы эле, ментов И н грухшу элеметчэв ИЛИ под.- ключены ко входам сумматоров всех последукошос рядов матрицы со сдвигом на один разряд , прЕГчем управлякшше входы каждой из групп элементов И подсоединены к шинам разрядов частного я ко входу тратгера, соответствующего

ts даянсжгу Р5ЭДУ сумматоров 13 .

Недостатком этого устройства является некотсфая избыточность аппаратуры, связанная, в частности, с наличием в

20 саеме устройства триггеров Шмидта, что также несколько снижает быстродействие устройства.

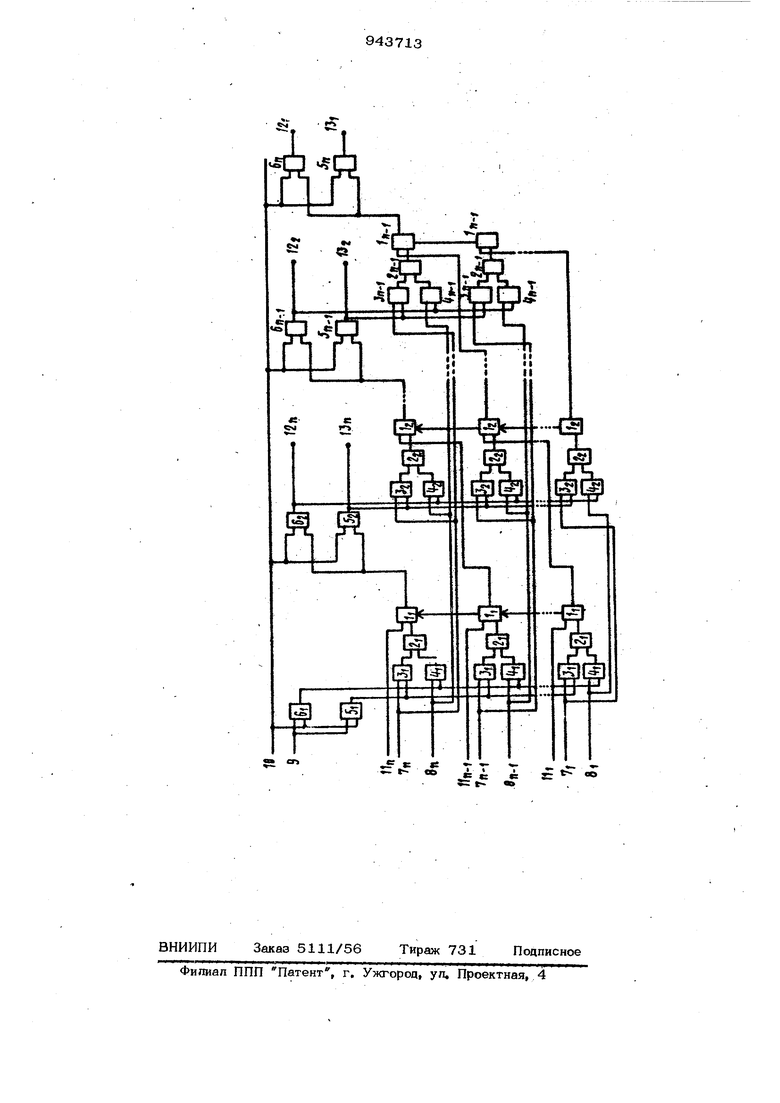

Наиболее близким к изобретению является устройство для деления матричного 3 9 типа, содержащее в каждой ячейке одноразряд1гый сумматор, один вход которого подключен через элемент ИЛИ к выходам двух элементов И, выход одноразрадного сумматора i -ой строки и j -г стспбца матрицы подключен к одном г из входов однора ядного сумматора ( )-й строки и ( -1)-го столбца матрицы, кроме того, в каждой ячейке содержится два сумматора по модуттю два, входы которых в каждой строке матрицы подключены к первой шине управления, вторые входы первого сумматора по модулю два в каждой строке матрицы подключены ко второй шине управления и к одному из входов пертого элемента И, вторые входы вторых сумматоров по модулю два в каждом столбце матрт1Ы подключены к одному из входов второго элемента И и к входу устройства, выходы сумматоров по модулю два подключены к другим входам соответствуюдих элементов И 4 , Недостатком этого устройства является некоторая избыточность обс удования, связанная с его дублированием в каждой ячейке. Цель изобретения - сокращение количества оборудования. Указанная дель достигается тем, что в усттройство для деления, содеркащее (tl -1) двоичных сумматоров (Г) - число разрядсж операндов), элементы И, ИЛИ и НЕРАВН08НАЧНОСТИ, причем первый вход i -го ( -( 1, ... , П ) первого сумматора подключен к шине соответствующего делимого устройства, первый вход каждого разряда j -го сумматора ( j 2, ... , П -1) подключен к выходу предыдущего разряда ( -1)-го сумматора, второй вход каждого разряда k -го сумматора ( k 1, ... , П -l) подключен к выходу соответствующего элемента ИЛИ k -ой группы, входы которого подключены к выходам соответствующих элементов И k -и и 2 k гй групп, первый вход каждого элемента И k -и группы соединен с шиной соответствующего разряда делителя устройства, выход первогю элемента НЕРАВНОЗНАЧНСХ:ЛИ соединен с вторым входом старшего элемента И первой группы, выход старшего разряда k -го сумматора соедипЁен с первым входом (k + 1)-го элемента НЕРАВНОЗНАЧНОСТИ, выход которого соединен с первым входом старшего элемента И (k+l группы, введе}1Ы элементы РАВНОЗНАЧ34НСХ:ТИ, причем входы первых элементов НЕРАВНШНАЧНОСТИ и РАВНОЗНАЧНОСТИ подключены к шинам знаковых разрядов делимого и делителя устройства, выход первого элемента НЕРАВНОЗНАЧНОСТИ соединен с вторыми входами младших элементов И первой группы, первые входы элементов И 2 k -и группы соединены с шинами соответствук ших разрядов дополнительного кода делителя, вторые вхрды элементов И 2k -и группы соединены с выходом k -го элемента РАВНОЗНАЧНОСТИ, входы 2 -го элемента РАВНСвНАЧНОСГИ ( 6 2, ... , П ) соединены с выходом старшего разряда ( f -1)-го сумматора и шзшой знакового разряда делителя устройства, второй вход -го элемента НЕРАВНОЗНАЧНОСТИ соединен с шиной знакового разряда делителя устройства. На чертеже представлена схема устройства. Устройство содержит 11 -1 сумматоР°® - -n-f -П 1 ipyiUI элемейтов ИЛИ 2|, 22/ ... 2f ; 2(11-1) групп элементов И 3, 82, ... , Зц- ; 4|, 42, ... , 4п- I элементы НЕРАВНОЗНАЧНОСТИ 5, 52, ... , 5п- , 5f,, элементы РАВНОЗНАЧНОСТИ 6.{. б2, . г ®П t шинь 7-(, ... , 7f).( , 7п делителя (прямого кода); щины 8, ... , 8n.j, 8f дополнительного кода делителя; шины 9 и 10 знаковых делимого и делителя; шины 11 делимого; .f . 1 шины етгачений 12, 122, ... , 12, 13, 132, ... , 13 (-| прямого и инверсного частного. Устройство работает следующим образом. Шерация деления начинается с анализа делимого и делителя, которые подаются по шинам 9 и 10 на элементы НЕРАВНОЗНАЧНОСТИ 5, к РАВ- . НОЗНАЧНОСТИ 6. Если знаки одинаковые, то срйбатьдаает элемент РАВНОЗНАЧНОСТИ 6 f и группа элементов И , н на вход сумматора 1 подается делитель в дополнительном коде, который поступает по шинам 8. Если же знаки делимого и делителя не совпадают, то срабатывает элемент НЕРАВНОЗНАЧНОСТИ 5 yf и- срабатывает группа элементов И 3 , и на вход сумматора 1 подается делитель в прямом коде по шинам 7. На другие входы всех разрядов сумматоров 1, 12 ... , подается ;Код делимого по шинам 11. Знак остатка с выхода старшего разряда cyMNiaTOpa 10 подается на элементы НЕРАВНОЗНАЧНОСТИ 42 и РАВНОЗНАЧНОСТИ 52, на дру1Ие входы которых подается знак делителя с шины Ю. Происходит сравнение знаков остатка и децитепя, если знаки совпадают в знаковый разряд частного по нишам 12 и 13 залнсывается единица, если знаки не совпадают - нуль, одновременно срабатывает схема РАВНОЗНАЧНОСТИ 52 или НЕРАВНОЗНАЧНОСТИ 42 соответственно, которые разрешают подачу на вторые входь сумматоров 10 2 второго столбца матрицы прямогчэ шш допошштельиого кода делителя. Последующие цифры частного получаются аналогичным образом. Преимущество предложенного устройства по сравнению с известным заключается в некотором уменьшении оборудо за счет исключения его дублирования в Каждой ячейке. Формула изобретения Устройство для деления, содержащее (n-l) двоичных сумматоров {п- число разрядов операндов), элементы И, ИЛИ и НЕРАВНОЗНАЧНОСТИ, причем первый вход -го разряда ( -i 1, ..., П ) первого сумматора подключен к шине соответствукяцего разряда делимого уст ройства, первый вход каждого разряда j -го сумматора ( j 2, ... , h -1) подкяючен к выходу предыдущего разряда ( j -1)-го сумматора, второй вход ка кдого разряда k -го сумм атора (k 1, ... , П -1) подключен к выходу соответствующего элемента ИЛИ k -ой группы, входы которого подключены к выходам соответствующих элементов И k -и и 2 k -и групп, первый вход каждог элемента И k -и группы соединен с щино соответствующего разряда делителя уст36ройства, выход первого элемента HEPABii НОЗНАЧНОСТИ соединен с вторым входсзм старшего элемента И первой группы, выход старщего разряда k -го сумматора соединен с первым входом (k+l)-ro элемента НЕРАВНОЗНАЧНОСТИ, выход которого соединен с первым входом старшего элемента И ( k +1)-й группы, отличающееся тем, что, с целью сокращения количества оборудования, оно содер«{ит элементы РАВНО ЗНАЧНОСТИ, причем входы первых элементов НЕРАВНОЗНАЧНОСТИ И PABHOu ЗНАЧНОСТИ подкгаочены к шинам знаковых разрядов делимого и делителя устройства, выход первого элемента НЕРАВНОЗНАЧНОСТИ соединен с вторыми входами младщих элементов И первой группы, первые входы элементов И 2 k -и группы соединены с шинами соответствующих разрядов дополнительного кода делзателя, втсфые входы элгалентов И 2 k -и группы соединены с выходом k -го элемента РАВНОЗНАЧНОСТИ, входы 6 -го элемента РАВНОЗНАЧНОСТИ ( 6 2, ... , П ) соединены с выходом стары ах разряда ( t -1)-го сумматора и шиной знакового раз)ряда делителя устройства, второй вход 2 -го элемента НЕРАВНОЗНАЧНОСТИ соединен с.щшюй знакового разряда делителя устройства. Источники инфсрмадии, принятые во внимание при экспертизе 1.Папернов А. А. Логические основы ЦВТ. М., Советское радио , 1972, с. 225-236. 2.Самофалов К. Г. и др. Электронные ЦВМ, Киев, Витти щкола 1976, с. 325-ЗЗО, 3.Авторское свидетельство СССР J 36О663, КЛ.О 06 Р 7/52, 1970. 4.Авторское свидетельство СССР № 543937, кл, G 06 Р 7/38, 1975 :{ирототшг).

Авторы

Даты

1982-07-15—Публикация

1978-07-03—Подача