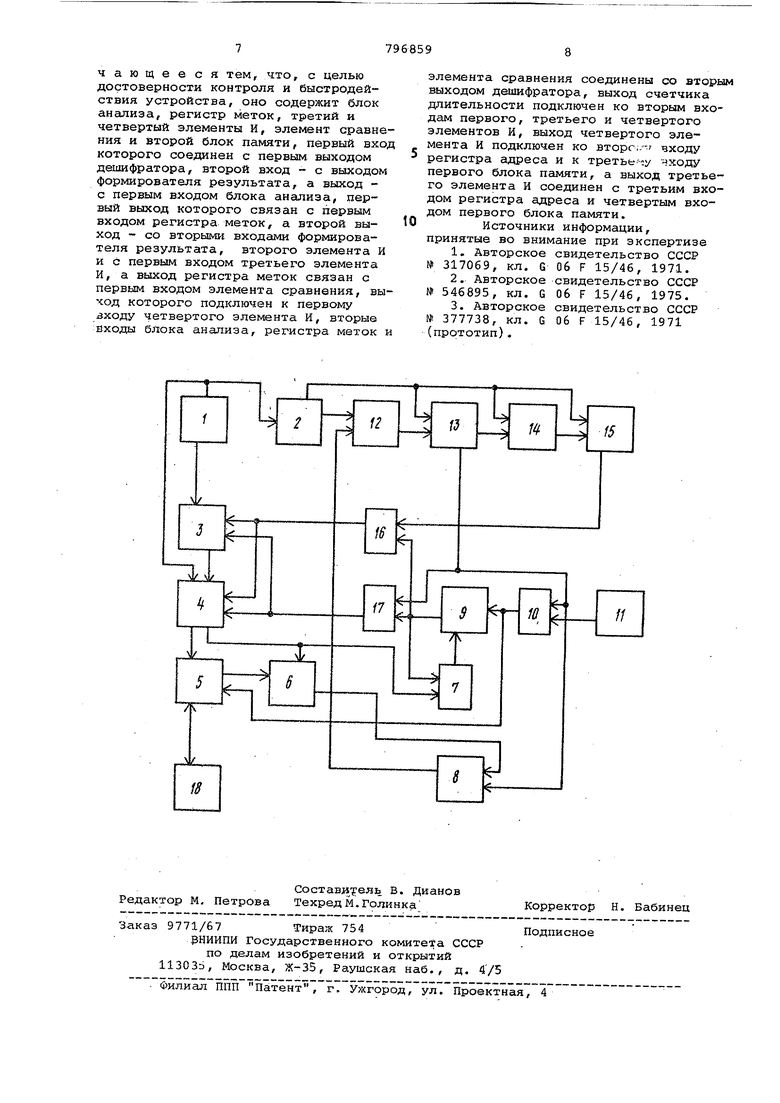

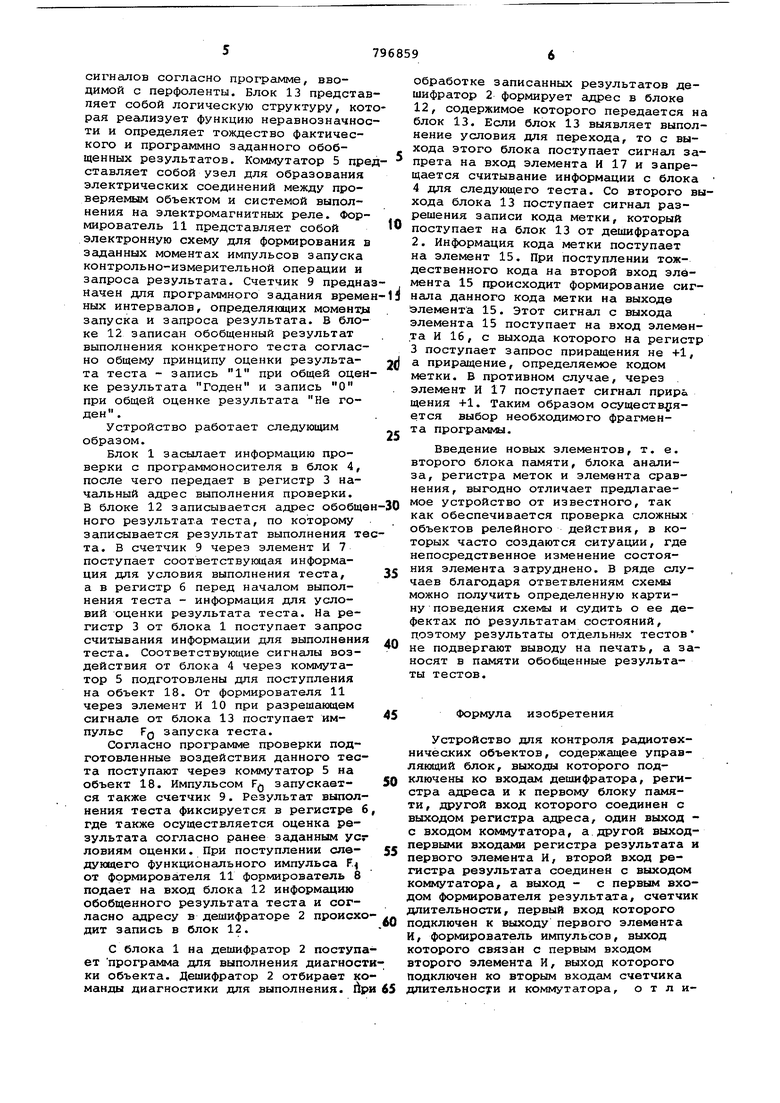

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОТЕХНИЧЕСКИХ ОБЪЕКТОВ сов, соответствующих первому состоянию объекта. На счетчик приближений последовательно во времени поступают компоненты вектора l с присвоенными им весами, и на счетчике после сумми рования фиксируется значение функции приближения вектора X первому состоя нию объекта 2 . Для данного устройства необходим оператор определения соответствующе состояния объекта, что значительно уменьшает производительность устройства при выполнении проверки объек- та в автоматическом режиме. Наиболее близким к предлагаемому устройству является система автоматического контроля больших интеграль ных схем, содержащая управляющую вычислительную машину (УВМ), которая передает в счетчик адреса памяти начальный адрес ячейки запоминающего устройства, в которой хранится первая тестовая комбинация для контроли руемой схемы. В регистр сщреса контролируемой тестовой комбинации записывается адрес комбинации, на которой требуется зафиксировать выходные сигналы контролируемой схемы. В регистр выходной тестовой комбинации из запоминающего устройст ва (ЗУ)выходных тестовых комбинаций входящего в состав УВМ, поступает вы ходная тестовая комбинация, соответс вующая выходным сигналам контролируе мой схемы на указанном номере тестовой комбинации. В каждой ячейке ЗУ выделены разряды для записи информации длительности поступления данной тестовой комбинации 3. При заполнении счетчика длительности наращивается на 1 счетчик адреса ЗУ по следугацему адресу.- На требуемом номере цикла запрещается прохождение тактовых импульсов на счетчик длительности, подается стробирующий импульс на дискриминатор и начинается исследование выходных сигналов. Однако в известной системе продолжение выполнения программы проверки осуществляется без анализа про межуточных результатов и оперативно го принятия решения, что при большом количестве тестовых комбинаций умен шает общую производительность. Цель изобретения - увеличение бы стродействия проверки достоверности результатов контроля путем определе ния места неисправности в случае, когда к проверяемому элементу нет прямого доступа. Указанная цель достигается тем, что устройство для контроля радиотехнических объектов, содержащее управляющий блок, выходы которого подключены ко входам дешифратора, регистра адреса и к первому блоку памяти, другой вход которого соединен с выходом регистра адреса, один вьрсод - с входом коммутатора, а другой выход - с первыми входами регистра результата и первого элемента И, второй вход регистра результата соединен с выходом коммутатора, а выход - с первым.входом формирователя результата, счетчик длительности, первый вход которого подключен к выходу первого элемента И, формирователь импульсов, выход которого связан с первым входом второго элемента И, вьлход которого подключен ко вторым входам счетчика длительности и коммутатора, содержит блок анализа, регистр меток, третий и четвертый элементы И, элемент сравнения и второй блок памяти, первый вход которого соединен с первым выходом дешифратора, второй вход с выхсЗдом формирователя результата, а выход - с первым входом блока анализа, первый выход которого связан с первым входом регистра меток, а второй выход - со вторыми входами формирователя результата, второго элемента И и с первым входом третьего элемента И, а выход регистра меток связан с первым входом элемента сравнения, выход которого подключен к первому входу четвертого элемента И, вторые входы блока анализа, регистра меток и элемента сравнения соединены со вторым выходом дешифра-. тора, выход счетчика длительности подключен ко вторым входам первого, третьего и четвертого элементов И, выход четвертого элемента И подключен ко второму входу регистра адреса и к третьему входу первого блока памяти, а выход третьего элемента И соединен с третьим входом регистра адреса и четвертым входом первого блока памяти. На чертеже приведена функциональная схема устройства. Устройство содержит управляющий блок 1, выходами подключенный ко входам дешифратора 2, регистра 3 адреса и к первому входу первого блока 4 памяти, первый выход которого связан с .первым входом коммутатора 5, а другой-выход - с.первыми входами регистра б результата и первого элемента И 7, а.выход регистра 6 соединен с первым входом формирователя 8 результата, счетчик $ длительности, второй элемент И 10, связанный с выходом формирователя 11 импульсов, второй блок 12 памяти, выход которого подключен к первому входу блока 13 анализа, первый выход которого связан с регистром 14 меток, четвертый логический элемент И 16, третий логический элемент И 17 и контрольный объект 18. Блок 1 представляет сооои автомат дискретного действия, выполненный на дискретных логических элементах, и служит для выработки управляющих

сигналов согласно программе, вводимой с перфоленты. Блок 13 представляет собой логическую структуру, которая реализует функцию неравнозначности и определяет тождество фактического и программно заданного обобщенных результатов. Коммутатор 5 представляет собой узел для образования электрических соединений между проверяемым объектом и системой выполнения на электромагнитных реле. Формирователь 11 представляет собой электронную схему для формирования в заданных моментах импульсов запуска контрольно-измерительной операции и запроса результата. Счетчик 9 предназначен для программного задания времен ных интервалов, определяющих моменту запуска и запроса результата. В блоке 12 записан обобщенный результат выполнения конкретного теста согласно общему принципу оценки результата теста - запись 1 при общей оценке результата Годен и запись О при общей оценке результата Не годен.

Устройство работает следующим образом.

Блок 1 засылает информацию проверки с программоносителя в блок 4, после чего передает в регистр 3 начальный адрес выполнения проверки. В блоке 12 записывается адрес обобщвн ного результата теста, по которому записывается результат выполнения теста. В счетчик 9 через элемент И 7 поступает соответствующая информация для условия выполнения теста, а в регистр 6 перед началом выполнения теста - информация для условий оценки результата теста. На регистр 3 от блока 1 поступает запрос считывания информации для выполнения теста. Соответствующие сигналы воздействия от блока 4 через коммутатор 5 подготовлены для поступления на объект 18. От формирователя 11 через элемент И 10 при разрешающем сигнале от блока 13 поступает импульс FQ запуска теста.

Согласно программе проверки подготовленные воздействия данного теста поступают через коммутатор 5 на объект 18. Импульсом FQ запускается также счетчик 9. Результат выполнения теста фиксируется в регистре 6, где также осуществляется оценка результата согласно ранее заданным усг ловиям оценки. При поступлении еледующего функционального импульса F. от формирователя 11 формирователь 8 подает на вход блока 12 информацию обобщенного результата теста и согласно адресу в дешифраторе 2 происходит запись в блок 12.

С блока 1 на дешифратор 2 поступает программа для выполнения диагностики объекта. Дешифратор 2 отбирает команды диагностики для выполнения, йртл

обработке записанных результатов дешифратор 2 формирует адрес в блоке 12, содержимое которого передается н блок 13. Если блок 13 выявляет выполнение условия для перехода, то с выхода этого блока поступает сигнал запрета на вход элемента И 17 и запрещается считывание информации с блока 4 для следующего теста. Со второго входа блока 13 поступает сигнал разрешения записи кода метки, который поступает на блок 13 от дешифратора 2. Информация кода метки поступает на элемент 15. При поступлении тождественного кода на второй вход элемента 15 происходит формирование сигнала данного кода метки на выходе Элемента 15. Этот сигнал с выхода элемента 15 поступает на вход элемента И 16, с выхода которого на регистр 3 поступает запрос приращения не +1, а приращение, определяемое кодом метки. В противном случае, через элемент И 17 поступает сигнал прирь щения +1. Таким образом осуществ яется выбор необходимого фрагмента программы.

Введение новых элементов, т. е. второго блока памяти, блока анализа, регистра меток и элемента сравнения , выгодно отличает предлагаемое устройство от известного, так как обеспечивается проверка сложных объектов релейного действия, в которых часто создаются ситуации, где непосредственное изменение состояния элемента затруднено. В ряде случаев благодаря ответвлениям схемы можно получить определенную картину поведения схемы и судить о ее дефектах по результатам состояний, поэтому результаты отдельных тестов не подвергают выводу на печать, а заносят в памяти обобщенные результаты тестов.

Формула изобретения

Устройство для контроля радиотехнических объектов, содержащее управляющий блок, выходы которого подключены ко входам дешифратора, регистра адреса и к первому блоку памяти, другой вход которого соединен с выходом регистра адреса, один выход с входом коммутатора, а другой выходпервыми входами регистра результата и первого элемента И, второй вход регистра результата соединен с выходом коммутатора, а выход - с первым входом формирователя результата, счетчик длительности, первый вход которого подключен к выходу первого элемента И, формирователь импульсов, выход которого связан с первым входом второго элемента И, выход которого подключен ко вторым входам счетчика длительности и коммутатора, о т л ичающееся тем, что, с целью достоверности контроля и быстродействия устройства, оно содержит блок анализа, регистр меток, третий и четвертый элементы И, элемент сравнения и второй блок памяти, первый вхо которого соединен с первым выходом дешифратора, второй вход - с выходом формирователя результата, а выход с первым входом блока анализа, первый выход которого связан с первым входом регистра меток, а второй выход - со вторыми входами формирователя результата, второго элемента И и с первым входом третьего элемента И, а выход регистра меток связан с первым входом элемента сравнения, вычод которого подключен к первому входу четвертого элемента И, вторые :йходы блока анализа, регистра меток

элемента сравнения соединены со вторым выходом дешифратора, выход счетчика длительности подключен ко вторым входам первого, третьего и четвертого элементов И, выход четвертого элемента И подключен ко вторг.--- входу регистра адреса и к третье .у чходу первого блока памяти, а выход третьего элемента И соединен с третьим входом регистра адреса и четвертым входом первого блока памяти.

0

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 317069, кл, G 06 F 15/46, 1971.

2.Авторское свидетельство СССР № 546895, кл. G Об F 15/46, 1975.

3.Авторское свидетельство СССР № 377738, кл. G Об F 15/46, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для автоматического контроля больших интегральных схем | 1981 |

|

SU1027735A1 |

| Устройство для тестового контроля цифровых узлов | 1980 |

|

SU918949A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Авторы

Даты

1981-01-15—Публикация

1979-02-23—Подача