сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1406640A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ РАБОТОСПОСОБНОСТИ ОБЪЕКТОВ | 1992 |

|

RU2036505C1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля сохранности информации в блоках постоянной памяти, В предложенном решении используется принцип сравнения информации, считанной с проверяемого и эталонного блоков памяти. Устройство позволяет производить контроль блоков постоянной памяти непосредственно во время работы их в различных устройствах и при воздействии внешних факторов. Это достигается тем, что в устройство, содержащее блок сравнения, блок эта- лонной памяти, коммутатор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик, элементы И, ИЛИ, триггер, введены элемент ИЛИ, регистры данных и адреса, блок оперативной памяти, соединенные определенным образом. Устройство позволяет производить диагностику неисправности в работающих блоках постоянной памяти и 1 выявлять любой характер ошибки. 3 ил.

Предлагаемое устройство относится к автоматике и вычислительной технике и может быть использовано для контроля сохранности информации в блоках постоянной памяти.

Целью предлагаемой заявки является расширение области применения устройства.

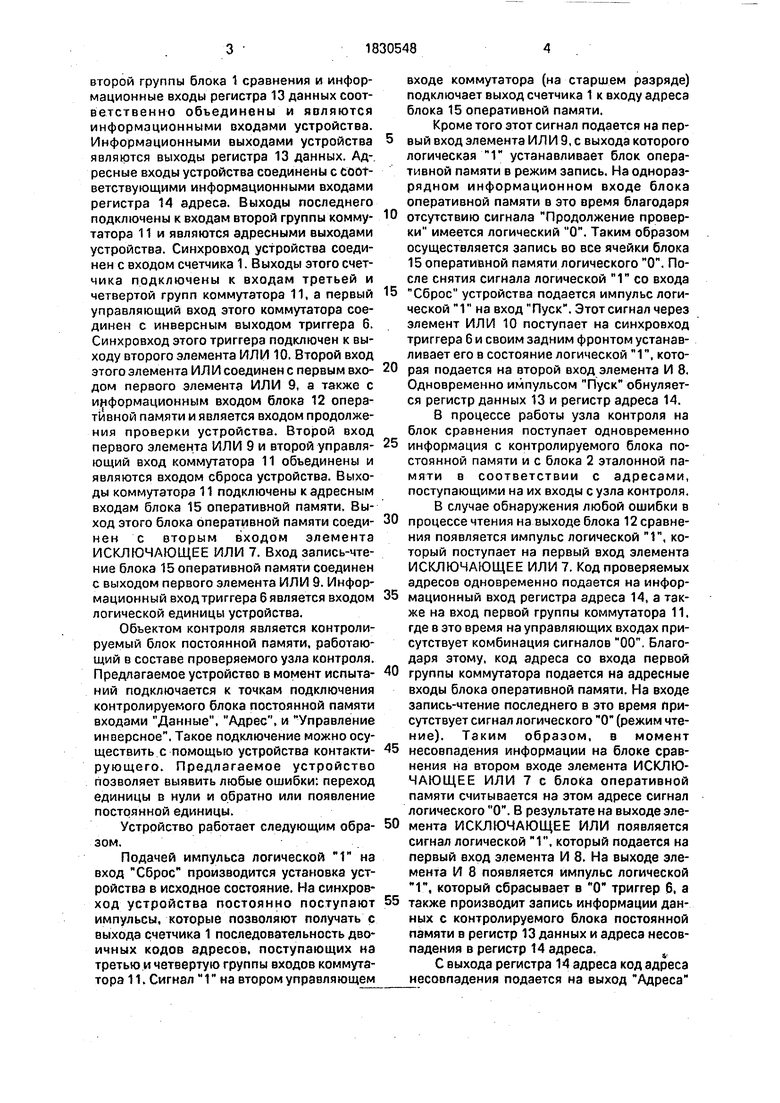

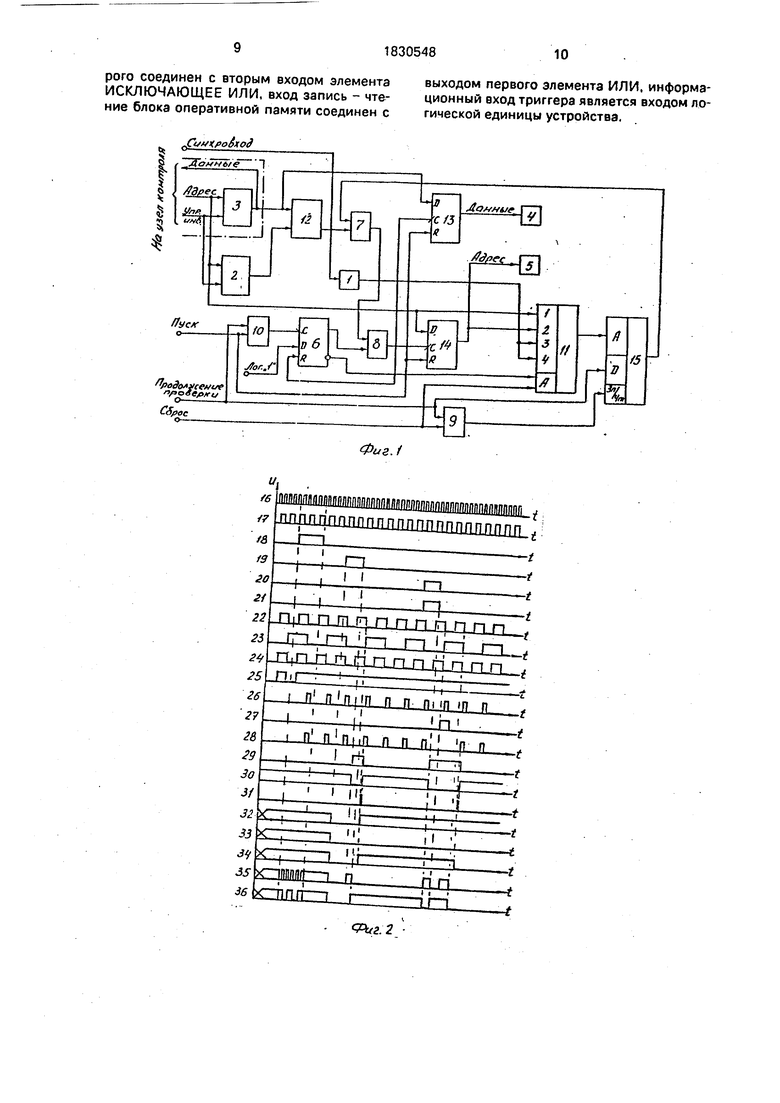

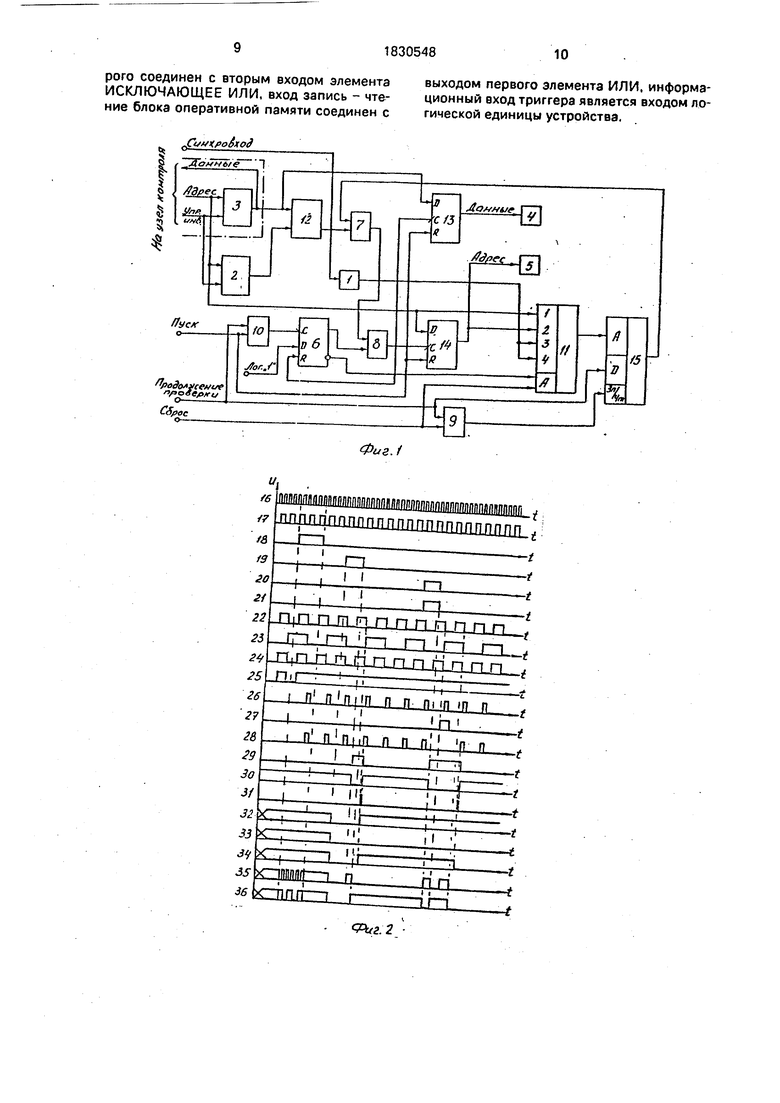

На фиг. 1 представлена структурная схема устройства для контроля блоков постоянной памяти; на фиг. 2 - временные диаграммы одного цикла работы устройства.

Устройство содержит блок 12 сравнения, блок 2 эталонной памяти, коммутатор 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7. счетчик 1, первый 9 и второй 10 элементы ИЛИ, элемент И 8, триггер 6, регистр 13 данных, регистр 14 адреса и блок 15 оперативной памяти.

Входы первой группы коммутатора 11 и адресные входы блока 2 эталонной памяти соответственно объединены и являются адресными входами устройства. Инверсным входом управления устройства является вход выборки блока 2 эталонной памяти. Выходы блока 2 эталонной памяти подключены к входам первой группы блока 12 сравнения. Выход блока 12 сравнения соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 соединен с первым входом элемента И 8, выход которого соединен с синхровходами регистра 13 данных и регистра 14 адреса и входом сброса триггера 6. Прямой выход триггера 6 соединен с вторым входом элемента И 8. Первый вход второго элемента ИЛИ 7 и входы сброса регистра 14 адреса и регистра 10 данных объединены и являются входом пуска устройства. Входы

оо со о сл

Ь

00

второй группы блока 1 сравнения и информационные входы регистра 13 данных соответственно объединены и являются информационными входами устройства. Информационными выходами устройства являются выходы регистра 13 данных. Ад-, ресные входы устройства соединены с соответствующими информационными входами регистра 14 адреса. Выходы последнего подключены к входам второй группы комму- татора 11 и являются адресными выходами устройства. Синхровход устройства соединен с входом счетчика 1. Выходы этого счетчика подключены к входам третьей и четвертой групп коммутатора 11, а первый управляющий вход этого коммутатора соединен с инверсным выходом триггера 6. Синхровход этого триггера подключен к выходу второго элемента ИЛИ 10. Второй вход этого элемента ИЛ И соединен с первым вхо- дом первого элемента ИЛИ 9, а также с информационным входом блока 12 оперативной памяти и является входом продолжения проверки устройства. Второй вход первого элемента ИЛИ 9 и второй управля- ющий вход коммутатора 11 объединены и являются входом сброса устройства. Выходы коммутатора 11 подключены к адресным входам блока 15 оперативной памяти. Выход этого блока оперативной памяти соеди- нен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Вход запись-чтение блока 15 оперативной памяти соединен с выходом первого элемента ИЛИ 9. Информационный вход триггера 6 является входом логической единицы устройства.

Объектом контроля является контролируемый блок постоянной памяти, работающий в составе проверяемого узла контроля. Предлагаемое устройство в момент испыта- ний подключается к точкам подключения контролируемого блока постоянной памяти входами Данные, Адрес, и Управление инверсное. Такое подключение можно осуществить с помощью устройства контакти- рующего. Предлагаемое устройство позволяет выявить любые ошибки; переход единицы в нули и обратно или появление постоянной единицы.

Устройство работает следующим обра- зом.

Подачей импульса логической Г на вход Сброс производится установка устройства в исходное состояние. На синхров- ход устройства постоянно поступают импульсы, которые позволяют получать с выхода счетчика 1 последовательность двоичных кодов адресов, поступающих на третью и четвертую группы входов коммутатора 11. Сигнал 1 на втором управляющем

входе коммутатора (на старшем разряде) подключает выход счетчика 1 к входу адреса блока 15 оперативной памяти.

Кроме того этот сигнал подается на первый вход элемента ИЛИ 9, с выхода которого логическая 1 устанавливает блок оперативной памяти в режим запись. На одноразрядном информационном входе блока оперативной памяти в это время благодаря отсутствию сигнала Продолжение проверки имеется логический О. Таким образом осуществляется запись во все ячейки блока 15 оперативной памяти логического О. После снятия сигнала логической Г со входа Сброс устройства подается импульс логической 1 на вход Пуск. Этот сигнал через элемент ИЛИ 10 поступает на Синхровход триггера 6 и своим задним фронтом устанавливает его в состояние логической 1, которая подается на второй вход элемента И 8. Одновременно импульсом Пуск обнуляется регистр данных 13 и регистр адреса 14.

В процессе работы узла контроля на блок сравнения поступает одновременно информация с контролируемого блока постоянной памяти и с блока 2 эталонной памяти в соответствии с адресами, поступающими на их входы с узла контроля.

В случае обнаружения любой ошибки в процессе чтения на выходе блока 12 сравнения появляется импульс логической Г, который поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Код проверяемых адресов одновременно подается на информационный вход регистра адреса 14, а также на вход первой группы коммутатора 11. где в это время на управляющих входах присутствует комбинация сигналов 00. Благодаря этому, код адреса со входа первой группы коммутатора подается на адресные входы блока оперативной памяти. На входе запись-чтение последнего в это время присутствует сигнал логического О (режим чтение). Таким образом, в момент несовпадения информации на блоке сравнения на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 с блока оперативной памяти считывается на этом адресе сигнал логического О. В результате на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ появляется сигнал логической 1, который подается на первый вход элемента И 8. На выходе элемента И 8 появляется импульс логической 1, который сбрасывает в О триггер б, а также производит запись информации данных с контролируемого блока постоянной памяти в регистр 13 данных и адреса несовпадения в регистр 14 адреса.

С выхода регистра 14 адреса код адреса несовпадения подается на выход Адреса

устройства, а также на вторую группу входов коммутатора, а с выхода регистра 13 данных - на выход Данные устройства. Таким образом, на выходах устройства появится информация данных и код адреса ячейки, в которой имеется ошибка. В этом случае имеется возможность проконтролировать информацию, считанную с ячейки контролируемого блока постоянной памяти, в которой имеет место сбой, с табличными данными, по которым производилась начальная запись информации в контролируемый блок постоянной памяти.

После обнаружения первой ячейки памяти, в которой имеется несоответствие информации, подается импульс логической 1 на вход Продолжение проверки устройства. Этот сигнал через элемент ИЛИ 10 подается на синхровход триггера б, а также поступает на информационный вход блока оперативной памяти и через элемент ИЛИ 9 на вход запись - чтение этого блока обеспечивая режим записи.

Во время действия импульса Продолжение проверки триггер 9 остается в состоянии О, и на первом управляющем входе коммутатора (младшем разряде) присутствует сигнал логической Г. На адресные входы блока оперативной памяти в это время через вторую группу входов коммутатора 11 подается код адреса ячейки, в которой был обнаружен сбой информации.

Таким образом, по этому адресу в блоке оперативной памяти по сигналу Продолжение проверки производится запись логической 1.

По заднему фронту импульса Продолжение проверки, поступающему через элемент ИЛИ 10 на синхровход триггера б, производится установка последнего в состояние 1, и на втором входе элемента И 8 появится сигнал логической 1.

Устройство подготовлено к обнаружению следующей ячейки, в которой будет несовпадение. При несовпадении информации в следующей какой-либо ячейке необходимо снова подать импульс Продолжение проверки и описанным выше образом записать в блок оперативной памяти по обнаруженному адресу логическую 1.

Таким образом, каждый раз при подаче сигнала Продолжение проверки обеспечивается маскирование обнаруженных ячеек, в которых выявлено несовпадение информации. Это позволяет после сигнала Продолжение проверки обнаруживать только новые ячейки, содержащие ошибки, так как при несовпадении информации по обнаруженным ранее ячейкам на второй

вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ будет подаваться с блока оперативной памяти всегда информация 1, а на его выходе присутствует информация О. 5Наличие информации О на первом

входе элемента И 8, не позволяет на обнаруженных ранее адресах получить с выхода элемента И 8 положительный импульс несовпадения, Сигнал Продолжение провер0 ки подается до тех пор, пока не будут обнаружены все дефекты ячейки.

Цикл проверки можно повторить, если подать последовательно импульсы логической 1 на входы Сброс и Пуск устрой5 ства. Импульсом Сброс производится запись во все ячейки блока оперативной памяти информации О (стирание логических 1 в ячейках по адресам сбоя), а импульсом Пуск устройство приводится в исходное

0 состояние.

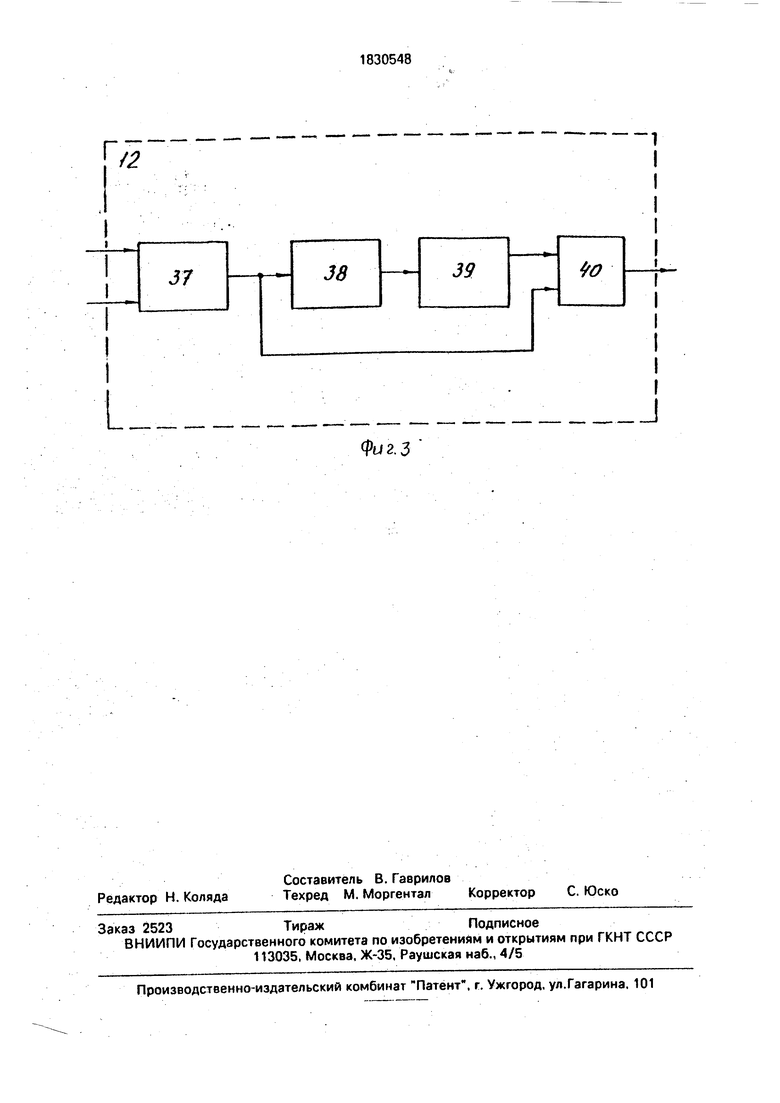

Для упрощения построения временных диаграмм на фиг. 2 приняты следующие допущения. Блок 2 эталонной памяти и контролируемый блок постоянной памяти имеют

5 объем памяти 4 х 1 бит. Таким образом, вход Адрес устройства, выход регистра 14. выход коммутатора 11, выход счетчика 1 имеют два двоичных разряда.

Выход Данные устройства, а также

0 вход регистра 13 имеют один двоичный разряд. Информационные выходы блока 2 эталонной памяти, контролируемого блока постоянной памяти (входы Данные устройства), а также выход регистра 13 имеют

5 один информационный разряд,

На фиг. 2 показаны импульсы 16, 17 на выходе счетчика (первый и второй разряды соответственно), импульсы 18 - на входе

0 Сброс устройства, импульсы 19 - на входе Пуск устройства, импульсы 20 - на входе Продолжение проверки устройства, импульсы 21 - на входе запись - чтение блока оперативной памяти, импульсы 22, 23 - на

5 входе Адрес устройства (первый и второй разряды соответственно), импульсы 24 - на выходе блока 2 эталонной памяти, импульсы 25 - на входе Данные устройства, импульсы 26 - на выходе блока 12 сравнения, им0 пульсы 27 - на выходе блока 15 оперативной памяти, импульсы 28 - на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7, импульсы 29, 30 - на выходе триггера 6 (прямой и инверсный выходы соответственно), импульсы 31 - на

5 выходе элемента И 8, импульсы 32 - на выходе регистра 13 данных, импульсы 33 и 34 - на выходе регистра 14 адреса (первый и второй разряд соответственно), импульсы 35 и 36 - на выходе коммутатора 11 (первый и второй разряды соответственно).

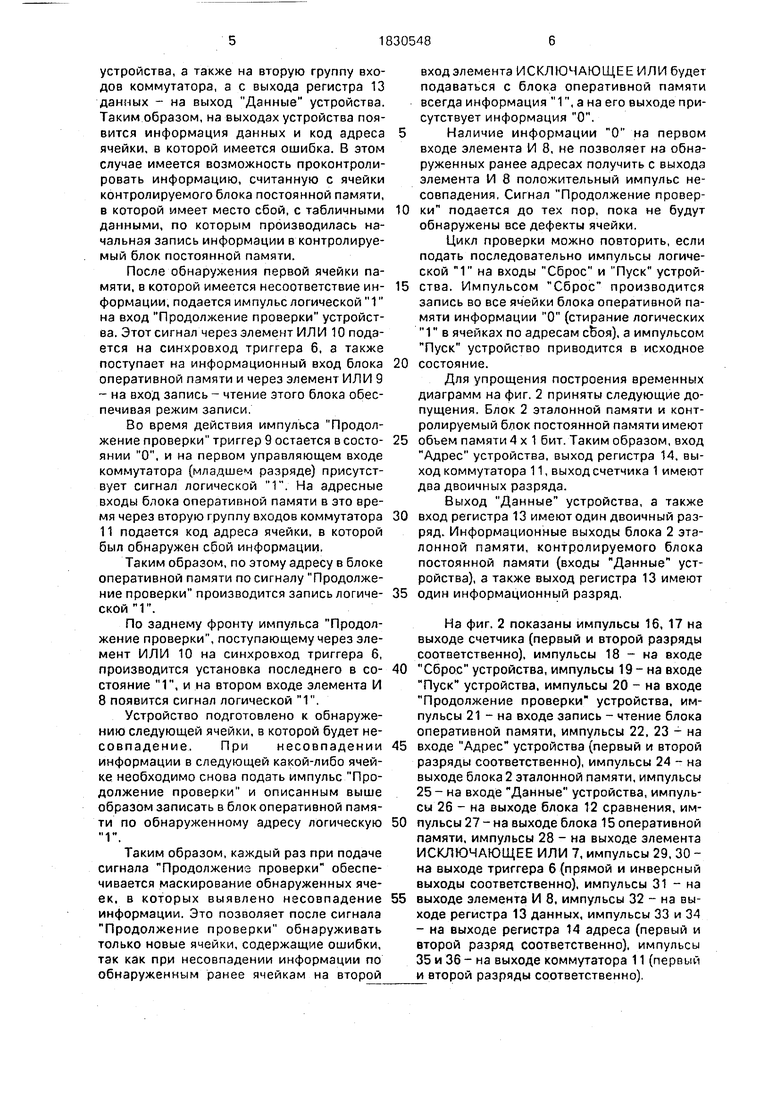

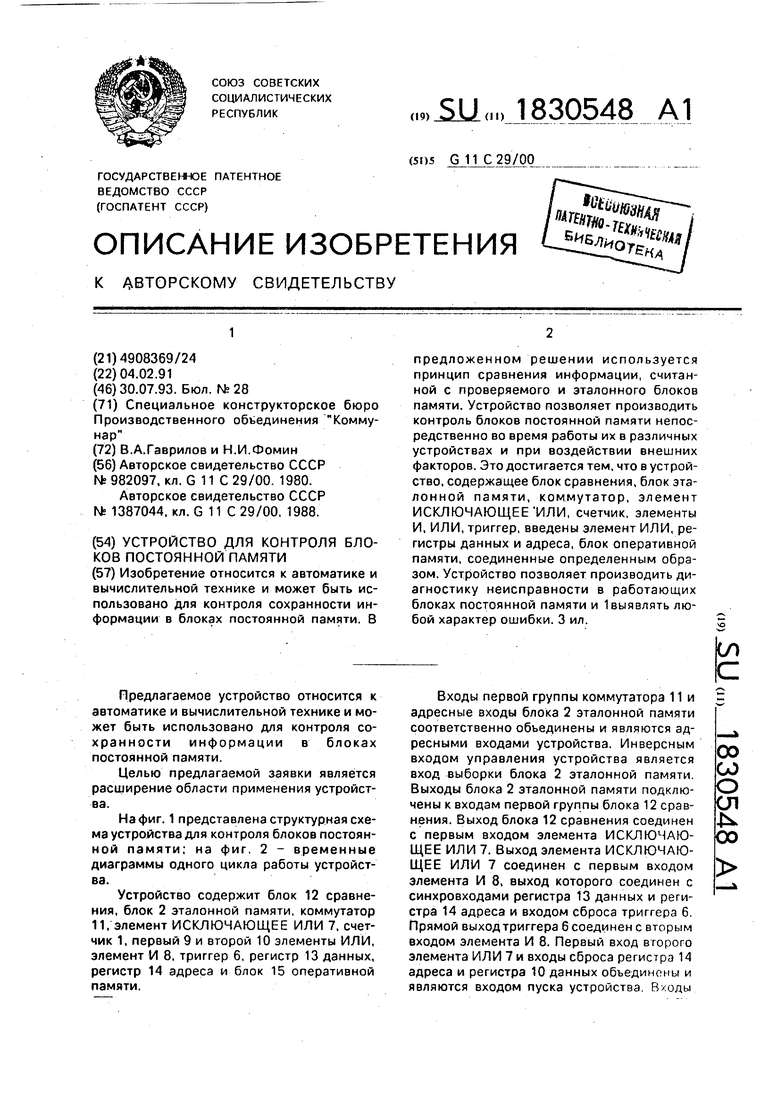

Для устранения появления на выходе блока 1 сравнения ложного сигнала несовпадения в моменты изменения состояний на выходах блоков эталонной и контролируемой памяти за счет разного времени переключения этих блоков применены следующие меры.

Блок 1 сравнения обеспечивает выдачу результата сравнения только по истечении времени, необходимого для переключения выходов блоков эталонной и контролируемой памяти. Один из вариантов реализации такого блока сравнения, обеспечивающего устранение ложного сигнала несовпадения, приведен на фиг. 3.

С выхода схемы 37 сравнения сигнал подается непосредственно на вход линии задержки 38, а также на второй вход элемента И 40, а с выхода линии задержки сигнал поступает через одновибратор 39 на первый вход элемента И 40.

Импульс несовпадения на выходе такого блока 12 сравнения, равный длительности выходного импульса одновибратора 39, может появиться только при наличии сигнала несовпадения на выходе схемы сравнения 37 по истечении времени, необходимого для переключения выходов блоков эталонной и контролируемой памяти, определяемого линией задержки 38.

Предлагаемое устройство может быть использовано и для проверки отдельно взятого ПП.ЗУ. В этом режиме на инверсный вход управления устройства необходимо подать сигнал логического О, а для опроса ячеек проверяемого ППЗУ выход счетчика соединить с входом адреса устройства (на чертеже не показано).

Применение предлагаемого устройства дает следующий технико-экономический эффект:

-расширяется область применения устройства для контроля блоков постоянной памяти, за счет применения контроля в узлах, работающих при воздействии внешних факторов;

-сокращается время поиска неисправности ППЗУ, так как диагностика узлов контроля производится без снятия ППЗУ с узла контроля;

-применение эффективной диагностики во время работы узлов контроля позволит экономить микросхемы ППЗУ, подозреваемые в сбоях и ошибочно демонтированные для перепроверки, так как вторичная установка их в аппаратуре, на место не допускается. Особенно это важно при проверке функциональных преобразователей, выполненных на ППЗУ, где диагностика без снятия микросхемы крайне затруднительна.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее блок сравнения,

блок эталонной памяти, коммутатор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик, первый элемент ИЛИ, элемент И и триггер, причем входы первой группы коммутатора и адресные входы блока эталонной памяти соответственно объединены и являются адресными входами устройства, инверсным входом управления которого является вход выборки блока эталонной памяти, выходы которого подключены к входам первой группы блока сравнения, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающее- с я тем, что, с целью расширения области применения устройства за счет диагностики

во время работы при воздействии внешних факторов и при изменении питающего напряжения, в него введены второй элемент ИЛИ, блок оперативной памяти, регистр данных и регистр адреса, причем выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом элемента И, выход которого соединен с синхровходами регистра данных и регистра адреса и входом сброса триггера, прямой выход которого соединен с вторым

входом элемента И, первый вход второго элемента ИЛИ и входы сброса регистра адреса и регистра данных объединены и являются входом пуска устройства, входы второй группы блока сравнения и информационные входы регистра данных соответственно объединены и являются информационными входами устройства, информационными выходами которого являются выходы регистра данных, адресные

входы устройства соединены с соответствующими информационными входами регистра адреса, выходы которого соединены с входами второй группы коммутатора и являются адресными выходами устройства, синхровход которого соединен с входом счетчика, выходы которого подключены к входам третьей и четвертой групп коммутатора, первый управляющий вход которого подключен к инверсному выходу триггера,

синхровход которого соединен с выходом второго элемента ИЛИ, второй вход которого, первый вход первого элемента ИЛИ и информационный вход блока оперативной памяти объединены и являются входом продолжения проверки устройства, второй вход первого элемента ИЛИ и второй управляющий вход коммутатора объединены и являются входом сброса устройства, выходы коммутатора подключены к адресным входам блока оперативной памяти, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход запись - чтение блока оперативной памяти соединен с

ункроёход

родолцсение ровер/п,

CSpac

б

17

выходом первого элемента ИЛИ. информационный вход триггера является входом логической единицы устройства.

fi

Г

О

/5

Фиг.1

ФЪг.2

J

Pll2.3

| Устройство для контроля постоянных блоков памяти | 1980 |

|

SU982097A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков постоянной памяти | 1986 |

|

SU1387044A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-07-30—Публикация

1991-02-04—Подача