Изобретение относится к цифровой вычислительной технике и может быть использовано для автоматической проверки и поиска неисправностей в блоках ЦВМ.

Известно устройство для контроля логических блоков, основанное на методе сравнения выходных сигналов контролируемого и эталонного логических блоков, входные сигналы которых формируются с помощью счетчика 1.

Недостатком этого устройства является ограниченная область применения. Оно используется для контроля сравнительно простых узлов.

Наиболее близким по техническому решению к данному изобретению является устройство для контроля логических блоков, в котором для формирования входных сигналов контролируемого и эталонного блоков используется генератор псевдослучайных кодов, что позволяет контролировать логические блоки с любым количеством входов. Это устройство содержит генератор псевдослучайных кодов, блок управления, блок информации, причем выход блока управления подключен к входу генератора псевдослучайных кодов, первая группа входов которого соединена с входами контролируемого блока 21 .

Недостатком известного устройства является то, что оно обнаруживает только те неисправности, которые приводят к изменению числа единиц в выходных последовательностях импульсов проверяемого блока.

Цель изобретения - повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство, содержащее управляющий генератор, два счетчика, триггер, одновибратор, элемент И, дешифратор, генератор псевдослучайной последовательности, блок сравнения, причем первый вход триггера является входом пуска устройства, второй вход подключен к выходу деиифратора и к первому входу блока сравнения, выход триггера подключен к входу одновибратора и первому входу элемента И, второй вход которого подключен к первому выходу одновибратора, второй выход которого подсоединен к первым входам первого и второго счетчиков, генератора псевдослучайной последовательности, :выход элемента И подключен к входу управляющего генератора, выход которого подключен к вторим,,: входам первого и второго счетчиков, генератора псевдослучайной последовательности, выход первого счетчика подключен к первому входу контролируемого блока, второй вход которого подсоединен к выходу генератора псевдослучайной последовательности, выход второго счетчика подключен к .входу дешифратора, введены N блоков вычисления остатков, каждый иэ которых содержит пять сумматоров по модулк) два, семь триггеров, причем первый вход первого сумматора по Модулю два подключен к первому входу первого триггера, выход которого подсоединен к первому входу второго сумматора по модулю два, выход которого пои лючеи к первому входу второго триггера, выход которого подключен к первому входу третьего сумматора по модулю два, выход которого подключен к первому входу третьего триггера, выход которого подсоединен к первому входу четвертого триггера, выход которого подключен к первому выходу пятого триггера, выход которого подключен к первому входу четвертого сумматора по модулю два, выход которого подсоединен к первому входу шестого триггера, выход которого подключен к первому входу пятого сумматора по модулю два, выход которого подключен к первому входу седьмого триггера,выход которого подключен к вторым входам первого, второго, третьего, четвертого,пятого сумматоров по модулю два, вторые входы первого, второго, третьего, четвертого, пятого, шестого, седьмого триггеров подключены к выходу управляющего генератора, третьи входы - к второму выходу одновибратора, выходы первого, второго, третьего, четвертого, пятого, шестого, седьмого триггеров N блоков подключены к второму входу блока сравнения.

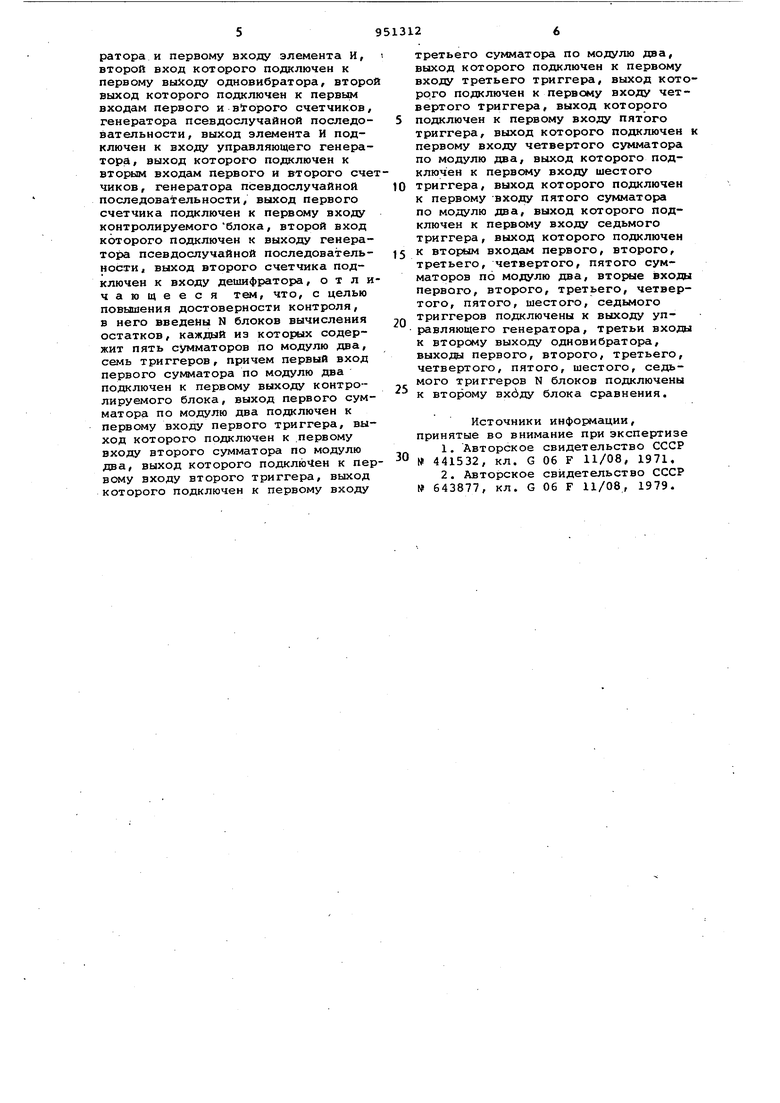

На чертеже приведена структурная схема устройства для контроля логических блоков.

Устройство содержит управляющий генератор 1, первый счетчик 2,триггер 3, одновибратор 4, элемент И 5, второй счетчик б, дешифратор 7, генератор 8 псевдослучайной последовательности, контролируемый блок 9, блок 10 сравнения, блок 11 вычисления остатка, сумматоры 12-16 по модулю два, триггеры 17-23.

Блок вычисления остатков представляет собой регистр сдвига с обратными связями с встроенными сумматорами по модулю два и состоит из D-триггеров 17-23 и сумматоров 12-16 по модулю два, блок 11 реализует деление на полином

д(х) 1 + х + х + х + х .

Устройство работает следующим ob-j разом.

По приходу сигнсша Пуск триггер 3 устанавливается в единичное состояние и запускает одновибратор

сброса 4, который генерирует импульс сброса, приводящий все элементы устройства в исходное состояние. На это время потенциал, снимаемый с его инверсного входа, запрещает прохождение сигнала Пуск на остальные элементы устройства. После окончания импульса сброса начинает работу управляющий генератор 1, управляющий работой устройства, С выхода счетчика

2 и генератора псевдослучайной последовательности 8 тестовые воздействия поступают на входы контролируемого блока 9. Последовательности импульсов с каждого выхода юонтро-

лируемого блока 9 и тактовые импульсы с выхода счетчика 2 поступают на вход блока 11 вычисления остатка от деления на полином.

Количество параллельных кодов, вырабатываемых генераторами 1 и 8 за время проверки, строго фиксировано, после выдачи последнего тестового воздействия срабатывает дешифратор 7, переводит триггер пуска в исходное состояние и разрешает индикацию вычислительных остатков , которые сравниваются с остатками, полученными в результате проверки исправного однотипного блока. Контролируемый логический блок считается исправным,

если указанные остатки совпадают. В противном случае, пользуясь диагностическими словарями и таблицами, определяют место возникновения неисправности .

Использование предлагаемого устройства позволяет контролировать логические блоки цифровой вычислительной техники, работающие под управлением последовательности синхронизирующих импульсов, повысить достоверность контроля, так как отклонение от заданной последовательности выходных импульсов вызывает изменение в значении остатка, и облегчить

поиск неисправностей в контролируемом устройстве.

Формула изобретения

55

Устройство для контроля логических блоков, содержащее управляющий генератор, .два счетчика, триггер, одновибратор, элемент И, дешифратор, генератор псевдослучайной последо60вательности, блок сравнения, причем первый вход триггера является входом пуска устройства, второй вход подключен к выходу дешифратора и к первому входу блока сравнения, выход 65 триггера подключен к входу одновибpaтора и первому входу элемента И, второй вход которого подключен к первому выходу одновибратора, второ выход которого подключен к первьгм входам первого и второго счетчиков, генератора псевдослучайной последовательности , выход элемента И подключен к входу управляющего генератора, выход которого подключен к вторым входам первого и в торого счечиков, генератора псевдослучайной последовательности, выход первого счетчика подключен к первому входу контролируемогоблока, второй вход которого подключен к выходу генератора псевдослучайной последовательности, выход второго счетчика подключен к входу дешифратора, отличающееся т&л, что, с целью повышения достоверности контроля, в него введейы N блоков вычисления остатков, каждый из которых содержит пять сумматоров по модулю два, семь триггеров, причем первый вход первого сумматора по модулю два подключен к первому выходу контролируемого блока, выход первого сумматора по модулю два подключен к первому входу первого триггера, выход которого подключен к .первому входу второго сумматора по модулю два, выход которого подключен к первому входу второго триггера, выход которого подключен к первому входу

третьего сумматора по модулю два, выход которого подключен к первому входу третьего триггера, выход которого подключен к первому входу четвертого триггера, выход которого

подключен к первому входу пятого триггера, выход которого подключен к первому входу четвертого сумматора по модулю два, выход которого подключен к первому входу шестого

триггера, выход которого подключен к первому ВХОДУ пятого (матора по модулю два, выход которого подключен к первому входу седьмого триггера, выход которого подключен

к вторым входам первого, второго, третьего, четвертого, пятого сумматоров по модулю два, вторые входы первого, второго, третьего, четвертого, пятого, шестого, седы4ого

триггеров подключены к выходу управляющего генератора, третьи входы к второму выходу одновибратора, выходы первого, второго, третьего, четвертого, пятого, шестого, седьМОго триггеров N блоков подключены к второму вхбду блока сравнения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 441532, кл. G 06 F 11/08, 1971.

2.Авторское свидетельство СССР № 643877, кл. G 06 F 11/08, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1983 |

|

SU1142837A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1251082A1 |

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1037257A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для определения области работоспособности радиоэлектронных схем | 1986 |

|

SU1386947A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

Авторы

Даты

1982-08-15—Публикация

1980-11-05—Подача