Изобретение относится к цифровой вычислительной технике и может быть использовано для автоматической проверки и поиска неисправностей в бло ках ЦВМ.

Цель изобретения - повьшение достоверности контроля.

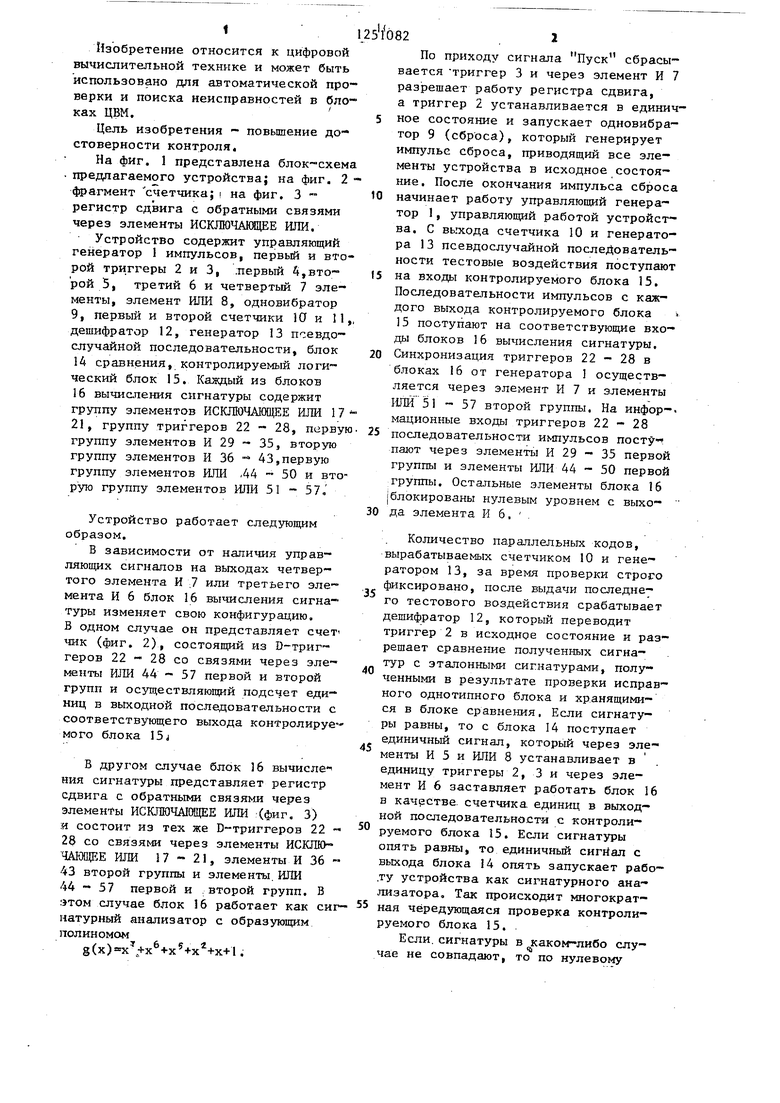

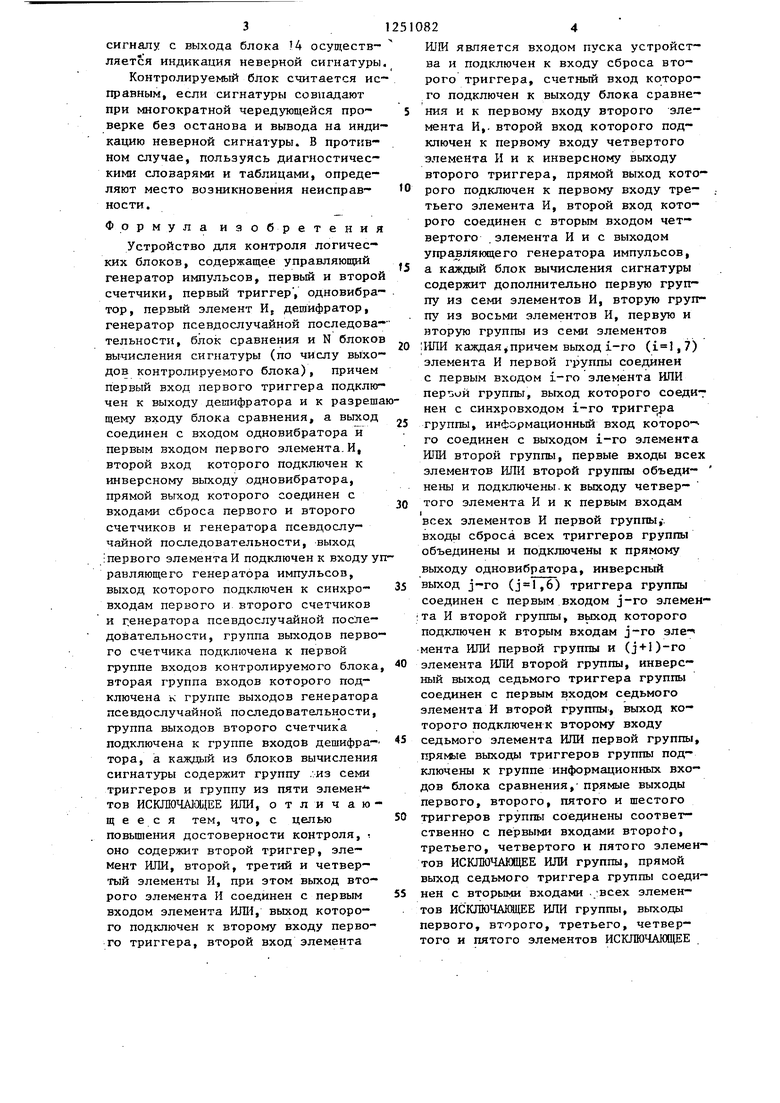

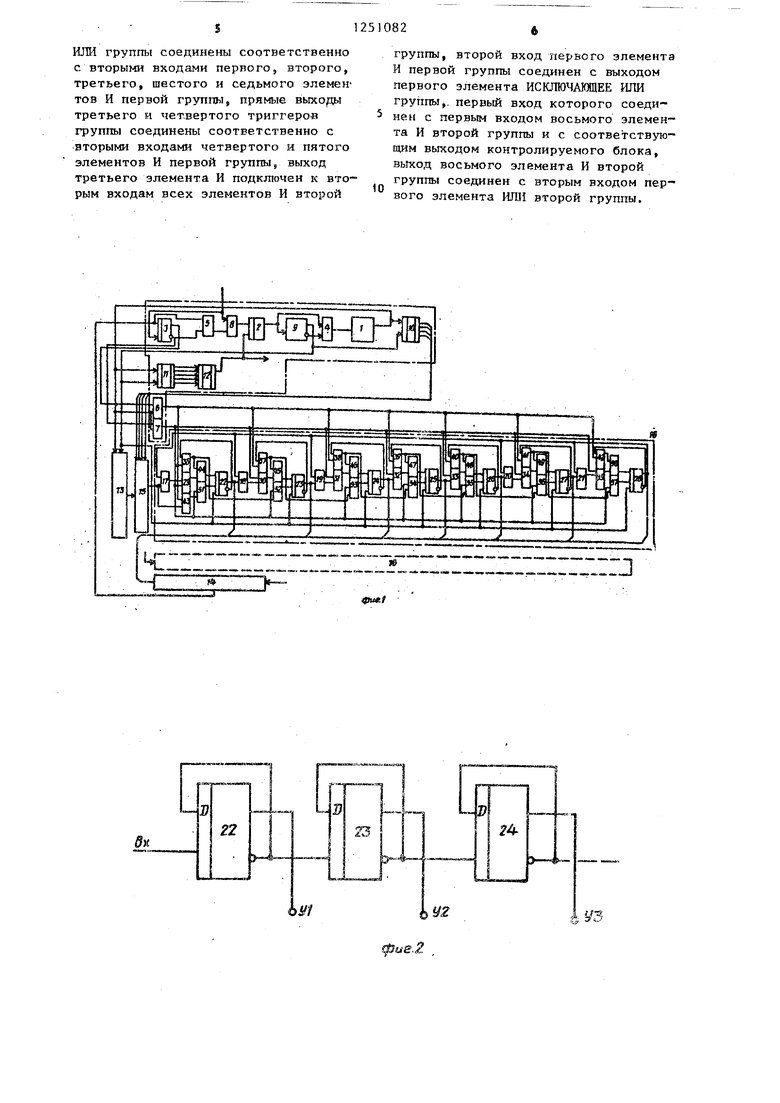

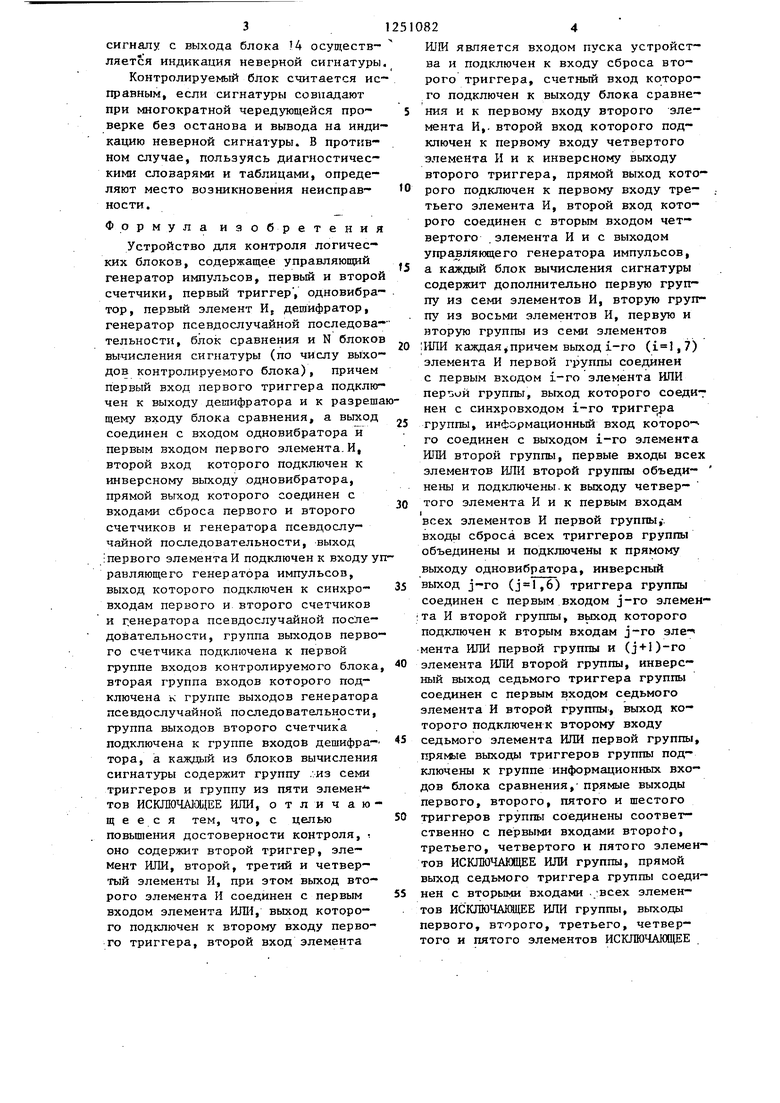

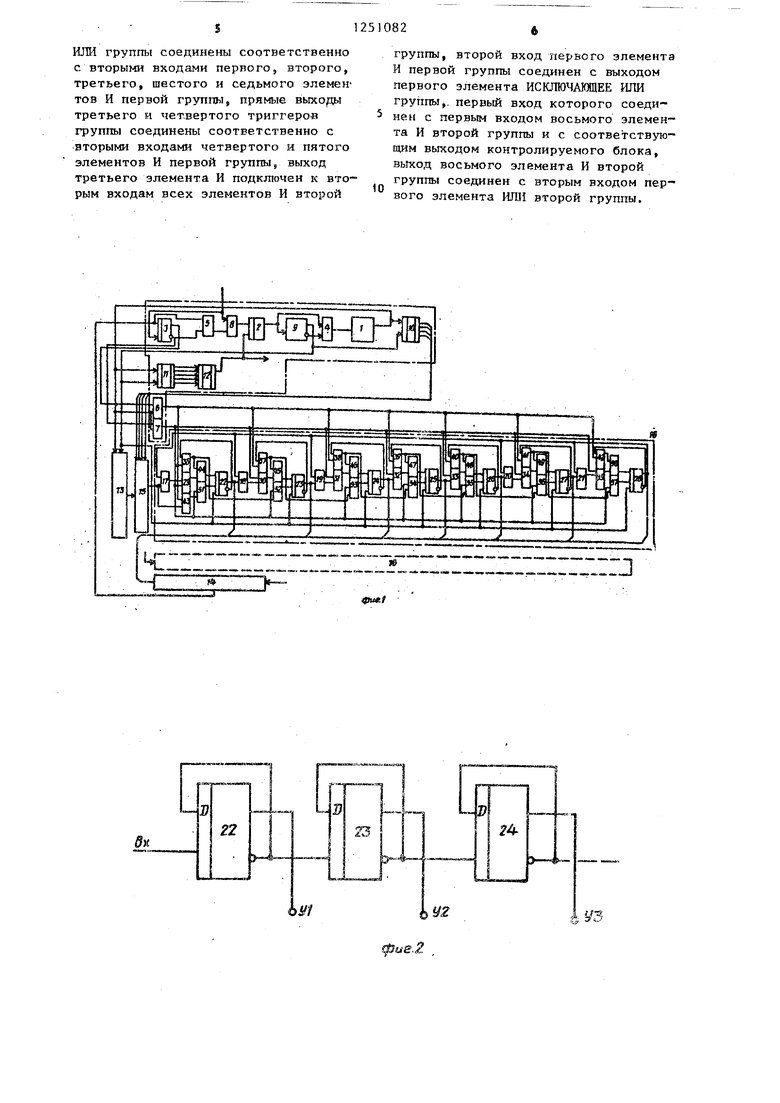

На фиг. 1 представлена блок-схема . предлагаемого устройства; на фиг. 2 - фрагмент счетчика; на фиг. 3 - регистр сдвига с обратными связями через элементы ИСКЛЮЧАНЩЕЕ ИЛИ.

Устройство содержит управляющий генератор 1 импульсов, первый и второй триггеры 2 и 3, .первый ,вто рой 5, третий 6 и четвертый 7 элементы, элемент ИЛИ 8, одновибратор 9, первый и второй счетчики Ш и 11,, дешифратор 12, генератор 13 псевдослучайной последовательности, блок 14 сравнения, контролируемый логический блок 15. Каждый из блоков 16 вычисления сигнатуры содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 17 21, группу триггеров 22 - 28, первую, группу элементов И 29 35, вторую группу элементов И 36 43,первую группу элементов ИЛИ .44 - 50 и вторую группу элементов ИЛИ 51 - 57. .

Устройство работает следующим образом.

В зависимости от наличия управляющих сигналов на выходах четвертого элемента И ,7 или третьего элемента И 6 блок 16 вычисления сигнатуры изменяет свою конфигурацию. В одном случае он представляет счеТ чик (фиг. 2), состоящий из В-триг геров 22 - 28 со связями через элементы ШШ 44 - 57 первой и второй групп и осуществляющий подсчет единиц в выходной последовательности с соответствующего выхода контролируемого блока 15J

В другом случае блок 16 вычисле ния сигнатуры представляет регистр сдвига с обратньши связями через элементы ИСКЛЮЧАКЩЕЕ ИЛИ (фиг. 3) и состоит из тех же D-триггеров 22 28 со связями через элементы ИСКЛЮ- ШСЩЕЕ ИЛИ 17 - 21, элементы И 36 -

43второй группы и элементы. ИЛИ

44- 57 первой и второй групп. В

10

15

20

25

30

35

40

45

50

По приходу сигнала Пуск сбрасы вается -триггер 3 и через элемент И разрешает работу регистра сдвига, а триггер 2 устанавливается в едини ное состояние и запускает одновибра тор 9 (сброса), который генерирует импульс сброса, приводящий все элементы устройства в исходное состояние. После окончания импульса сброс начинает работу управляющий генератор 1, управляющий работой устройст ва. С вьжода счетчика 10 и генерато ра 13 псевдослучайной последователь ности тестовые воздействия поступаю на входы контролируемого блока 15. Последовательности импульсов с каждого выхода контролируемого блока 15 поступают на соответствующие вхо ды блоков 16 вычисления сигнатуры. Синхронизация триггеров 22 - 28 в блоках 16 от генератора 1 осуществляется через элемент И 7 и элементы ИЛИ 51-57 второй группы. На инфор мационные входы триггеров 22 - 28 последовательности импульсов пост-}- пают через элементы И 29 - 35 перво группы и элементы ИЛИ 44 - 50 перво группы. Остальные элементы блока 16 jблокированы нулевым уровнем с выхода элемента И 6. .

Количество параллельных кодов, вырабатываемых счетчиком 10 и генератором 13, за время проверки строго фиксировано, после выдачи последнего тестового воздействия срабатывает дешифратор 12, который переводит триггер 2 в исходное состояние и раз решает сравнение полученных сигнатур с эталонными сигнатурами, полученными в результате проверки исправ ного однотипного блока и хранящимися в блоке сравнения, Если сигнатуры равны, то с блока 14 поступает единичный сигнал, который через элементы И 5 и ИЛИ 8 устанавливает в единицу триггеры 2, 3 и через элемент И 6 заставляет работать блок 16 в качестве счетчика единиц в выходной последовательности с контролируемого блока 15. Если сигнатуры опять равны, то единичный сигйал с выхода блока 14 опять запускает рабо ту устройства как сигнатурного анализатора. Так происходит многократитом случае блок 16 работает как сиг- 5 нал чередующаяся проверка контролинатурный анализатор с образующимруемого блока 15.

полиномомЕсли.сигнатуры в каком-либо слуg(x).чае не совпадают, то по нулевому

5

0

5

0

5

0

5

По приходу сигнала Пуск сбрасывается -триггер 3 и через элемент И 7 разрешает работу регистра сдвига, а триггер 2 устанавливается в единичное состояние и запускает одновибратор 9 (сброса), который генерирует импульс сброса, приводящий все элементы устройства в исходное состояние. После окончания импульса сброса начинает работу управляющий генератор 1, управляющий работой устройства. С вьжода счетчика 10 и генератора 13 псевдослучайной последовательности тестовые воздействия поступают на входы контролируемого блока 15. Последовательности импульсов с каждого выхода контролируемого блока 15 поступают на соответствующие входы блоков 16 вычисления сигнатуры. Синхронизация триггеров 22 - 28 в блоках 16 от генератора 1 осуществляется через элемент И 7 и элементы ИЛИ 51-57 второй группы. На инфор-- мационные входы триггеров 22 - 28 последовательности импульсов пост-}- пают через элементы И 29 - 35 первой группы и элементы ИЛИ 44 - 50 первой группы. Остальные элементы блока 16 jблокированы нулевым уровнем с выхо да элемента И 6. .

Количество параллельных кодов, вырабатываемых счетчиком 10 и генератором 13, за время проверки строго фиксировано, после выдачи последнего тестового воздействия срабатывает дешифратор 12, который переводит триггер 2 в исходное состояние и разрешает сравнение полученных сигнатур с эталонными сигнатурами, полученными в результате проверки исправного однотипного блока и хранящимися в блоке сравнения, Если сигнатуры равны, то с блока 14 поступает единичный сигнал, который через элементы И 5 и ИЛИ 8 устанавливает в единицу триггеры 2, 3 и через элемент И 6 заставляет работать блок 16 в качестве счетчика единиц в выходной последовательности с контролируемого блока 15. Если сигнатуры опять равны, то единичный сигйал с выхода блока 14 опять запускает работу устройства как сигнатурного анализатора. Так происходит многократ

сигналу с выхода блока 4 осуществ- ллется индикация неверной сигнатуры Контролируемый блок считается исправным, если сигнатуры совпадают при многократной чередующейся проверке без останова и вывода на индикацию неверной сигнатуры. В противном случае, пользуясь диагностическими словарями и таблицами, определяют место возникновения неисправности.

Формула изобретения Устройство для контроля логических блоков, содержащее управляющий генератор импульсов, первый и второй счетчики, первый триггер , одновибра- тор, первый элемент И, дешифратор, генератор псевдослучайной последовательности, блок сравнения и N блоков вычисления сигнатуры (по числу выходов контролируемого блока), причем первый вход, первого триггера подключен к выходу дешифратора и к разрешащему входу блока сравнения, а выход соединен с входом одновибратора и первым входом первого элемента.И, второй вход которого подключен к инверсному выходу одновибратора, прямой выход которого соединен с входами сброса первого и второго счетчиков и генератора псевдослучайной последовательности, выход : первого элементам подключен к входу управляющего генератора импульсов, выход которого подключен к синхро- входам первого и второго счетчиков и г.енератора псевдослучайной последовательности, группа выходов первого счетчика подключена к первой группе входов контролируемого блока, вторая группа входов которого подключена к группе выходов генератора псевдослучайной последовательности, группа выходов второго счетчика подключена к группе входов дешифратора, а каждый из блоков вычисления сигнатуры содержит группу ..из семи триггеров и группу из пяти элемен- тов ИСКЛЮЧА ЭДЕЕ ИЛИ, отличаю

щ е е с я тем, что, с целью повьшшния достоверности контроля, . оно содержит второй триггер, элемент ИЛИ, второй, третий и четвертый элементы И, при этом выход второго элемента И соединен с первым входом элемента ИЛИ, выход которого подключен к второму входу первого триггера, второй вход элемента

10

t5

20

j. 0

30

35

45

0

5

ИЛИ является входом пуска устройства и подключен к входу сброса второго триггера, счетный вход которого подключен к выходу блока сравнения и к первому входу второго элемента И,, второй вход которого подключен к первому входу четвертого элемента И и к инверсному выходу второго триггера, прямой выход которого подключен к первому входу третьего элемента И, второй вход которого соединен с вторым входом четвертого .элемента И и с выходом упра вляющего генератора импульсов, а каждый блок вычисления сигнатуры содержит дополнительно первую группу из семи элементов И, вторую группу из восьми элементов И, первую и вторую группы из семи элементов :1ШИ каждая причем выход i-ro (,7) элемента И первой группы соединен с первым входом i-ro элемента ИЛИ первой группы, выход которого соедит нен с синхровходом i-ro триггедза группы, информационный вход которо- го соединен с выходом i-го элемента ИЛИ второй группы, первые входы всех элементов ИЛИ второй группы объеди- нены и подключены.к выходу четвертого элемента И и к первым входам всех элементов И первой группы,-. входы сброса всех триггеров группы объединены и подключены к прямому выходу одновибратора, инверсный выход j-ro (,6) триггера группы соединен с первым входом j-ro элемен- ;та И второй группы, выход которого подключен к вторым входам j-ro эле мента Р1ПИ первой группы и (j + l)-ro элемента ШТИ второй группы, инверсный выход седьмого триггера группы соединен с первым входом седьмого элемента И второй группы, выход которого подключенк второму входу седьмого элемента ИЛИ первой группы, прямые выходы триггеров группы подключены к группе информационных входов блока сравнения, прямые выходы первого, второго, пятого и шестого триггеров группы соединены соответственно с первыми входами второго, третьего, четвертого и пятого элементов ИСКЛЮЧАКЩЕЕ ИЛИ группы, прямой выход седьмого триггера группы соединен с вторыми входами . Всех элементов ИСКЛЮЧАЩЕЕ ИЛИ группы, выходы первого, второго, третьего, четвертого и пятого элементов ИСКЛЮЧАКЩЕЕ

ИЛИ группы соединены соответственно с вторыми входами первого, второго, третьего, шестого и седьмого элементов И первой групп, прямые выхо;д.1 третьего и четвертого триггеров группы соединены соответственно с вторыми входами четвертого и пятого элементов И первой группы, выход третьего элемента И подключен к вторым входам всех элементов И второй

группы, второй вход первого элемента И первой группы соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группыJ. первый вход которого соеди ней с первым входом восьмого элемента И второй группы и с соответствую™ щим выходом контролируемого блока, выход восьмого элемента И второй группы соединен с вторым входом первого элемента ИЛИ второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1980 |

|

SU951312A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1142837A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1319035A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для автоматической проверки и поиска неисправностей в блоках ЦВМ. Целью изобретения является повышение достоверности контроля. Устройство содержит управляющий генератор, два счетчика, два триггера, одновибратор, четыре элемента И, элемент ИЛИ,, дешифратор, генератор псевдослучайной последова.тельности, блок сравнения, а также N блоков вычисления сигнатуры по числу выходов контролируемого блока, каждый из которых содержит группу из семи триггеров, группу из пяти элементов ИСКЛЮЧАЮЩЕЕ {ШИ, первую группу из семи элементов И, вт Ьрую группу из восьми элементов И, первую и вторую группы из семи элементов ИЛИ каждая. В зависимости от внутренних управляющих сигналов блоки вычисления сигнатур изменяют свою конфигурацию: в одном «„лучае они представляют собой сигнатурные анализаторы, в другом - счетчики единиц в контролируемой последовательности. Устройство обеспечивает многократную чередующуюся проверку контролируемого блока при свертке - выходной его информации последовательно методом вычисления сигнатуры и методом счета единиц, что повышает вероятность обнаружения ошибок.3 ил. о (Л

фия

, I/S

| Устройство для контроля логических блоков | 1976 |

|

SU643877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU951312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-02—Подача