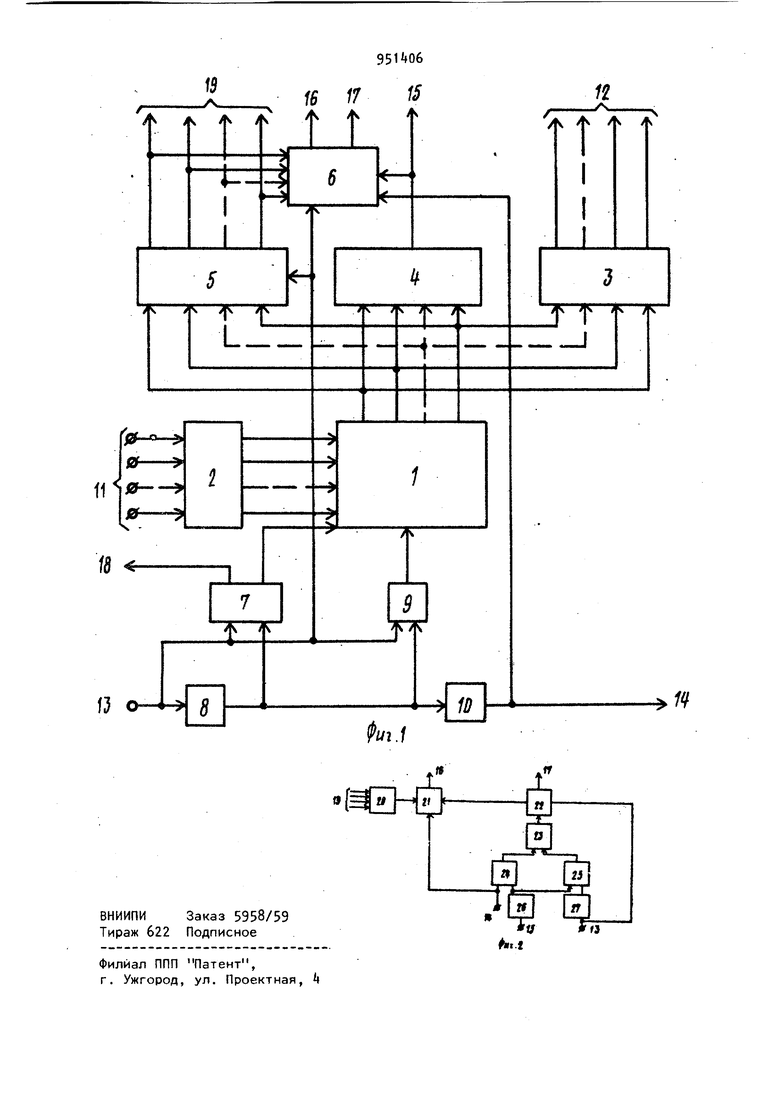

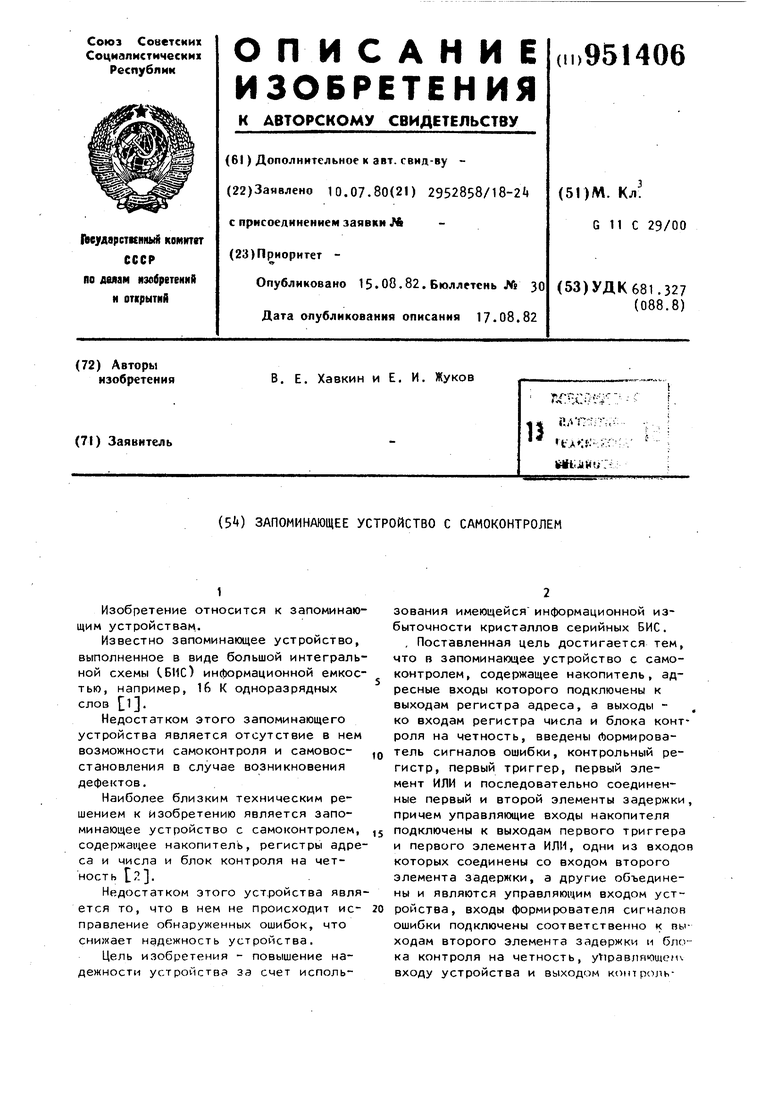

Изобретение относится к запоминающим устройствам.. Известно запоминающее устройство, выполненное в виде большой интеграль ной схемы С,БИС) информационной емкостью, например, 16 К одноразрядных слов 1. Недостатком этого запоминающего устройства является отсутствие в нем возможности самоконтроля и самовосстановления D случае возникновения дефектов. Наиболее близким техническим решением к изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, регистры адре са и числа и блок контроля на четность л. Недостатком этого устройства явля ется то, что в нем не происходит исправление обнаруженных ошибок, что снижает надежность устройства. Цель изобретения - повышение надежности устройства за счет использования имеющейся информационной избыточности кристаллов серийных БИС. , Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель, адресные входы которого подключены к выходам регистра адреса, а выходы - , ко входам регистра числа и блока контроля на четность, введены Лормирователь сигналов ошибки, контрольный регистр, первый триггер, первый элемент ИЛИ и последовательно соединенные первый и второй элементы задержки, причем управляющие входы накопителя подключены к выходам первого триггера и первого элемента ИЛИ, одни из входов которых соединены со входом второго элемента задержки, а другие объединены и являются управляющим входом устройства, входы формирователя сигналов ошибки подключены соответственно к выходам второго элемента задержки и блока контроля на четность, управляющем входу устройства и выходом контрольного регистра, информационные входы которого соединены с выходами накопителя, а управляющий вход подключен к управляЮ14ему входу устройства, а также тем, что формирователь сигналов ошибки содержит элементы ИЕ-ИЛИ, И, НЕ-И, НЕ, второй элемент ИЛИ, второй триггер и третий элемент задержки, причем выход элемента НЕ-ИЛИ подключен к одному из входов элемента И, другие входы которого соединены с одним из выходов триггера и первым входом первого элемента НЕ-И, второй вход которого подключен к выходу элемента НЕ и одному из входов второго элемента НЕ-И, другой вход которого соединен с выходом третьего элементазадержки, выходы элементов НЕ-И подключены ко входам второго элемента ИЛ выход которого соединен с одним из входов второго триггера, другой вход которого соединен со входом третьего элемента задержки, входы элементов НЕ-ИЛИ, элемента НЕ и третьего элемента задержки и первый вход nepao го элемента НЕ-И являются входами фор мирователя, выходами которого являются выход элемента И и другой выход второго триггера. На фиг. 1 изображена структурная схема запоминающего устройства с само контролем; на фиг. 2 - структурная схема формирователя сигнала ошибки. Устройство (см. фиг. 1) содержит накопитель 1 с информационной емкостью не менее чем в два раза превышающей требуемую для решения задач системы, регистр 2 адреса, регистр 3 числа, блок k контроля на четность, контрольный регистр 5, представляющий регистр последовательного сравнения, формирователь 6 сигналов ошибки, первый триггер 7, первый элемент задержки, первый элемент ИЛИ 9, второй элемент 10 задержки. Устройство имеет адресные входы 1 информационные выходы 12, управляющий вход 13, выход И сигналов Готов ность, выход 15 сигналов Разрешение считывания, выход 16 сигналов Кратная ошибка, выход 17 сигналов Одиночная ошибка, выход 18 сигналов дополнительного разряда кода адреса, выходы 19 сигналов Неисправные разряды. Формирователь 6 сигналов ошибки (см. фиг. 2) содержит элемент НЕ-ИЛИ элемент И 21, второй триггер 22, второй элемент ИЛИ 23, первый 2 и второй 25 элементы НЕ-И, элемент НЕ 26 и третий элемент 27 задержки. Устройство работает следующим образом. В накопитель 1, состоящий из БИС оперативной или постоянной памяти, количество адресов в каждой из которых, по крайней мере, в два раза превышает необходимую для работы вычислительного устройства, тем или другим способом записана информация (см. фиг. 1), причем в каждой паре адресов, отличающихся, например, старшим разрядом кода адреса БИС, информация одинакова. При считывании информации на входы запоминающего устройства поступает от арифметического устройства (на фиг. 1 не показано) код адреса по входам 11, который запоминается в регистре 2 и запрос по входу 13, который устанавливает блоки 5, 6 и 7 в исходное состояние и через элемент ИЛИ 9 подается на входы выбора кристалла БИС. При этом происходит считывание ранее записанной информации по адресу, соответствующему поданному на входы БИС коду адреса от регистра 2 и триггера 7; считанная информация записыва ется в регистр 3 и вместе с информацией с контрольного разряда поступает на входы блока . Если свертка по модулю два совпала с информацией, считанной из контрольного разряда, с выхода 15 в арифметическое устройство передается сигнал Разрешение считывания. В противном случае си|- нал Разрешение считывания не вырабатывается. Как в том, так и в другом случае производится повторное считывание информации из аналогичного адреса другой половины каждой БИС, для чего по истечении времени, опреде ляемого задержкой запроса в элементе 8 задержки, формируется повторный запрос, поступающий на соответствующий вход каждой БИС через элемент ИЛИ 9. Этот же сигнал перебрасывает триггер 7, в результате чего на соответствующем входе каждой БИС устанавливается код адреса, определяющий обращение к одноименным ячейкам другой половины БИС, в которых записана та же, что и при предыдущем обращении, исходная информация. Считанная информация также контролируется по модулю два. В зависимости от результатов контроля при первом и втором считыоа-НИИ возможны следующие вари ант ь1. 5 Одиночная 1или любая некратная) ошибка зафиксирована только при первом считывании: тогда с выхода 17 в арифметическое устройство и на пульт оператора (на фиг. 1 не показан) поступает сигнал одиночной ошибки и с выхода 18 - адрес половины массива адресов. При повторном считывании на выходе 15 появляется сигнал Разрешение считывания. Одиночная ошибка зафиксирована только при повторном считывании. На выходе 17 появляется сигнал одиночно ошибки, на выходе 18 - адрес другой половины массива адресов. В этом слу чае считанная в первом такте информация уже используется арифметически устройством, а полученная с выходов и 18 информация об ошибке может быть использована оператором или автомато для контроля за состоянием резерва. Одиночная ошибка обнаружена при первом и втором считывании. Эта ситу ация соответствует отказу основного и резервного адресов накопителя 1, и вопрос о дальнейшем его использова нии решается в зависимости от наличия в системе других средств анализа икоррекции обнаруженной неисправ ности. При первом и втором считывании контроль по модулю два показал отсутствие одиночных ( некратных/ошибок. В этом случае арифметическое устройство использует информацию, полученную при первом считывании, н в запоминающем устройстве производи ся контроль на отсутствие кратных ошибок следующим образом. Информация при первом и втором считывании поступает на регистр 5, каждый разряд которого представляет собой триггер со счетным входом, устанавливаемый в исходное состояние сигна ЛОМ Запрос, поступающим на вход 1 Если на триггер 7 подается два последовательных сигнала Логический О, то состояние триггера 7 сохраняется, если два сигнала Логическая 1, то состояние триггера 7 изменяется дважды и после второго счи тывания соответствует исходному. По этому на выходах 19 устанавливается сигнал Логическая 1, что соответс вует отсутствию неисправности во вс разрядах. Если в каких-либо разряда информация при двух последовательных считываниях различается, то на выходах 19 этих разрядов устанавлив 6 ется сигнал, инверсный по отношению к исправным разрядам. После второго считывания, момент окончания которого определяется элементом 10 задержки ,на вход формирователя 6 поступает разрешение формирования сигнала ошибки . При отсутствии ошибок на выходах 16 и 17 устанавливается (сохраняется) О, свидетельствующий об отсутствии неисправности. Если в любой половине накопителя имеется одиночная (некратная ошибка, то на выходе 17 устанавливается сигнал одиночной ошибки (1, а на выходе 16 - О, так как формирователь 6 формирует сигнал кратной ошибки только при несравнении сигналов считывания в разрядах при условии отсутствия ошибки при контроле по модулю два. При появлении.кратной ошибки, характеризуемой появлением сигнала несравнения в разрядах при отсутствии ошибки при контроле по модулю два на выходе 17 сохраняется О, а на выходе .16 появляется 1. С выходов 19 в арифметическое устройство и н-а пульт оператора выводится информация о неисправных разрядах для оценки состояния накопителя 1 и принятия мер по корректировке кратных ошибок, если в системе предусмотрены необходимые для этого аппаратные или программные средства. Разрешение на последующие обращения к памяти пс окончании второго считывания и операции контроля выдается по выходу 1. Как это следует из рассмотренного принципа действия, запоминающее устройство требует для выполнения операции полного контроля двух тактов обращения. В подавляющем большинстве случаев системного использования памяти это не приводит к ощутимому снижению быстродействия системы, так как полная задержка на один такт возникает только в случае неиспрй вности в первой половине накопителя и при непрерывных обращениях к памяти с максимальной частотой. Последнее является маловероятным, так как после такта считывания из памяти происходит обработка считанного сигнала в арифмети-ческом устройстве. Кроме того при реализации описанного устройства могут быть использованы БИС ЗУ с быстродействием, препышающим требуемое для системы. Устройство позволяет обнаруживать и исправлять все некратные ошибки Р

любой половине накопителя и обнаруживать все кратные ошибки и некратные ошибки, возникающие в одноименных адресах обеих половин накопителя.

Формула изобретения

1. Запоминающее устройство с самоконтролем, содержащее накопитель, ресные входы которого подключены к выходам регистра адреса, а выходы - к входам регистра числа и блока контроля на четность, отличающеес я тем, что, с целью повышения на- 5 дежности устройства, содержит формирователь сигналов ошибки, контрольный регистр, первый триггер, первый элемент ИЛИ и последовательно соединенные первый и второй элементы зaдepжки 20 причем управлякЗщие входы накопителя подключены к выходам первого триггера и первого элемента ИЛИ, одни из входов которых соединены с входом второго элемента задержки, а другие объ- 25 единены и являются управляющим входом устройства, входы формирователя сигналов ошибки подключены соответственно к выходам второго элемента задержки и блока контроля на четность, управля-зо ющему входу устройства и выходам контрольного регистра, информационные ВХОД111 которого соединены с выходами накопителя, а управляющий вход подключен к управляющему входу устройст- j ва.

2. Устройство по п. 1, о т л и чающееся тем, что формирователь сигналов ошибки содержит элементы НЕ-ИЛИ, И, НЕ-И, НЕ, второй элемент ИЛИ, второй триггер и третий задержки, причем выход элемента НЕ-ИЛИ подключен к одному из входов элемента И, другие входы которого соединены с одним из выходов триггера и первым входом первого элемента НЕ-И, второй вход которого подключен к выходу элемента НЕ и одному из входов второго элемента НЕ-И, другой вход которого соединен с выходом третьего элемента задержки, выходы элементов НЕ-И подключены к входам второго элемента ИЛИ, выход которого соединен с одним из входов второго триггера, другой вход которого соединен с входом третьего элемента задержки, входы элементов НЕ-ИЛИ, элемента НЕ и третьего элемента задержки и первый вход первого элемента НЕ-И являются входами формирователя, выходами которого являются выход элемента И и другой выход второго триггера.

Источники информации, принятые во внимание при экспертизе

1. Электроника, русский перевод, 1978, N 19, с. 112.

2. Путинцев Н.Д. Аппаратный контроль управляющих цифровь1х вычислительных машин, М., Советское радио, 1966, с. 276 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1100638A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

Авторы

Даты

1982-08-15—Публикация

1980-07-10—Подача