Изобретение относится к запоминающим устройствам, в которых для повышения надежности используется мажоритарное резервирование на уровне микросхем памяти.

Известно запоминающее устройство с самоконтролем, содержащее накопитель, регистр адреса, регистр числа, блок контроля на четность, формирователь сигналов ошибки, контрольный регистр, первый триггер, первый элемент ИЛИ, первый и второй элементы задержки, причем формирователь ошибки содержит элементы НЕ-ИЛИ, И, НЕ-И, НЕ, второй элемент ИЛИ, второй триггер, третий элемент задержки [1].

Недостатком этого устройства является низкая надежность.

Известно также запоминающее устройство с самоконтролем, содержащее регистр адреса, накопитель, контрольный регистр, формирователь ошибки, элемент ИЛИ, первый, второй, третий и четвертый элементы задержки, счетчик старших разрядов кода адреса, элемент И, причем формирователь сигнала ошибки содержит группу инверторов, элемент ИЛИ, первый и второй элементы И, первый и второй элементы задержки, инвертор и триггер [2].

Недостатком этого устройства является низкая информационная емкость накопителя.

Наиболее близким по технической сущности решением является запоминающее устройство с резервированием, содержащее накопитель, контрольный регистр, формирователь сигнала ошибки, сумматор, первый и второй элементы ИЛИ, элемент И, пять элементов задержки, умножитель на три, счетчик-регистр, вход обращения, адресные входы, информационные выходы, выходы неисправных разрядов, выход разрешения считывания и выход ошибки.

Технические средства прототипа ориентированы на накопитель, состоящий из БИС оперативной или постоянной памяти, количество адресов в котором в три раза превышает необходимое для работы вычислительного устройства, причем в каждых трех соседних адресах, начиная с адреса, кратного трем, информация одинакова.

Однако при этом затруднено использование мажоритарного резервирования на уровне микросхем памяти, так как вся избыточная информация оказывается записанной в одной области одной микросхемы памяти и при отказе микросхемы или ее области приводит к отказу всего устройства. Следовательно прототип имеет низкую надежность и ограничение возможности мажоритарного резервирования на уровне микросхем памяти.

Целью изобретения является повышение надежности и расширение области применения устройства.

Цель достигается тем, что в запоминающее устройство с резервиpованием, содержащее накопитель, контрольный регистр, формирователь сигнала ошибки, сумматор, первый и второй элементы ИЛИ, элемент И, с первого по пятый элементы задержки, причем выходы накопителя соединены со счетными входами контрольного регистра, выходы первой группы которого являются информационными выходами устройства, выходами неисправных разрядов которого являются выходы второй группы контрольного регистра, которые соединены с соответствующими информационными входами формирователя сигнала ошибки, первый и второй выходы которого являются соответственно выходом разрешения считывания и выходом ошибки устройства, первый и второй синхровходы формирователя сигнала ошибки соединены соответственно с выходами второго элемента задержки и элемента И, первый и второй входы которого подключены соответственно к второму выходу формирователя сигнала ошибки и к выходу четвертого элемента задержки, вход которого соединен с выходом первого элемента задержки, входом второго элемента задержки и с первым входом первого элемента ИЛИ, второй вход и выход которого подключены соответственно к выходу элемента И и первому входу второго элемента ИЛИ, второй вход которого соединен с входом первого элемента задержки и выходом пятого элемента задержки, вход которого, вход сброса контрольного регистра и вход сброса формирователя сигнала ошибки объединены и являются входом обращения устройства, выход второго элемента ИЛИ соединен с входом третьего элемента задержки, выход которого подключен к входу выборки накопителя, введены первый, второй и третий регистры, с первого по четвертый блоки элементов И, первый и второй блоки элементов ИЛИ, причем выходы первого регистра подключены к соответствующим адресным входам накопителя, информационные входы второго и третьего регистров являются соответственно адресными входами первой и второй групп устройства, выходы второго и третьего регистров подключены к входам групп соответственно первого и второго блоков элементов И, выходы которых соединены соответственно с входами первой и второй групп первого блока элементов ИЛИ, выходы которого подключены к соответствующим входам первой группы сумматора, входы второй группы которого и входы группы четвертого блока элементов И соответственно объединены и являются адресными входами третьей группы устройства, входы первого и четвертого блоков элементов И объединены и подключены к выходу пятого элемента задержки, к входу которого подключены вход установки нуля первого регистра и вход установки нуля сумматора, выходы которого подключены к соответствующим входам группы третьего блока элементов И, вход которого соединен с выходом первого элемента ИЛИ, выходы третьего и четвертого блоков элементов И соединены соответственно с входами первой и второй групп второго блока элементов ИЛИ, выходы которого подключены к соответствующим информационным входам первого регистра.

Сущность изобретения заключается в повышении надежности и расширении области применения устройства путем введения новой дисциплины обращения к запоминающему устройству.

Суть новой дисциплины состоит:

а) в предварительной записи в любые три области накопителя одинаковой информации и записи во второй и третий регистры смещений начальных адресов второй и третьей областей памяти, причем в качестве первой области памяти может быть использована любая из трех областей, хранящих одинаковую информацию.

б) в последовательном считывании и сравнении считанной информации из первой и второй областей памяти, используя для формирования адреса второго операнда смещения, хранящееся во втором регистре, причем смещение может быть и отрицательной величиной;

в) в считывании при несовпадении первого и второго операндов, третьего операнда из третьей области памяти, используя смещение, хранящееся в третьем регистре, и которое также может быть отрицательной величиной.

Введение первого регистра, второго блока элементов ИЛИ, третьего и четвертого блоков элементов И и соответствующих им связей обеспечивает формирование на адресном входе накопителя адреса операнд в первой, второй или третьей области памяти.

Введение второго и третьего регистров, первого и второго блоков элементов И, первого блока элементов ИЛИ и соответствующих им связей обеспечивает прием, хранение и выдачу кодов смещения начальных адресов второй и третьей областей памяти накопителя соответственно относительно начального адреса первой области памяти.

Введение новых связей сумматора обеспечивает формирование на его выходе номера ячейки во второй или третьей области памяти накопителя, в которых хранится информация, одинаковая с информацией в ячейке первой области памяти, к которой производится обращение по первой группе адресных входов.

Введение второй и третьей групп адресных входов обеспечивает запись соответственно во второй и третий регистры начальных адресов второй и третьей областей памяти.

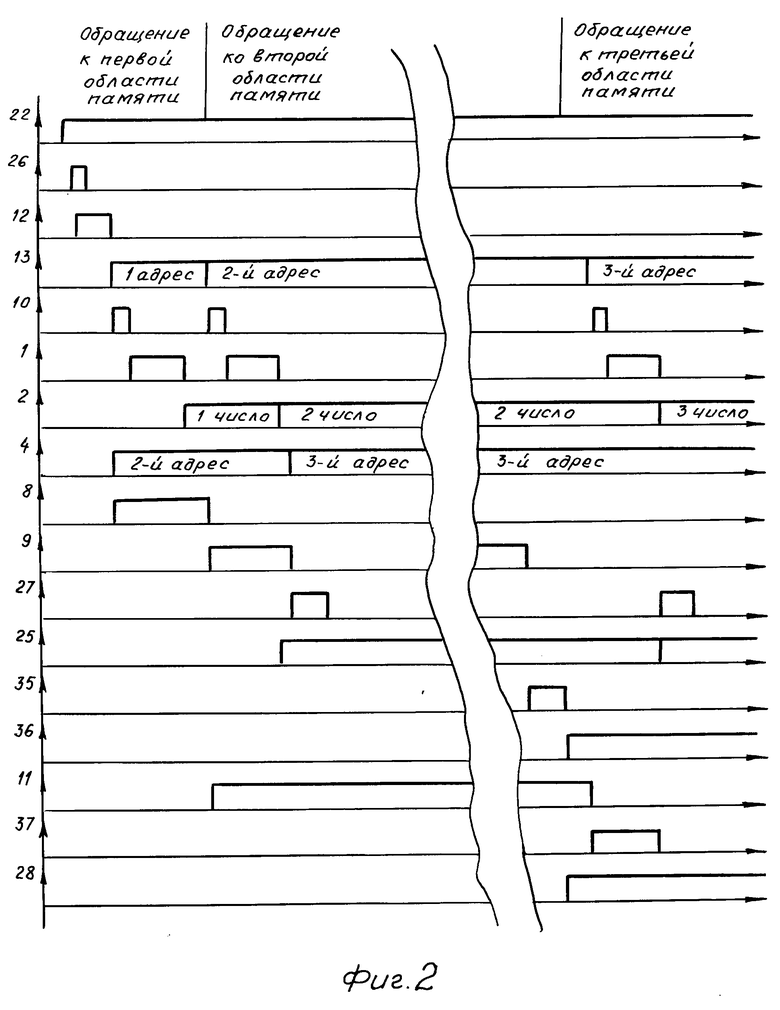

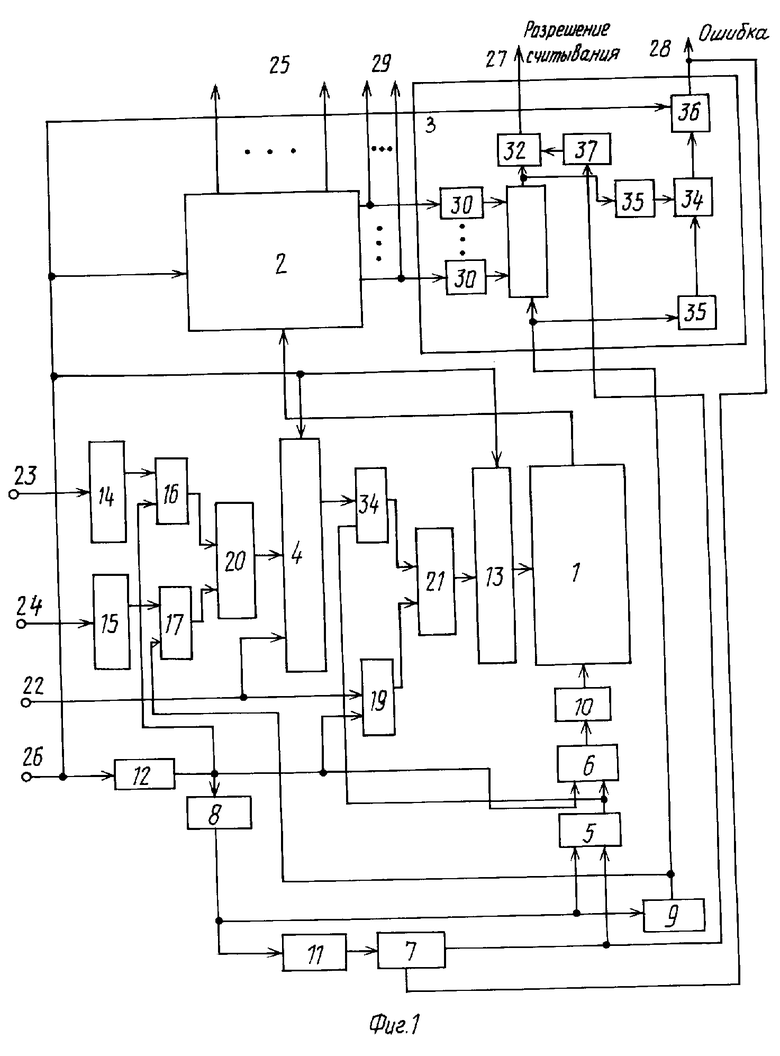

На фиг.1 изображена функциональная схема запоминающего устройства с резервированием; на фиг.2 - временные диаграммы работы устройства.

Устройство содержит накопитель 1, контрольный регистр 2, формирователь сигнала ошибки 3, сумматор 4, первый 5 и второй 6 элементы ИЛИ, элемент И 7, первый 8, второй 9, третий 10, четвертый 11, пятый 12 элементы задержки, три регистра 13, 14, 15, четыре блока элементов И 16, 17, 18, 19, первый 20 и второй 21 блоки элементов ИЛИ, три группы адресных входов 22, 23, 24, информационные входы 25, вход 26 обращения, выход 27 разрешения считывания, выход 28 ошибки, выходы 29 неисправных разрядов.

Формирователь сигнала ошибки 3 содержит группу инверторов 30, первый 31 элемент И, элемент ИЛИ 32, инвертор 33, второй 34 элемент И, шестой 35 элемент задержки, триггер 36, седьмой 37 элемент задержки. Накопитель 1 имеет информационную емкость, в три раза превышающую требуемую для решения задач системы.

Выходы накопителя 1 соединены со счетными входами контрольного регистра 2, выходы первой группы которого являются информационными выходами 25 устройства, выходами 29 неисправных разрядов которого являются выходы второй группы контрольного регистра 2, которые соединены с соответствующими информационными входами формирователя сигнала ошибки 3, первый и второй выходы которого являются соответственно выходом 27 разрешения считывания и выходом 28 ошибки устройства. Первый и второй синхровходы формирователя сигнала ошибки 3 соединены соответственно с выходами второго элемента задержки 9 и элемента И 7, первый и второй входы которого подключены соответственно к второму выходу формирователя сигнала ошибки 3 и к выходу четвертого элемента задержки 11, вход которого соединен с выходом первого элемента задержки 8, входом второго элемента задержки 9 и с первым входом первого элемента ИЛИ 5, второй вход и выход которого подключены соответственно к выходу элемента И 7 и первому входу второго элемента ИЛИ 6, второй вход которого соединен с входом первого элемента задержки 8 и выходом пятого элемента задержки 12, вход которого, вход сброса контрольного регистра 2 и вход сброса формирователя сигнала ошибки 3 объединены и являются входом 26 обращения устройства. Выход второго элемента ИЛИ 6 соединен с входом третьего элемента задержки 20, выход которого подключен к входу выборки накопителя 1. Выходы первого регистра 13 подключены к соответствующим адресным входам накопителя 1. Информационные входы второго 14 и третьего 15 регистров являются соответственно адресными входами первой 23 и второй 24 групп устройства. Выходы второго 14 и третьего 15 регистров подключены к входам групп соответственно первого 16 и второго 17 блоков элементов И, выходы которых соединены соответственно с входами первой и второй групп первого 20 блока элементов ИЛИ, выходы которого подключены к соответствующим входам первой группы сумматора 4, входы второй группы которого и входы группы четвертого 19 блока элементов И соответственно объединены и являются адресными входами 22 третьей группы устройства. Входы первого 16 и четвертого 19 блоков элементов И объединены и подключены к выходу пятого элемента задержки, к входу которого подключены вход установки нуля первого регистра 13 и вход установки нуля сумматора 4, выходы которого подключены к соответствующим входам группы третьего 18 блока элементов И, вход которого соединен с выходом первого элемента ИЛИ 5. Выходы третьего 18 и четвертого 19 блоков элементов И соединены соответственно с входами первой и второй групп второго 21 блока элементов ИЛИ, выходы которого подключены к соответствующим информационным входам первого регистра 13.

Накопитель 1 предназначен для хранения информации и может быть реализован на одной или нескольких БИС оперативной или постоянной памяти.

Контрольный регистр 2 предназначен для приема и хранения первого и второго операндов, а при необходимости и третьего операнда. Может быть реализован, например, на счетчиках, при этом для каждого разряда используется один двухразрядный счетчик.

Формирователь сигнала ошибки 3 обеспечивает контроль информации в контрольном регистре 2 и формирование сигнала разрешения считывания либо сигнала ошибки и управляющего сигнала для обращения к третьей области памяти накопителя 1. Может быть реализован по схеме прототипа.

Сумматор 4 обеспечивает формирование адреса операнда во второй или в третьей области памяти накопителя 1. Может быть реализован по типовой схеме.

Первый элемент ИЛИ 5 формирует стробирующий сигнал на вход третьего блока элементов И 18 и управляющего сигнала на вход третьего элемента задержки 10 по сигналам с выхода первого элемента задержки 8 или с выхода элемента И 7. Второй элемент ИЛИ 6 передает сигналы на запуск третьего элемента задержки 10. Элемент И 7 формирует управляющий сигнал по сигналу ошибки и сигналу с выхода четвертого элемента задержки 11.

Первый элемент задержки 8 обеспечивает формирование сигнала запуска на второй 9, третий 10 и четвертый 11 элементы задержки через интервал времени, обеспечивающий завершение первого цикла обращения к накопителю 1.

Второй элемент задержки 9 обеспечивает формирование сигнала на первый синхровход формирователя сигнала ошибки через интервал времени, обеспечивающий завершение второго цикла обращения к накопителю 1.

Третий элемент задержки 10 обеспечивает формирование сигнала на вход выборки накопителя 1 через интервал времени, обеспечивающий запись в первый регистр 13 адреса с третьей группы адресных входов 2 через четвертый блок элементов И 19 и второй блок элементов ИЛИ 21 или с выхода сумматора 4 через третий блок элементов И 18 и второй блок элементов ИЛИ 21.

Четвертый элемент задержки 11 обеспечивает формирование сигнала третьего обращения к накопителю 1 и на второй синхровход формирователя сигнала ошибки 3 через интервал времени, обеспечивающий формирование сигнала разрешения считывания или сигнала ошибки после второго обращения к накопителю 1.

Пятый элемент задержки 12 обеспечивает формирование сигналов первого обращения к накопителю 1 и разрешения записи первого адреса в первый регистр 13 через интервал времени, обеспечивающий обнуление первого регистра 13 по сигналу обращения к устройству.

Первый регистр 13 используется в качестве регистра адреса накопителя 1. Второй регистр 14 обеспечивает хранение смещения начального адреса второй области памяти относительно первой. Третий регистр 15 обеспечивает хранение смещения начального адреса третьей области памяти относительно первой. Первый 16, второй 17 блоки элементов И и первый блок элементов ИЛИ 20 обеспечивает пересылку содержимого второго 14 или третьего 15 регистров на вход сумматора 4.

Устройство работает следующим образом.

а) Настройка. В этом режиме в накопитель 1, состоящий из БИС оперативной или постоянной памяти, любым способом записана информация (цепи записи на чертеже не показаны), причем в трех любых разных областях накопителя записана одинаковая информация. Второй 14 и третий 15 регистры обнуляются (цепи установки нуля на чертеже не показаны) и в них записывается по первой 23 и второй 24 группам адресных входов соответственно смещение начального адреса второй и третьей области памяти накопителя 1 относительно первой области памяти и сохраняется до конца работы устройства.

б) Обращение к первой области памяти. На третью группу адресных входов 22 устройства поступает адрес обращения и сохраняется на входе. Запрос, поданный на вход обращения 26 устройства, стробирует блоки 2, 3, 4, 13 и через пятый элемент 12 задержки, блоки 16, 19, разрешая прием первого адреса через четвертый блок элементов И 19 и второй блок элементов ИЛИ 21 в первый регистр 13, а смещения второй области памяти через первый блок элементов И 16, первый блок элементов ИЛИ 20 на второй вход сумматора 4, на первый вход которого подается адрес первой области памяти и сумматор вычисляет номер ячейки второй области памяти. Одновременно с этим запрос через второй элемент ИЛИ 6 и третий элемент задержки 10 поступает на вход выборки накопителя 1. Производится считывание ранее записанной информации по адресу, соответствующему поданному на адресные входы накопителя 1 коду адреса от первого регистра 13. Считанная информация записывается в контрольный регистр 2, каждый разряд которого представляет собой, например, двухразрядный счетчик. В зависимости от считанной информации младший разряд каждого двухразрядного счетчика переключается или не переключается.

в) Обращение ко второй области памяти. После завершения первого цикла считывания из накопителя 1 происходит повторное обращение к нему через интервал времени, задаваемый первым элементом задержки 8. При этом задержанный сигнал запроса с выхода пятого элемента задержки 12 поступает через первый вход первого элемента ИЛИ 5 на второй вход третьего блока элементов И 18 и разрешает пересылку содержимого сумматора 4 через третий блок элементов И 18 и второй блок элементов ИЛИ 21 на вход первого регистра 13, обеспечивая обращение ко второй области памяти накопителя 1. С выхода первого элемента ИЛИ 5 сигнал поступает на первый вход второго элемента ИЛИ 6, с выхода которого через третий элемент задержки 10 он подается на управляющий вход выборки накопителя 1. При этом происходит считывание информации из второй области памяти накопителя 1 из ячейки, в которой была записана та же информация, что и в выданном в предыдущем такте адресе. Считанная информация поступает на входы контрольного регистра 2. Далее возможны два варианта функционирования.

1. Информация при первом и втором обращении совпадает. В этом случае после второго обращения на каждом из младших разрядов двухразрядных счетчиков контрольного регистра 2 устанавливается сигнал логического "0". Этот сигнал от всех разрядов контрольного регистра 2 поступает на первые входы формирователя 3 сигнала ошибки, далее через группу инверторов 30 на входы элемента И 31. По истечении времени, превышающее время выборки информации из накопителя 1, на второй вход формирователя 3 сигнала ошибки поступает сигнал от второго элемента задержки 9, который вызывает срабатывание элемента И 31. Сигнал совпадения через элемент ИЛИ 32 выдает на выход 27 сигнал разрешения считывания информации, которая устанавливается после второго обращения на старших разрядах двухразрядных счетчиков контрольного регистра 2, соединенных с информационными выходами 25 устройства. Поскольку эта информация, проверенная сравнением при считывании из двух областей памяти накопителя 1, признается истинной, она может быть использована процессором. Сигнал с выхода второго элемента задержки 9 разрешает пересылку содержимого третьего регистра 15 через второй блок элементов И 17 и первый блок элементов ИЛИ 20 на вход сумматора 4, который вычисляет адрес ячейки в третьей области памяти. При необходимости перед этим сумматор 4 обнуляется.

2. Информация при первом и втором обращении не совпадает в одном или нескольких разрядах, что является признаком неисправности. В этом случае производится обращение к третьей области памяти.

г) Обращение к третьей области памяти. После второго обращения на выходах одного или нескольких младших разрядов двухразрядных счетчиков контрольного регистра 2 устанавливается логическая "1". После подачи сигнал от второго элемента задержки 9 элемент И 31 не срабатывает, а на выходе 27 не появляется сигнал разрешения считывания. На первый вход элемента И 34 через инвертор 33 подается сигнал логической "1". После подачи на второй вход элемента И 34, задержанного на элементе задержки 35 сигнала от второго элемента задержки 9, элемент И 34 срабатывает и вызывает переключение триггера 36. В результате этого на выходе 28 устройства устанавливается сигнал ошибки. Этот сигнал подается на первый вход элемента И 7 и разрешает третье обращение к накопителю, так как на второй вход элемента И 7 будет подан сигнал запроса от входа 26 обращения через пятый 12, первый 8 и четвертый 11 элементы задержки. Через элемент И 7, первый 5, второй 6 элементы ИЛИ, третий элемент задержки этот сигнал подается на вход выборки накопителя 1. Этот же сигнал с выхода первого элемента ИЛИ 5 поступает на второй вход третьего блока элемента И 18, разрешая передачу третьего адреса с выхода сумматора 4 через третий блок элементов И 18 и второй блок элементов ИЛИ 21 на вход первого регистра 13 (при необходимости первый регистр 13 предварительно обнуляется). Считанная при третьем обращении информация поступает на входы всех разрядов контрольного регистра 2 и вызывает срабатывание соответствующих двухразрядных счетчиков, в результате чего на их старших разрядах и информационных выходах 25 устройства устанавливается информация, соответствующая истинной по мажоритарному принципу. После задержки на время считывания при третьем обращении, определяемой элементом задержки 37 формирователя сигнала ошибки 3, через элемент ИЛИ 32 на выходе 27 появляется сигнал разрешения считывания. По этому сигналу установившаяся на информационных выходах 25 устройства информация может быть использована процессором. Наличие на выходе 28 сигнала ошибки после второго обращения обеспечивает информацию о наличии неисправности в накопителе 1, состояние информации на выходах 29 неисправных разрядов устройства после второго обращения позволяет локализовать ошибку с точностью до разряда.

Пример конкретной реализации устройства.

Допустим накопитель 1 реализован на одной БИС. Первая область начинается с адреса 100, вторая - с адреса 200, третья - 300. Тогда в режиме настройки во второй регистр 14 записывается число 100, в третий регистр 15 - 200. При обращении, например, к ячейке 108 первое обращение производится по адресу 108, второе - по адресу 100 + 108 = 208, третье - по адресу 200 + 108 = 308. В качестве первой области памяти может быть использована, например, область памяти с начальным адресом 300. Тогда во второй регистр 14 записывается число 200, а в третий регистр 15 - число -100. При этом первое обращение производится в ячейке 308, второе - к ячейке 308 + (-200) = 108, третье - к ячейке 308 + (-100) = 208. При записи во второй регистр 14 и третий регистр 15 кода "0" все три обращения будут осуществляться к одной и той же ячейке.

При реализации накопителя 1, например, на трех БИС конструкция узла формирования второго и третьего адресов существенно упрощается, так как этот узел может использоваться только для формирования старших разрядов адреса.

Устройство позволяет записать информацию в трех разных БИС накопителя. При этом в случае отказа одной БИС работоспособность устройства сохраняется, т. е. надежность устройства увеличивается в два раза. При использовании в накопителе одной БИС надежность также увеличивается, так как появляется возможность записи одинаковой информации в разные области памяти. При отказе одной области памяти работоспособность устройства сохраняется. Кроме того, устройство имеет более широкую область применения. Оно может быть использовано в запоминающих устройствах с мажоритарным резервированием на уровне микросхем, в мажоритарных ЗУ с накопителем на одной микросхеме, а также может использоваться в ЗУ, в которых информация записана один раз, а считывание этой информации производится три раза из одной ячейки. Устройство может также существенно сократить потребную емкость накопителя (на одну треть), если информацию записать только в две области памяти, а третье считывание производить второй раз из первой или второй области памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1437917A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

Изобретение относится к запоминающим устройствам, в которых для повышения надежности используется мажоритарное резервирование на уровне микросхем памяти. Цель изобретения - повышение надежности и расширение области применения устройства. Устройство содержит накопитель 1, контрольный регистр 2, формирователь сигнала ошибки 3, сумматор 4, первый 5 и второй 6 элементы ИЛИ, элемент И 7, первый 8, второй 9, третий 10, четвертый 11, пятый 12 элементы задержки, первый 13, второй 14, третий 15 регистры, первый 16, второй 17, третий 18, четвертый 19 блоки элементов И, первый 20 и второй 21 блоки элементов ИЛИ. 2 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ, содержащее накопитель, контрольный регистр, формирователь сигнала ошибки, сумматор, первый и второй элементы ИЛИ, элемент И, с первого по пятый элементы задержки, причем выходы накопителя соединены со счетными входами контрольного регистра, выходы первой группы которого являются информационными выходами устройства, выходами неисправных разрядов которого являются выходы второй группы контрольного регистра, которые соединены с соответствующими информационными входами формирователя сигнала ошибки, первый и второй выходы которого являются соответственно выходом разрешения считывания и выходом ошибки устройства, первый и второй синхровходы формирователя сигнала ошибки соединены соответственно с выходами второго элемента задержки и элемента И, первый и второй входы которого подключены соответственно к второму выходу формирователя сигнала ошибки и к выходу четвертого элемента задержки, вход которого соединен с выходом первого элемента задержки, входом второго элемента задержки и первым входом первого элемента ИЛИ, второй вход и выход которого подключены соответственно к выходу элемента И и первому входу второго элемента ИЛИ, второй вход которого соединен с входом первого элемента задержки и выходом пятого элемента задержки, вход которого, вход сброса контрольного регистра и вход сброса формирователя сигнала ошибки объединены и являются входом обращения устройства, выход второго элемента ИЛИ соединен с входом третьего элемента задержки, выход которого подключен к входу выборки накопителя, отличающееся тем, что, с целью повышения надежности и расширения области применения устройства, в него введены первый, второй и третий регистры, с первого по четвертый блоки элементов И, первый и второй блоки элементов ИЛИ, причем выходы первого регистра подключены к соответствующим адресным входам накопителя, информационные входы второго и третьего регистров являются соответственно адресными входами первой и второй групп устройства, выходы второго и третьего регистров подключены к входам групп соответственно первого и второго блоков элементов И, выходы которых соединены соответственно с входами первой и второй групп первого блока элементов ИЛИ, выходы которого подключены к соответствующим входам первой группы сумматора, входы второй группы которого и входы группы четвертого блока элементов И соответственно объединены и являются адресными входами третьей группы устройства, входы первого и четвертого блоков элементов И объединены и подключены к выходу пятого элемента задержки, к входу которого подключены вход установки нуля первого регистра и вход установки нуля сумматора, выходы которого подключены к соответствующим входам группы третьего блока элементов И, вход которого соединен с выходом первого элемента ИЛИ, выходы третьего и четвертого блоков элементов И соединены соответственно с входами первой и второй групп второго блока элементов ИЛИ, выходы которого подключены к соответствующим информационным входам первого регистра.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1437917A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-12-15—Публикация

1990-10-09—Подача