(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1427360A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для деления чисел | 1985 |

|

SU1552180A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Устройство для деления чисел | 1986 |

|

SU1709308A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Устройство для деления | 1983 |

|

SU1166100A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

1

Изобретение относится к измерительной технике и может быть применено в цифровых измерительных приборах с пер)- вичной обработкой результатов измерений (для выполнения операции деления).

Известно устройство для деления чисел, представленных в виде цифровых :кодов, содержащее генератор тактовых импульсов, соединенный с первьп входом элемента И, вггорой вход которого подюшчен к выходу триггера управления, еГвыход - к регистру делителя и входу дересчетной схемы, выход которой соединен с регистром делимого, разрядные вьхходы регистров соединены соответственно с первыми входами двух схем сравнения, вторые входы которых соединены со счетчиками делителя и делимого, выход схемы сравнения делимого соед ней со входом сброса триггера управления, вход запуска которого соединен со входом устройства, а выход схемы сравнения делителя соединен со входом сбро

са решстра делителя и входом счетчика частного р. .

; Недостаток данного устройства - гро моздкость, так как оно содержит пять счетчиков (или регистров) при двух операндах и одном числовом результате.

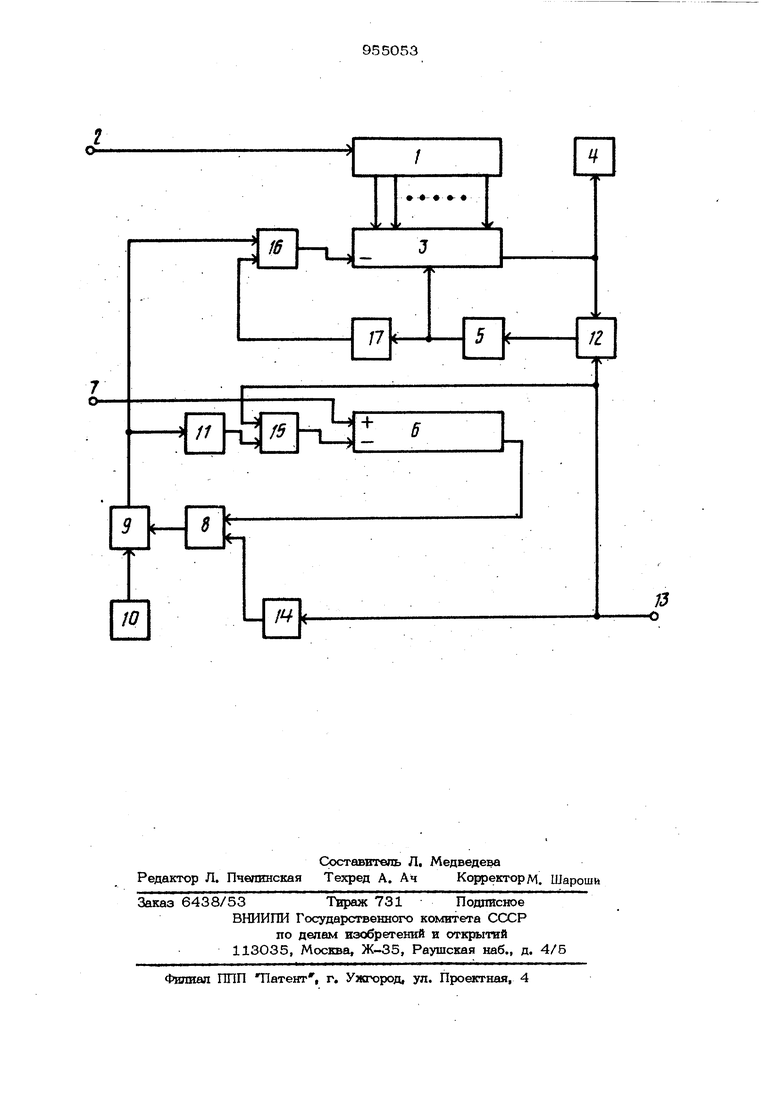

Наиболее близким к предлагаемому по технической сущности является устрой ство, содерншщее счетчик делителя, счетчик частного, реверсивный счетчик делителя, реверсивный счетчик делимого, генератор тактовых импульсов, триггер, элемент И, делитель частоты и форм рователь импульсов, причем информационный вход .счетчика делителя является входом делителя устройства, суммирукьШИЙ вход реверсивного счетчика делимого является входом делимого устройства, выход реверсивного счетчика делимого соединен со входом сброса триггера, едр нячный выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, разрядные выхс . |ды счетчика делителя соединены со6тБёт сггвенао с разрядными га:одами реверсИвного счетчика дешггепя, выход которого соединен с информационным входом счетчика частного, выход элемента И соединен с информационным входом делителя частоты 2 . Недостатком устройства является наличие погрешности, обусловленной тем, что при делении числа А на число В результат оказывается равным |i , так как импульсы на выходах обратного переноса старших разрядЬв реверсивных ; счетчиков появляк)тся после перехода их из состояния ОО...О в состояние 99...9. Если хотя бы одно из чисел А или В мало, то погрешность деления становится недопустимо большой. Цель изобретения - повьпыение точн ости деления. Поставленная цель достигается тем, что в устройство введены три элемента ИЛИ и два элемента задержки, хтричем вход первого элемента задержки объединен с первыми входами первого и второго элементов ИЛИ и является входом запуска устройства, выход первого эле мента задержки соединен с информационным входом триггера, второй вход первого элемента ИЛИ соединен с выходом ревфсивного счетчика делителя, а выход со входом формирователя импульсов, выход которого соединен со входом второго элемента задержки и установбчным входом реверсивного счетчика делителя, выход второго элемента задержки соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход - с вычитающим входом реверсивного счетчика делителя, вь1ход делителя частоты соединен со вторым входом второго элемента ИЛИ, выход которого соединен с вычитающим входом реверсивного счетчика делимого. На чертеже представлена фушадаональная схема устройства. Счетчик 1 Делителя, вход 2 делителя устройства, реверсивный счетчик; 3 делитшя, счетчик 4 частного, формирователь 5 импульсов, реверсивнь1Й счетчик 6; делимого, вход 7 делимого устройства, триггер 8, элемент И 9, генератор 10 тактовых импульсов, делитель 11 частоты, элемент ИЛИ 12, вход 13 запуска устройства, элемент 14 задержки, элеК1енты ИЛИ 15 и 16 И элемент 17 задержки. В устройстве информационный вход счетчика 1 делителя жсвляется входом 2 делителя устройства, суммируЮнций вход реверсивного счетчика i6 делимого - входом 7 делимого устройства, выход реверсивного счетчика 6 делимого соединен со входом сброса триггера 8, единичный выход которогосоединен с первым входом элемента И 9, второй вход которого соединен с выходом генератора 10 тактовых импульсов, разрядные выходы счетчика 1 делителя соединены соответственно с разрядными входами реверсивного счетчика 3 делителя, выход которого соединен с информационным входом счетчика 4 частнрго, выход элемента 9 И соединен с информационным входом делителя 11 частоты, вход элемента 14 задэриоси объединен с первыми входами элементов ИЛИ 12 и 15 и является входом 13 запуска устройства, выход элемен та 14 -задержки соединен с информационт ным входом триггера 8, второй вход элемента ИЛИ 12 соединен с выходом реверсивного счетчика 3 делителя, а выход - со входом формирователя 5 импульсов, выход которого соединен с выходом элемента 17 задержки и установочным входом реверсивн9го счетчика 3 делителя, выход элемента 17 задержки соедиHiSH с входом элемента ИЛИ 16, второй вход которого соединен с входом элемента И 9, а выход - с вычитанядим входом реверсивного счетчика 3 делителя, выход делителя 11 частоты соединен со вторым входом элемента ИЛИ 15, выход которого соединен С вычитающим входом реверсивного счетчика 6 делимого. Устройство работает следующим образом. На входы 2 и 7 устройства подаются последовательности импульсов, количество которых представляет соответственно делитель В и делимое А. После накопления этих импульсов в счетчиках 1 и 6 на вход 13 устройства поступает импульс, разрешающий начало операции деления. Этот импульс, воздействуя через элемент 15 ИЛИ на счетный вход в режиме вычитания счетчика 6, уменьшает код последнего на единицу. Одновременно этот же импульс через элемент ИЛИ 12 воздействует на формирователь 5 импульсов, который ра ешает запись в реверсивный счетчик 3 делителя кода ИЗ счетчика 1. Затем через элеметт 17 задержки и элемент 16 ИЛИ импульс поступает на счетный вход счетчика 3, что также уменьшает код, содержащийся в последнем, на единицу. Далее с опозданием, определяемым элементом 14 задержки от входного импульса включается 8, который, воздействуя на вход элемента 9 И, разрешает прохеткденне через него тактовых импульсов свьГхода генератора 10 через элемент ИЛИ 16 на вычитающий вход счетчика 3 и через элемент 15 ИЛИ - на вычитающий вход счетчика 6. После устан(жления в счетчике 3 ростояшш 99...9 импульс с выхода обратного переноса поступает на вход счетчика 4 частного и через элемент ИЛИ 12 на формирователь 5, который разрешает по управляющему входу счетчика 3 загшсь в него Кода из счетчика Затем через элемент 17 и элемент ИЛИ 16 импульс поступает на счетный вход счетчика 3, гго вызывает уменьши ние кода, содержащегося в последнем, на единицу. Далее импульсы генератора 10 такто вых импульсов снова поступают на входы реверсивного счетчика 3 делителя и реверсивного счетчика 6 делимого, и .работа устройства циклически повторяется до тех пор, пока счетчик 6 не переходит из состояния 00.,.О в состояние 99... 9 и импульс с выхода обратного переноса не перебрасывает триггер 8 в другое устойчивое состояние, после чего импульсы с выхода генератора 10 не П рохрдят через элемент И 9. Таким образом, в счетчике 4 оказьгаается код, равный частному кА/В (где k - коэффициент пересчета делителя 11). На этом процесс деления числа А на число В заканчивается. Для повторения пикла рабо ты устройства {для повторного деляпш чисел) необходимо установить счетчики 1, 4 и 6 в нулевое состояние. При таком построении устройства иэ чисел, содержащихся в реверсивном счет чике 3 делителя и реверсивном счётчике 6 делимого, дополнительно вычитается единица в моменты времени, не совпадак шие с моментами поступления на их счетные входы тактовых импульсов, что приводит к коррекции погрешности. Эффект от применения предлагаемого устройства обусловлен уменьшении погрешности вычислений, аппаратурной погрешности и измерений и, следовательно повьшгекием точности и снижением трудо емкости производственного контроля. Формула изобретения Устройство для деления, содержащее счетчик делителя, счет.чик частного, реверсивный счетчик делителя, реверсивный счетчик делимого, генератор тактовых импульсов, триггер, элемент И, делитель частоты и фор гарователь импульсов, при;чем информационный вход счетчика дели|теля является входом делителя устройства, суммирукишй вход реверсивного счетчика делимого является входом делимого устройства, выход реверсивного счетчика делимого соединен со входом сброса триггера, единичный выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, разрядные выходы счетчика делителя соединены соответственно с разрядными входами реверсивного счетчика делителя, выход которого соединен с информационным входом счетчика частного, выход элемента И соединен с информационным входом делителя частоты, отличающееся .тем, что, с целью повьш1ения точности, в него введены три эйемента ИЛИ, два элемента задержки, причем вход первого элемента ;эадержки объединен с первыми входами первого и второго элементов ИЛИ и является входом запуска устройотва, выкоа первого элемента задержки соединен с информационным входом триггера, второй вход первого эла лента ИЛИ .соединен с клходом реверсивного счетчгаш делителя, а выход - со вкодом формирователя импульсов, выход которого соединен со входом второго элемента задержки и установочным входом реверсивного счетчика делителя, выход второго элемента задержки соединен с первым входом третьего элемента ИЛИ, вход которого соединбя с выходом элемента И, а выход - с вычитающим входом jpeверсивного счетчика делителя, выход делителя частоты соединен со вторым . входом второго элемента ИЛИ, выход которого соепяиен с вычитающим входом реверсивного счетчика делимого. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 434413, Kn.G 06 F 7/52, 1972. 2.Радио, 1978, № 5, с. 37 - 38 (врототип).

Авторы

Даты

1982-08-30—Публикация

1980-12-29—Подача