Изобретение относится к вычисли тельной технике и может быть использовано в интегральных полупроводниковых схемах цифровых и запоминанмцих устрюйств, в частности в Ьольших интегральных схемах запоминающих устройств с произвольной выборкой на основе структур металл-диэлектрикполупроводник (МДП БИС ЗУПВ).

Известен адресный формирователь, содержащий стробируемую чувствительную схему, выполненную по балансной схеме с триггерными связями. В плечи схемы введена конструктивная несимметрия, влияние которой эквивалентно тому, как если бы в симметричной схеме при входном сигнале, равном нулю, ко входу фордшрователя было приложено отрицательное напряжение, абсолютная величина которого в оптимальном случае равна среднему значению между уровняиш Лог О и Лог 1 ТТЛ логики, т.е. примерно 1,5 В 1.

Недостатком такого адресного формирователя является разбаланс импедансов на плечи чувствительного Tjairгера, обусловленный наличием конструктивной .несимметрий плеч. Это приводит к зависимости порога срабатывания чувствительной схемы от дли|т льности фронта стробирующего сигнала. При этом в случае больших разб « росов длительностей фронтов входные уровни порогов срабатывания некоторой части формирователей могут уходить за пределы норм уровней ТТЛ (0,4-2,4 В), что приводит к неработоспособности схемы.

Наиболее близким по технической

10 сущности к предлагаемому является адресный формирователь, содержащий выходной буферный усилитель и чувствительный элемент, состоящий из симметричного триггера, плечи которого

5 подключены к выходному буферному усилителю и двух пар последовательно включенных транзисторов - входного и транзистора связи, опорного и транзистора связи, причем стоки

20 транзисторов связи этих пар н затворы входного и опорного транзисторов подключены к соответствующим плечам транзистора, затворы транзисторов связи подключены к первой тактовой шине,исток опорного транзистора одной пары подключен к шине нулевого потенциала,а исток входного транзистора другой - к входной шине 2. Транзисторы связи транзисторных

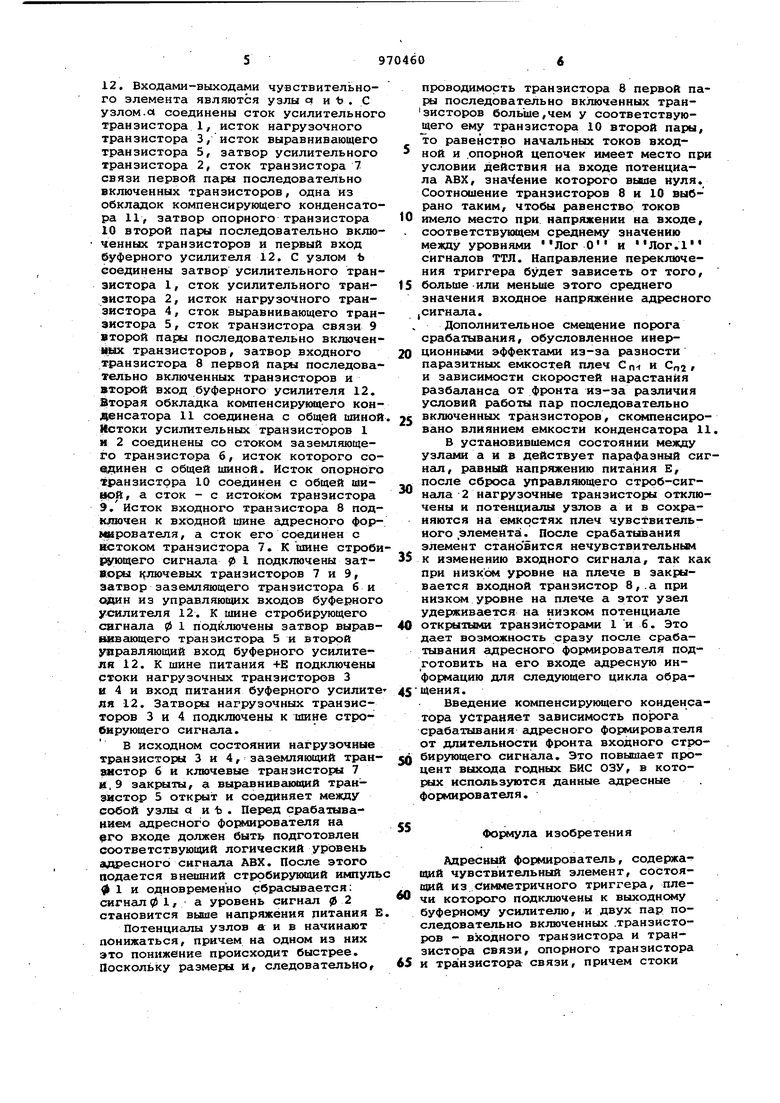

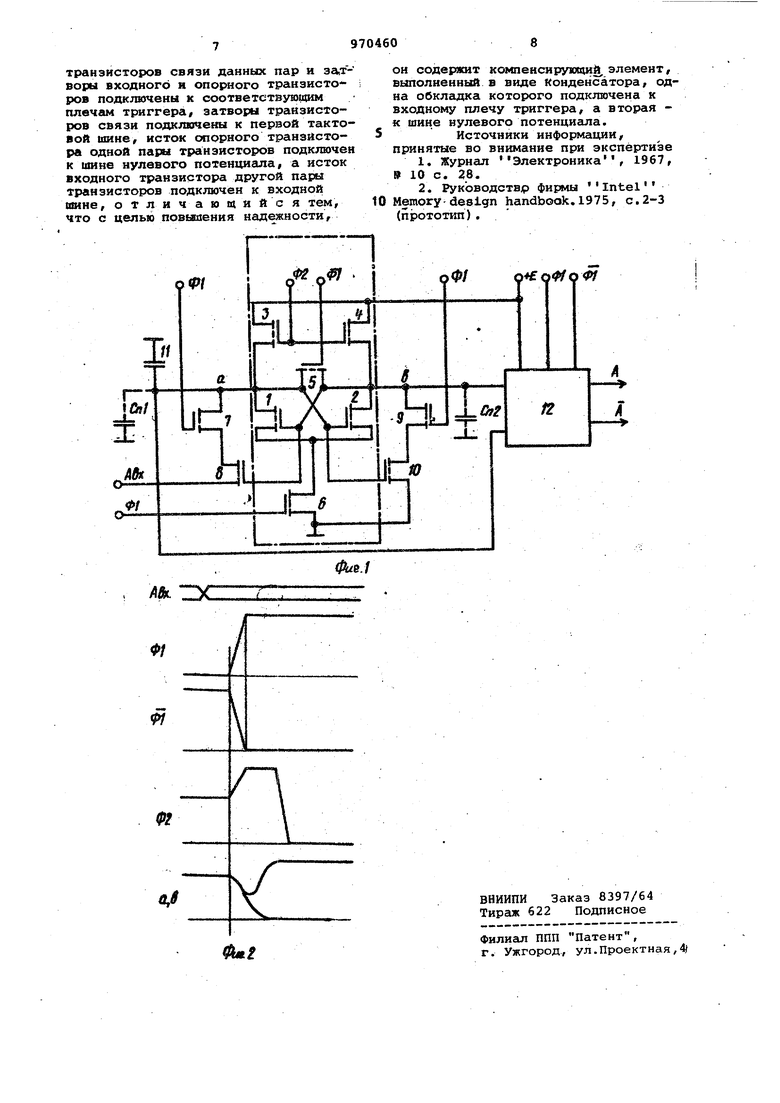

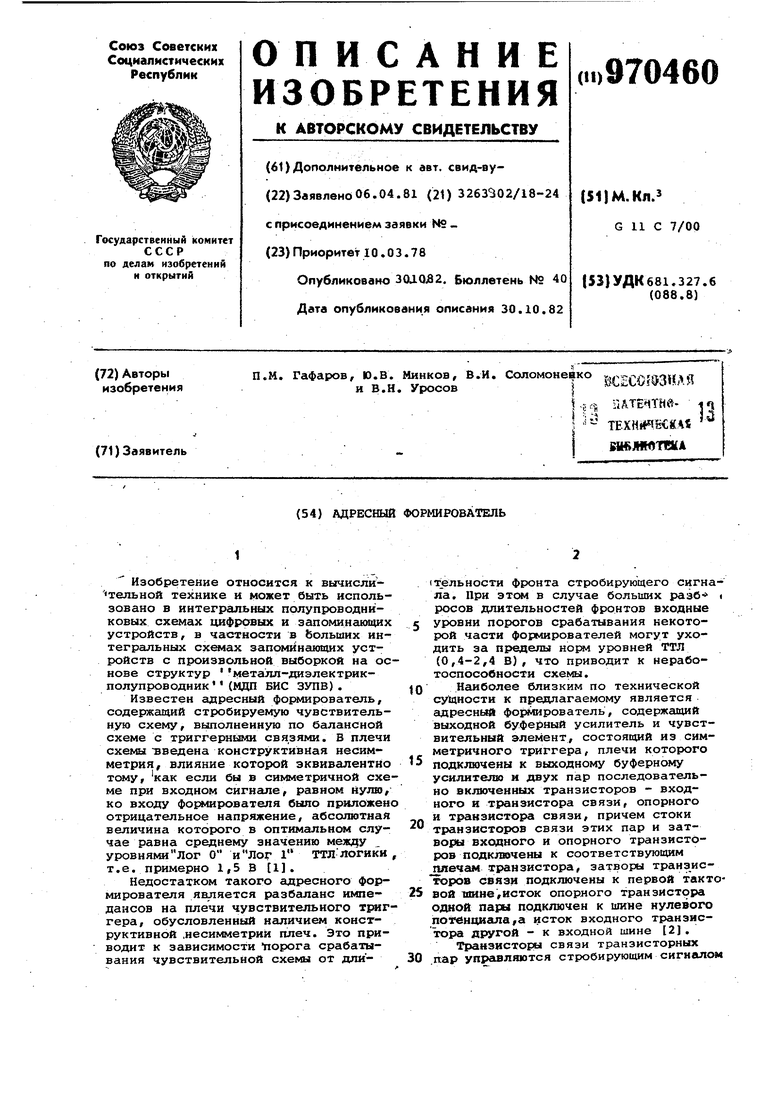

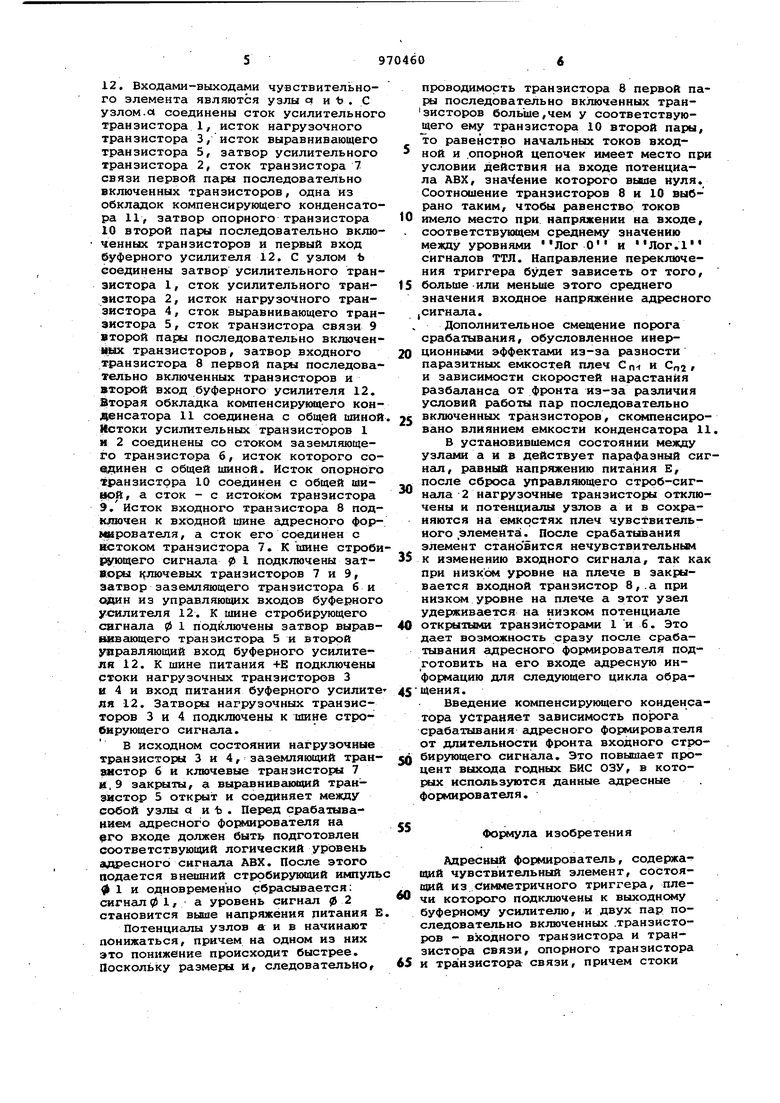

30 пар управляются стробирующим сигналом и сложат для отключения плеч тригге на период его подготовки,входной и опорный транзистоЕяд транзисторных п служат для смещения нуля схемы до уровня 1,5 В, для чего входной тран зистор, объединенный с входной адресной шиной, имеет большую ширину канала и, соответственно, большую проводимость в открытом состоянии, чем опорный транзистор, соединенный с шиной нулевого потенциала. Затворы этих двух транзисторов включены перекрестно на противоположные плечи триггера, что создает дополнительную положительную обратную-связь и обеспечивает автоматическое отключение схемы от входа лри ее срабатывании. Таким образом, к плечам триггера оказываются подключенными несбалансированные эквивалентные емкости. Направление опрокидывания триггера из уравновешенного состояния определяется в течение процесса установлен ния на истоках усилительных транзисторов низкого потенциала при включении стробирующим сигналом заземляющего транзистора. Чем быстрее происходит это включение, что зависит от длительности фронта стробирующего сигнсша, тем в большей степени на величину и знак начального парафазно сигнала оказывает влияние разность постоянных времени плеч триггера. В частности, плечо, имеющее большую емкость,, при статически сбалансированных сигналах будет при срабатывании триггера иметь более высокий потенциал, чем противоположное плечо Разность эквивалентных емкостных нагрузок на плечи транзистора является лишь одной из двух причин, обус лавливающих зависимость порога сраг батывания от длительности фронта стробирующего сигнала. Направление переключения триггера зависит также от соотношения скоростей изменения токов через пары последовательно включенных транзисторов в момент включения схемы стробирующим сигнало Поскольку вблизи точки баланса входная и опорная пары транзисторов работают при различных приложеннызс к ним разностях потенциалов, то соотнсядение скоростей изменения токов в этих цепочках зависят от скоростивключения схемы. Действия расссмотренных причин складываются и приводят к повышению порога срабатывания при уменьшении длительности фронта стробирующего сигнала. В соответстви с экспериментальными данньтми при из менении длительности фронта включения от 10 НС до 40 НС изменение порога срабатывания составляет 0,6 Таким образом, имеет неста бильность порога срабатывания адрес кого формирователя при изменении длительности фронта стробирующего сигнала. Эта нестабильность, наряду с технологическими разбросами параМетров,а также температурными уходами,дает дополнительный процент схем,входные уровни срабатывания которых лежат ниже 0,4 В или выше 2,4 В. Такие схемы являются браком. Современные ВИС ЗУПВ емкостью-16384 бит и ыше содержат 14 и более адрес1улх формирователей на кристалле, а за норму уровня срабатывания любого из них означает брак изделия в целом, поэггому для таких БИС дополнительная нестабильность уровней срабатывания адресных формирователей приводи к значительному понижению процента выхода годных изделий при их изготовлении. Цель изобретения - повышение надежности адресного фОЕ 4ироватёля. Поставленная цель достигается тем, что в адресный формирователь, содержащий чувствительный элемент, состоящий из симметричного триггера, плечи которого подключены к выходному буферному усилителю и двух пар последовательно включенных транзистороввходного транзистора и транзистора связи, опорного транзистора и транзистора связи, причем стоки транзисторов связи этих пар и затворы входного и опорного транзисторов подключены к соответствующим плечам триггера, затворы транзисторов связи подключены к первой тактовой шине, исток опорного транзистора одной парц транзисторов подключены к шине нулевого потенциала, а исток входного тра:нзистора другой - к входной шине, введен компенсирующий элемент, выполненный в виде конденсатора, одна обкладка которого подключена к входному плечу триггера а вторая к шине нулевого потенциала. Емкость конденсатора выбирается такой, чтобы скомпенсировать действия двух рассмотренных выше факторов, обуславливающих зависимость порога срабатывания от фронта стробирующего сигнала. На фиг. 1 приведена принципиальная электрическая схема предлагаемого адресного форялирователя; на фиг. 2 - временные диаграммы, поясняющие его работу. Адресный формирователь содержит чувствительный элемент, в состав которого входит управляегфлй триггер, состоящий из 2-х усилительных транзисторов 1 и 2, охваченный триггерной связью, двух нагрузочных транзисторов 3 и 4, выравнивающего транзистора 5 и заземляющего транзистора 6 , две пары последовательно включенных транзисторов, входная (транзисторы 7 и 8) и опорная (транзисторл 9 и 10) и компенсируюшлй конденсатор 11, а также буферный усилитель

i2. Входами-выходами чувствительного элемента являются узлы « и Ъ, С узлом.а соединены сток усилительного транзистора 1, исток нагрузочного транзистора 3, исток выравнивающего транзистора 5, затвор усилительного транзистора 2, сток транзистора 7 связи первой пары последовательно включенных транзисторов, одна из обклсшок компенсирующего конденсатора 11, затвор опорного транзистора 10 второй пары последовательно включенных транзисторов и первый вход буферного усилителя 12. С узлом Ь соединены затвор усилительного транзистора 1, сток усилительного транзистора 2, исток нагрузочного транзистора 4, сток выравнивающего транзистора 5, сток транзистора связи 9 второй пары последовательно включениях транзисторов, затвор входного транзистора 8 первой пары последовательно включенных транзисторов и второй вход буферного усилителя 12. Вторая обкладка компенсирующего конденсатора 11 соединена с общей шиной Истоки усилительных транзисторов 1 и 2 соединены со стоком заземляющего транзистора 6, исток которого соединен с общей шиной. Исток опорного ijpaH зистора 10 соединен с общей шиapiR, а сток - с истоком транзистора 9, Исток входного транзистора 8 подключен к входной тине адресного формирователя, а сток его соединен с истоком транзистора 7. К шине стробийпощего сигнала 0 1 подключены затeopta. 1 лючевых транзисторов 7 и 9, затвор заземляющего транзистора б и один из управляющих входов буферного усилителя 12. К шине стробирующего сагнала 0 1 подключены затвор выравнивающего транзистора 5 и второй уиравляющий вход буферного усилителя 12. К шине питания +Б подключены стоки нагрузочных транзисторов 3 и 4 и вход питания буферного усилите ля 12. Затворы нагрузочных транзисторов 3 и 4 подключены к шине стробирующего сигнала.

В исходном состоянии нагрузочные транзисторы 3 и 4, заземляющий транвнстор 6 и ключевые транзисторы 7 1. 9 закрыты, а выравнивающий транда|стор 5 открыт и соединяет между собой узлы о и Ъ . Перед срабатыва- нием адресного формирователя на его входе должен быть подготовлен соответствующий логический уровень адресного сигнала АВХ. После этого подается внешний стррбирующий импуль 1 и одновременно сбрасывается: сигнал 01, а уровень сигнал 02 становится выше напряжения питания Б

Потенциашы узлов айв начинают понижаться, причем на одном из них это понижение происходит быстрее. Поскольку размеры и, следовательно.

проводимость транзистора 8 первой паЕ« последовательно включенных транзисторов больше,чем у соответствующего ему транзистора 10 второй пары, то равенство начальных токов входной и опорной цепочек имеет место при условии действия на входе потенциала АВХ, значение которого выше нуля. Соотношение транзисторов 8 и 10 выбрано таким, чтобы равенство токов

0 имело место при напряжении на входе, . соответствукнцем среднему значению между уровнями О и Лог.1 сигналов ТТЛ. Направление переключения триггера будет зависеть от того,

5 больше или меньше этого среднего

значения входное напряжение гщресногс (Сигнала.

Дополнительное смещение порога срабатывания, обусловленное инер-

0 ционными эффектами из-за разности паразитных емкостей плеч Cn-t и С„2 t и зависимости скоростей нарастания разбаланса от фронта из-за различия условий работы пар последовательно

5 включенных транзисторов, скомпенсировано влиянием емкости конденсатора 11.

В установившемся состоянии между узлами айв действует парафазный сигНсш, равный напряжению питания Е, после сброса управляющего строб-сиг нала 2 нагрузочные транзисторы отключены и потенциёшы узлов айв сохраняются на емкостях плеч чувствительного элемента. После срабатывания элемент становится нечувствительным

5 к изменению входного сигнала, так как при нИзкбм уровне на плече в закрывается входной транзистор 8,.а при низком уровне на плече а этот узел удерживается на низксмл потенциале

0 открытыми транзисторами 1 и 6. Это дает возможность сразу после срабатывания адресного формирователя подготовить на его входе адресную информацию для следующего цикла обра5имения.

Введение компенсирукхцего конденсатора устраняет зависимость порога срабатывания адресного формирователя от длительности фронта входного строл бирующего сигнала. Это повышает процент выхода годных БИС ОЗУ, в котоЕих используются данные адресные формирователя.

55

Формула изобретения

Адресный формирователь, содержащий чувствительный элемент, состоящий из симметричного триггера, плечи которого подключены к выходному буферному усилителю, и двух пар последовательно включенных .транзисторов - входного транзистора и транзисто1ра связи, опорного транзистора

65 и транзистора связи, причем стоки

транзисторов связи данных пар и эа,творы входного и опорного транзисторов подключены к соответствующим плечам триггера/ затворы транзисторов связи подключены к первой тактовой шине, исток опорного транзистора одной пары транзисторов подключен к ишне нулевого потенциала, а исток входного транзистора другой пары транзисторов подключен к входной шине, отличающийся тем, что с целью повышения надежности.

.j

Ith9 Atl I

Q«Pf

%

I

он содержит компенсирующий, элемент, выполненный в виде конденсатора, одна обкладка которого подключена к входному плечу триггера, а вторая к шине нулевого потенциала. Источники информации/

принятые во внимание при экспертизе

1.Журнал Электроника, 1967, 10 с. 28.

2.Руководству Intel Memory-design handbook.1975, с.2-3

(прототип).

41оФ1

Ttr

iQ bLA

1

I

EL

12

Off

Г

./

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Адресный формирователь | 1988 |

|

SU1624521A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель на кмдп-транзисторах | 1979 |

|

SU862236A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-06—Подача