Изобретение относится к вычислитель ной технике и предназначено для контроля блоков оперативной памяти.

Целью изобретения является повьпиенне надежности устройства.

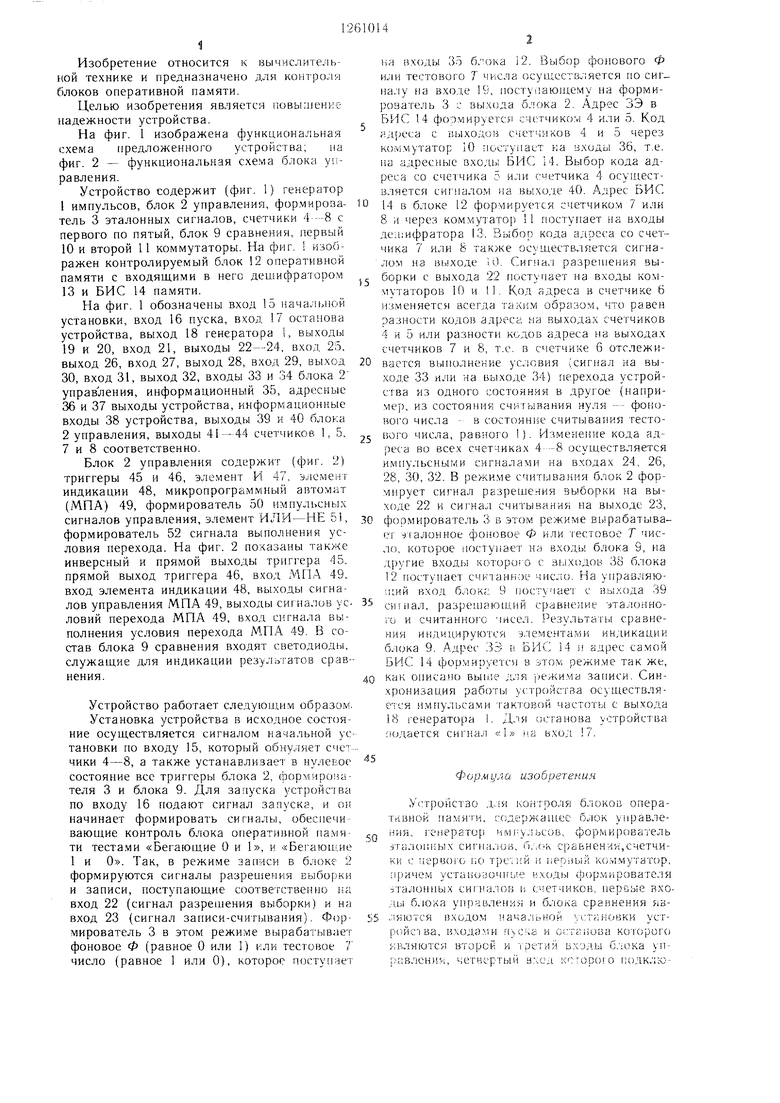

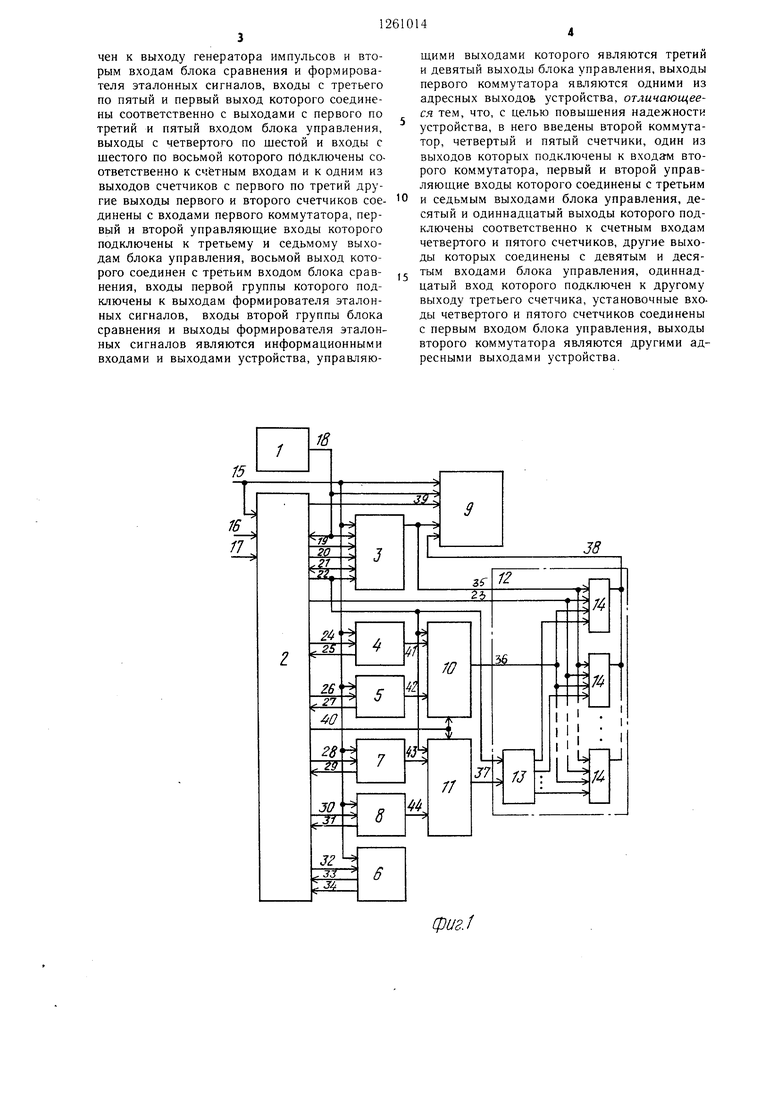

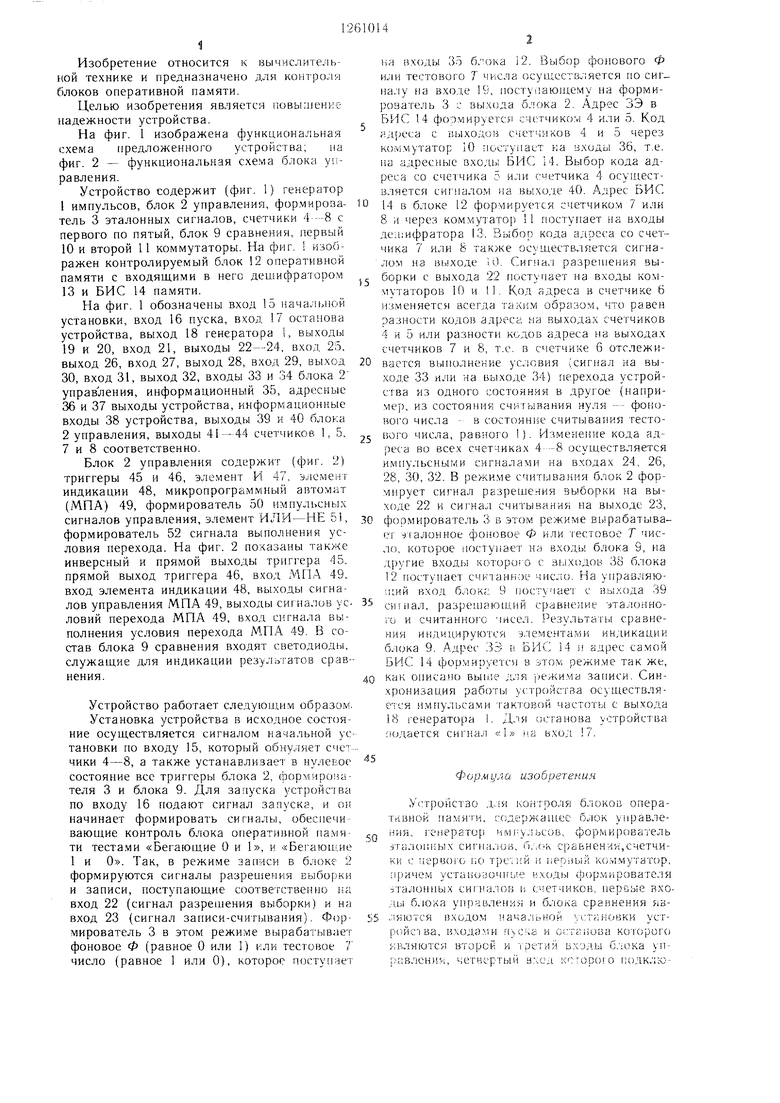

На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 - функциональная схема блока уи- равления.

Устройство содержит (фиг. 1) генератор

1импульсов, блок 2 управления, формирователь 3 эталонных сигналов, счетчики 4 --8 с первого по пятый, блок 9 сравнения, первый 10 и второй 11 коммутаторы. На фиг. 1 изображен контролируемый блок 12 оперативной памяти с входящими в него дешифратором 13 и БИС 14 памяти.

На фиг. 1 обозначены вход 15 начальной установки, вход 16 пуска, вход 17 останова устройства, выход 18 генератора 1, выходы 19 и 20, вход 21, выходы 22-24, вход 25, выход 26, вход 27, выход 28, вход 29, выход 30, вход 31, выход 32, входы 33 и 34 блока 2 управления, информационный 35, адресные 36 и 37 выходы устройства, информационные входы 38 устройства, выходы 39 и 40 блока

2управления, выходы 41-44 счетчиков 1, 5, 7 и 8 соответственно.

Блок 2 управления содержит (фиг. 2) триггеры 45 и 46, элемент И 47, э.;1емент индикации 48, микропрограммный автомат (МПА) 49, формирователь 50 импульсных сигналов управления, элемент ИЛИ-НЕ 5, формирователь 52 сигнала выполнения условия перехода. На фиг. 2 показаны также инверсный и прямой выходы триггера 45. прямой выход триггера 46, вход МПА 49. вход элемента индикации 48, выходы сигналов управления МПА 49, выходы сигналов условий перехода МПА 49, вход сигнала выполнения условия перехода МПА 49. В состав блока 9 сравнения входят светодиоды, служащие для индикации результатов сравнения.

Устройство работает следующим образом.

Установка устройства в исхо.дное состояние осуществляется сигналом начальной установки по входу 15, который обнуляет сче чики 4-8, а также устанавливает в нулевое состояние все триггеры блока 2, формиро и - теля 3 и блока 9. Для запуска устройства по входу 16 подают сигнал запуска, и он начинает формировать сигналы, обеспечи вающие контроль блока оперативной памяти теста.ми «Бегающие О и 1, и «Бегаюьг.ие 1 и О. Так, в режиме записи в блоке 2 формируются сигналы разрец ения выборки и записи, поступающие соответственно iia вход 22 (сигнал разрешения выборки) и на вход 23 (сигнал записи-считывания). Oi)p- мирователь 3 в этом режиме вырабатывает фоновое Ф (равное О или 1) или тестовое Т число (равное 1 или 0), которое поступает

на входы 35 блока 12. Выбор фонового Ф или тестового 7 числа ()суи1сств;:яется по сигналу на входе И, посту 1ающему на формирователь 3 L выхода oj OKa 2. Адрес ЗЭ в БИС 14 фоомируется счетчиком 4 или 5. Код

с ныходон счетчиков 4 и 5 через коммутатор 10 поступает на входы 36, т.е. lia адресные входы БИС i4. Выбор кода адреса со счетчика 5 или счетчика 4 осуществляется сигиало.м иа выходе 40. Адрес БИС

14 в блоке 12 формируется счетчиком 7 или 8 и через коммутатор 11 поступает на входы дешифратора 13. Выбор кода адоеса со счетчика 7 или 8 также осуществл5 ется сигналом на выходе UJ. Сигнал разрешения выборки с выхода 22 постуг1ает на входы коммутаторов 10 и 11. Код адреса в счетчике 6 изменяется всегда таким образом, что равен разности кодов адреса на выходах счетчиков 4 и 5 или разности кодов адреса на выходах счетчиков 7 и 8, т.е. в счетчике 6 отслежиБается выполнение ус.ювия (сипгал на выходе 33 HJiH на выходе 34) перехода устройства из одного состояния в другое (например, из состояния считывания нуля -- фопо- 1Ю1 о числа - в cocTOHHiic считывания тестового числа, равного 1). Измене1 ие кода ад-- реса во всех счетчиках 4--8 осуществляется импу. 1ьсными сигналами на вхо.дах 24, 26, 28, 30, 32. В режиме считывания блок 2 формирует сигнал разрешения выборки на выходе 22 и сигнал считывания па выходе 23,

формирователь 3 в этом режиме вырабатывает эталонное фоиювое Ф или тестовое Т число, которое поступает на входы блока 9, на другие входы KOTOpoi O с аыходов 38 блока 12 поступает считанное чис:1о. На управляю- ;:шй вход блока 9 иостучает с выхода 39

СИ нал, |)азре111ающий сравнение этало({но- i o и считанно1 с чисел. Результаты сравнения индицируются э.лементаг.ли индикации бл(жа 9. .Адрес ЗЭ в БИ( 14 н адрес самой БИС 14 формируется в этом режиме так же,

как описано выи.ке л.ля |1е.;кима записи. Синхронизация работь устройства осуществляется и.мпульсами тактовой частоты с выхода 18 генератора 1. Для останова устройства

Роомили изооретения

зталошгых сигиа. юв, ().,( К сравнения,счетчики с uepBorcj iO т) и пеоиый коммутатор. ;|)ичем устаиоаочшле вхс|Ды формирователя эталонных сигналов и счетчиков, первые входы блока управления и блока сравнения яв- .лянзтся входом иача. чл инсгьзки устройства, входа-ли пчс ха и ocTaiioua кот орого являются второй и третий входы б;:ока уп- : авлен1 и, четнерты(1 Kcropojo 1;е)дклх}чен к выходу генератора импульсов и вторым входам блока сравнения и формирователя эталонных сигналов, входы с третьего по нятый и первый выход которого соединены соответственно с выходами с первого по третий и пятый входом блока управления, выходы с четвертого по шестой и входы с шестого по восьмой которого пбдключены соответственно к счётным входам и к одним из выходов счетчиков с первого по третий друШ.ИМИ выходами которого являются третий и девятый выходы блока управления, выходы первого коммутатора являются одними из адресных выходоь устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй коммутатор, четвертый и пятый счетчики, один из выходов которых подключены к входам второго коммутатора, первый и второй управляющие входы которого соединены с третьим

гие выходы первого и второго счетчиков сое- 0 и седьмым выходами блока управления, де- динены с входами первого коммутатора, первый и второй управляюш,ие входы которого подключены к третьему и седьмому выходам блока управления, восьмой выход которого соединен с третьим входом блока сравнения, входы первой группы которого подключены к выходам формирователя эталонных сигналов, входы второй группы блока сравнения и выходы формирователя эталонных сигналов являются информационными входами и выходами устройства, управляюсятыи и одиннадцатый выходы которого подключены соответственно к счетным входам четвертого и пятого счетчиков, другие выходы которых соединены с девятым и деся- |, тым входами блока управления, одиннадцатый вход которого подключен к другому выходу третьего счетчика, установочные входы четвертого и пятого счетчиков соединены с первым входом блока управления, выходы второго коммутатора являются другими адресными выходами устройства.

Ш.ИМИ выходами которого являются третий и девятый выходы блока управления, выходы первого коммутатора являются одними из адресных выходоь устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй коммутатор, четвертый и пятый счетчики, один из выходов которых подключены к входам второго коммутатора, первый и второй управляющие входы которого соединены с третьим

и седьмым выходами блока управления, де-

сятыи и одиннадцатый выходы которого подключены соответственно к счетным входам четвертого и пятого счетчиков, другие выходы которых соединены с девятым и деся- тым входами блока управления, одиннадцатый вход которого подключен к другому выходу третьего счетчика, установочные входы четвертого и пятого счетчиков соединены с первым входом блока управления, выходы второго коммутатора являются другими адресными выходами устройства.

ф{/а/

(pl/2.l

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для ввода информации | 1986 |

|

SU1363225A2 |

| Устройство для записи-считывания звуковых сигналов | 1989 |

|

SU1712964A1 |

| Устройство для контроля адресных цепей блоков памяти | 1984 |

|

SU1200347A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

Изобретение относится к вычислительной технике и предназначено для контроля блоков оперативной памяти. Целью изобретения является повышение надежности устройства. Устройство содержит генератор импульсов, формирователь эталонных сигналов, счетчики с первого по пятый, коммутаторы, блок сравнения и блок управления, задающий программы контроля тестами «Бегущие О и 1 или «Бегущие 1 и О. Устройство позволяет контролировать как ячейки памяти, относящиеся к одной БИС памяти, так и время выборки каждой БИС памяти, для чего в устройство введены четвертый и пятый счетчики, формирующие адрес БИС памяти, и второй коммутатор. 2 ил. IC о

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| Солесос | 1922 |

|

SU29A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU902077A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-30—Публикация

1985-04-25—Подача