«

Изобретение относится к преобразовательной технике и может быть использовано в системах электропитания и электропривода для преобразования постоянного напряжения в многофазное переменное напряжение, модулированное по синусоидальному закону широтно-импульсной модуляции (ШИМ) с жестким алгоритмом переключения силовых ключей инвертора.

Целью изобретения является улучшение качества выходного напряжения и обеспечение возможности реверса.

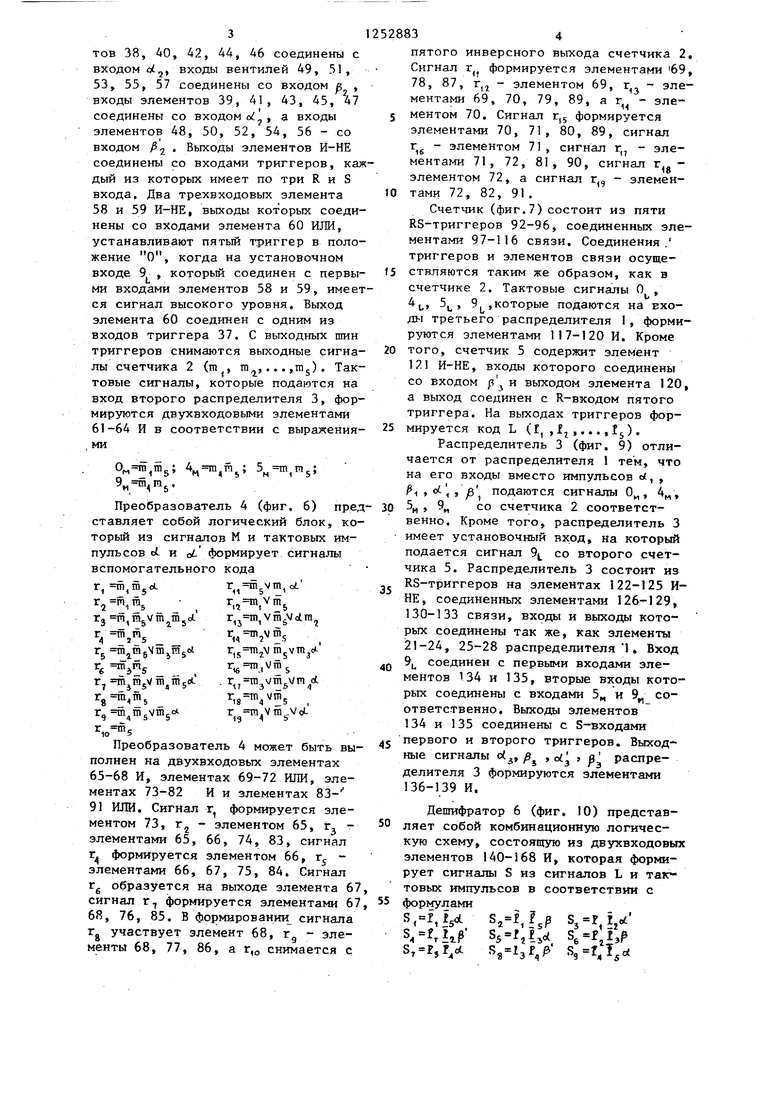

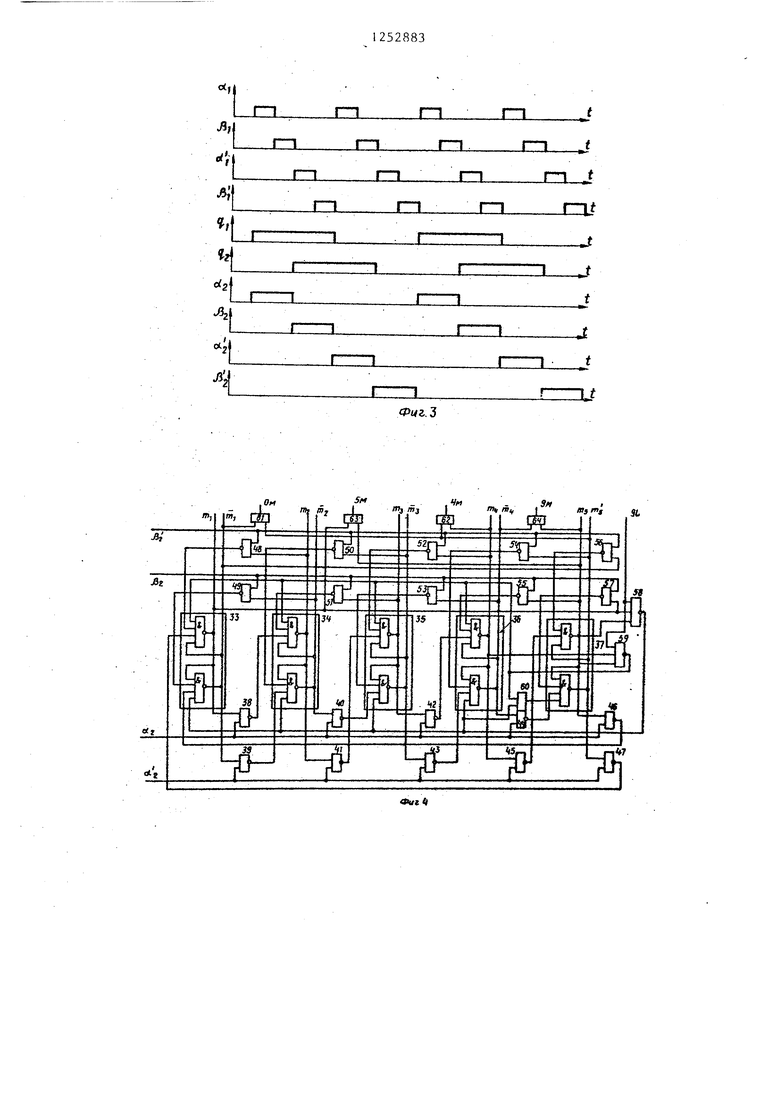

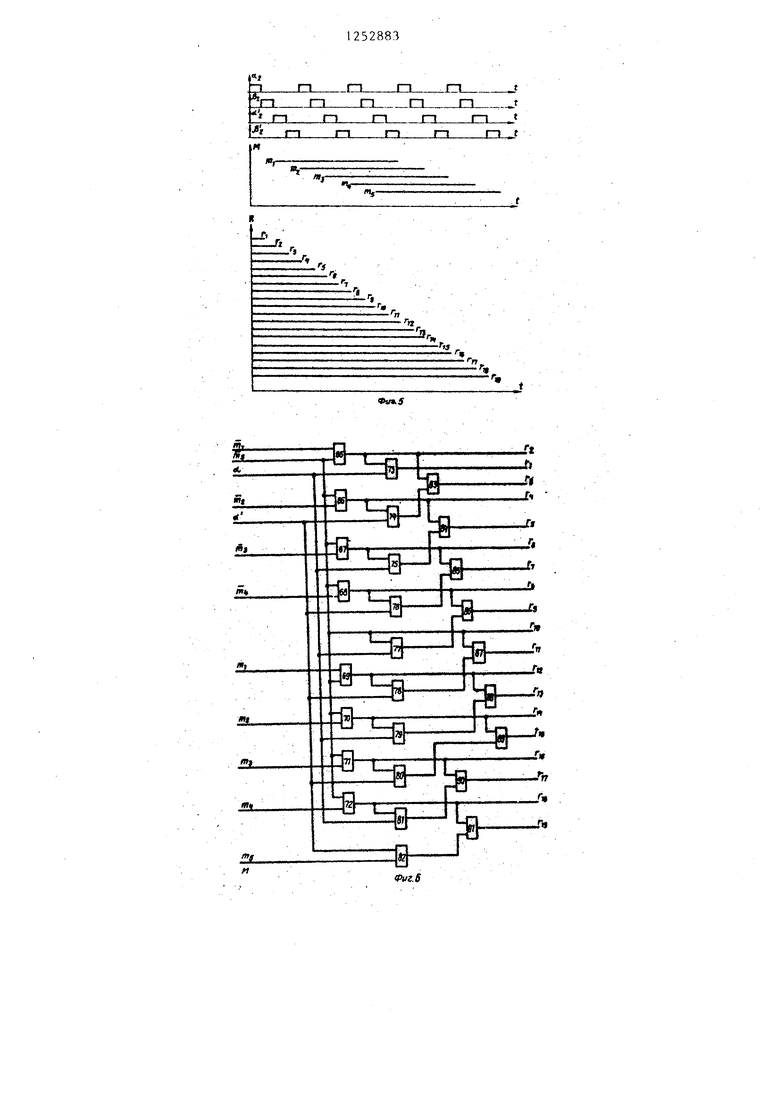

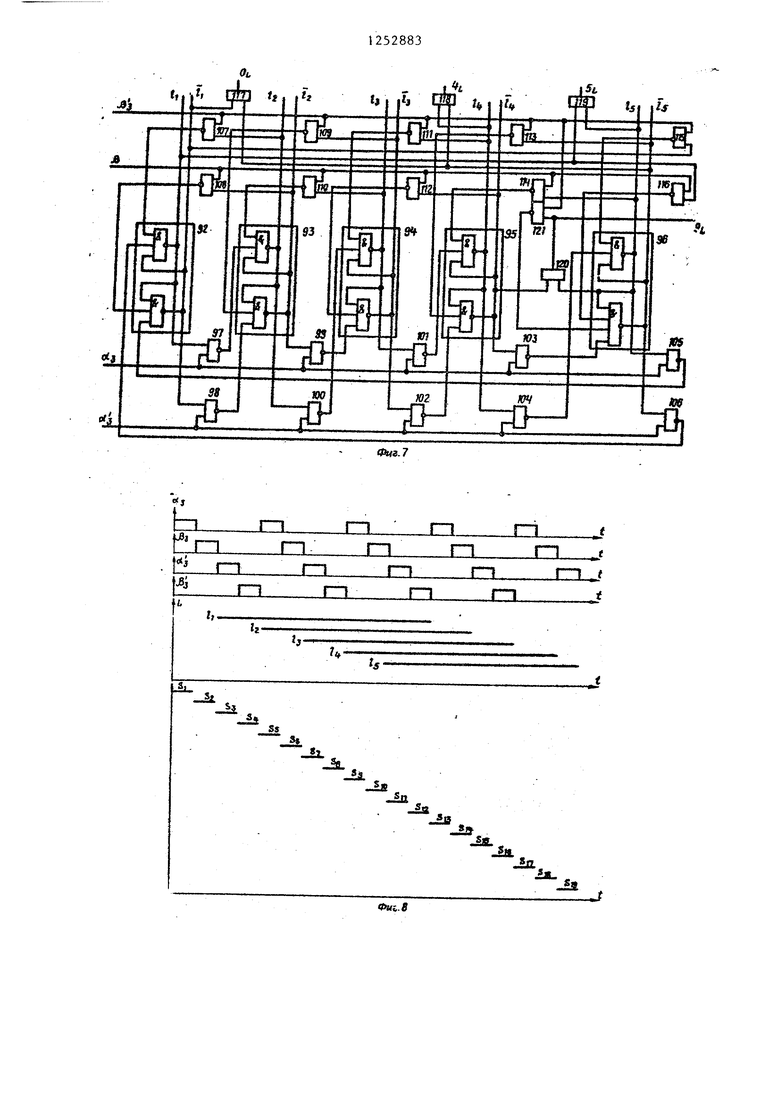

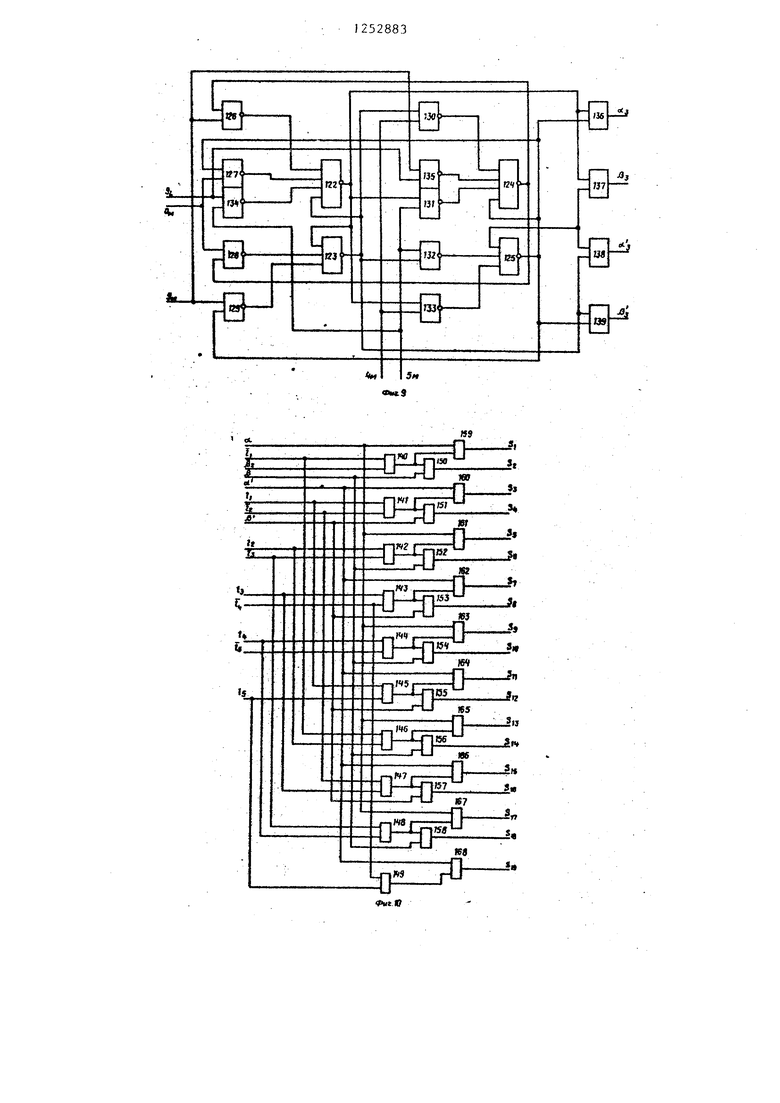

На фиг, 1 приведена структурная схема устройства; на фиг. 2 - принципиальная схема первого и третьего распределителей; на фиг. 3 - диаграммы входных сигналов C/L , ft , о1., р сигналов триггеров q , q и выходных сигналов о(.,

Ш

1252883

р соединены с первыми входами пер вого счетчика 2 Джонсона. Тактовые выходы 0|, 4, 5, 9„ счетчика 2 со динены с тактовыми входами второго

5 распределителя 3 импульсов, а выходы счетчика 2 и входыot, иы соединены с входами преобразователя 4 кодов. Выходы 0 , , oil, , f, распре делителя 3 соединены с входами второго счетчика 5 Джонсона и входами. дешифратора 6. Тактовые выходы 0, и L) L второго счетчика 5 соединены с входами третьего распределителя 1, полностью аналогичного пе

5 вому распределителю 1, а входы счет чика 5 соединены со входами дешифратора 6. Выход 9 ц счетчика .5 соеди нен с установочными входами счетчик 2 и распределителя 3. Выходные шины о( , /3j, ,oi , б третьего распределителя 1 соединены с входами третьего счетчика 7 Джонсона,

Выхода R и S преобразователя 4 и дешифратора 6 соединень с первым и

вторым входами блока 8 совпадения, выход Р которого соединен с вторым входом коммутатора 9, первый вход

20

-г f itdit

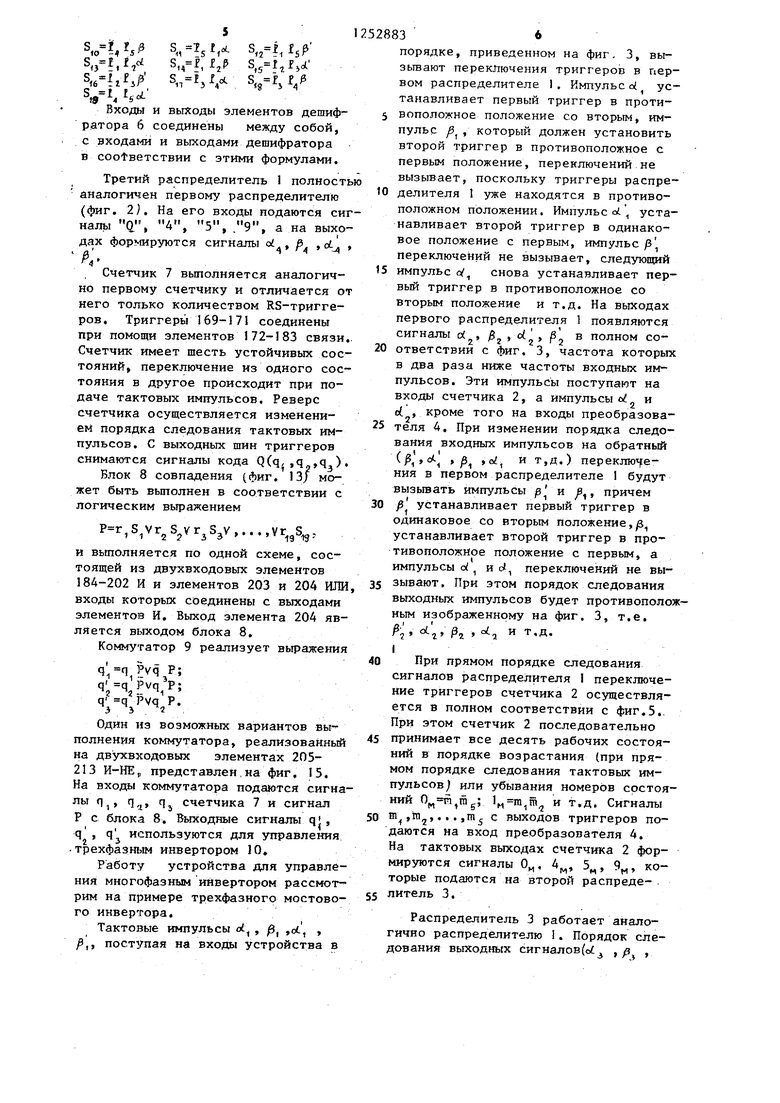

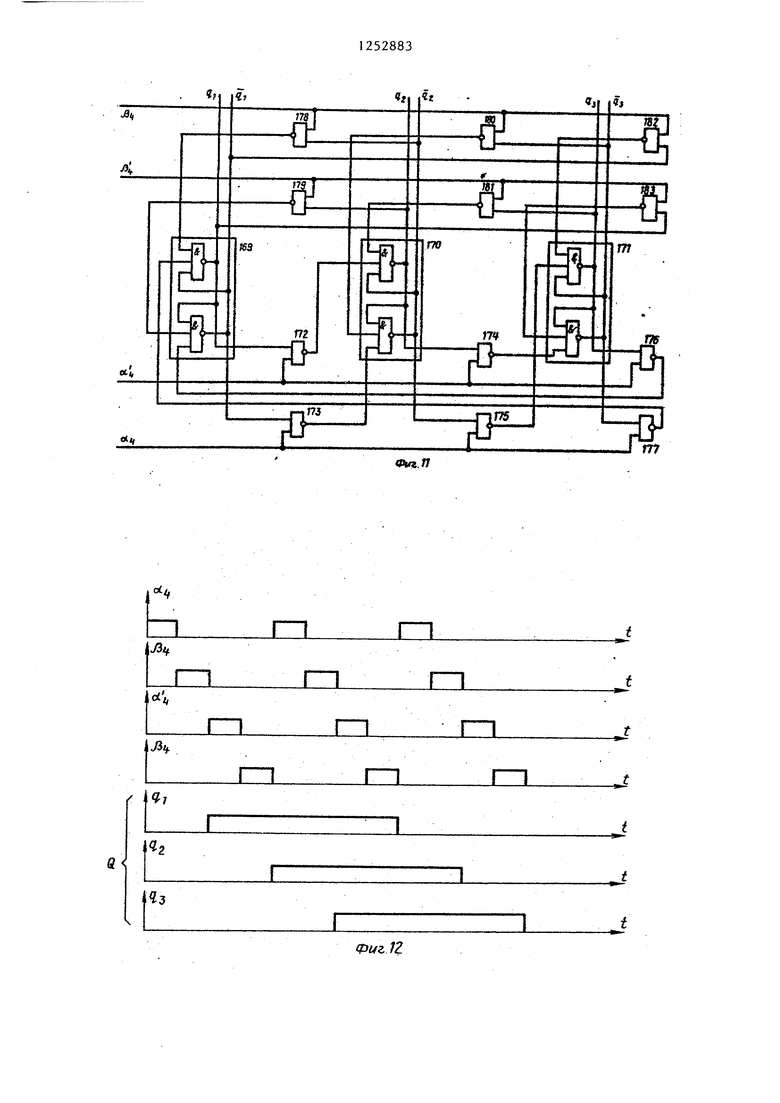

этих распределителей; на фиг. 4 - принципиальная схема первого счетчика Джонсона; на фиг. 5 - диаграммы его входных сигналов f. 2 9J, выходных сигналов m .mj,... П1. и выходные сигналы преобразователя кода; на фиг. 6 - принципиальная схема преобразователя кода; на .фиг.7- принципиальная схема второго счетчика Джонсона; на фиг. 8 - диаграммы его входных сигналов з , Р, Pj выходных сигналов f,,f,...,, а также выходных сигналов S дешифратора i на фиг. 9 - принципиальная схема второго распределителя импульсов, 35 ключи 12, 14, 16. на фиг. 10 - принципиальная схема де- Распределители 1 (фиг. 2) предкоторого соединен с выходом Q счетчика 7, а выходы q , q . q связаны 30 с силовыми ключами трехфазного мостового инвертора 10, содержащего силовые ключи 11-16, Сигналы q, q j, q j подаются на ключи П, 13, 15, а инверсные сигналы q , q , q

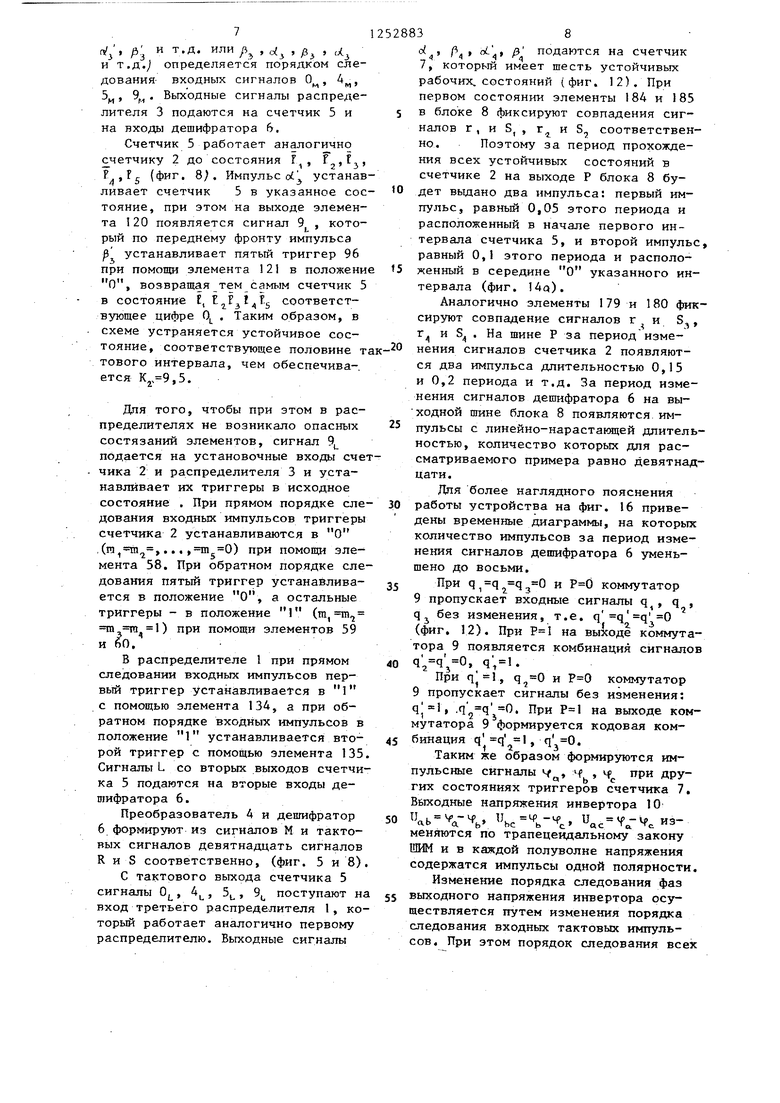

шифратора; на фиг. 11 - принципиальная схема третьего счетчика Джонсона; на фиг. 12 - диаграммы его входных счетчиков о . « 4 выходных сигналов q, q Ч на фиг. 13 - принципиальная схема блока совпадения; на 4мг, 14 - диаграммы вькоднь1х сигналов Р блока совпадения и выходные сигналы Г.,,.,. ,1 второго счетчика Джонсона; на фиг. 15 - принципиальная схема коммутатора; на фиг. 16 - времен1я 1е диаграмъв) выход- ньпс сигналов коммутатора . совпадаюшх по форме е потенциалами V Ч точек А , Ь ,с с мостового инвертора и выходных напряжений U, Uf, Up для первого варианта блока совпадения.

, Тактовые входы устройства oL , f, , с,, , соединены с входами первого четырехтактного распределителя 1 импульсов, выход которого cij ,j

Ш

252883

р соединены с первыми входами первого счетчика 2 Джонсона. Тактовые выходы 0|, 4, 5, 9„ счетчика 2 соединены с тактовыми входами второго

5 распределителя 3 импульсов, а выходы счетчика 2 и входыot, иы соединены с входами преобразователя 4 кодов. Выходы 0 , , oil, , f, распределителя 3 соединены с входами второго счетчика 5 Джонсона и входами., дешифратора 6. Тактовые выходы 0, и L) L второго счетчика 5 соединены с входами третьего распреде . лителя 1, полностью аналогичного пер 5 вому распределителю 1, а входы счетчика 5 соединены со входами дешифратора 6. Выход 9 ц счетчика .5 соединен с установочными входами счетчика 2 и распределителя 3. Выходные шины о( , /3j, ,oi , б третьего распределителя 1 соединены с входами третьего счетчика 7 Джонсона,

Выхода R и S преобразователя 4 и дешифратора 6 соединень с первым и

вторым входами блока 8 совпадения, выход Р которого соединен с вторым входом коммутатора 9, первый вход

20

- в, 35 ключи 12, 14, 16. - Распределители 1 (фиг. 2) пред35 ключи 12, 14, 16. Распределители 1 (фиг. 2) предкоторого соединен с выходом Q счетчика 7, а выходы q , q . q связаны 30 с силовыми ключами трехфазного мостового инвертора 10, содержащего силовые ключи 11-16, Сигналы q, q j, q j подаются на ключи П, 13, 15, а инверсные сигналы q , q , q ,

ставляют собой реверсивную схему, которая может быть выполнена, например, на двух RS-триггерах, сос40 тоящих из трехходовых элементов 17, 18 и 9, 20. Триггеры связаны между собой элементами 21-28 И- НЕ, один вход которых соединен с одним из тактовых входов, а второй

4S вход соединен с одним из выходов триггера. Выходные сигналы распределителя 1 формируются элементами 29-32 И, выходы которых соединены с соответствующими выходами RS-триг5огерьв, в соответствии с формулами

.q,q,; ,i,q,; . „,

)

Счетчик 2 (фиг. 4) вьтолнен по 55 схеме счетчика на десять устойчивых состояний, например, на RS -триггерах 33-37, связанных между собой элементами 38-57 Й-НЕ. Входы элемен-тов 38, 40, 42, 44, 46 соединены с входом Ы,, входы вентилей 49, 51, 53, 55, 57 соединены ее входом р , входы элементов 39, 41, 43, 45, 47 соединены со входом о , а входы элементов 48, 50, 52, 54, 56 - со входом 2 Выходы элементов Й-НЕ соединены со входами триггеров, каждый из которых имеет по три R и S входа. Два трехвходовых элемента 58 и 59 И-НЕ, выходы которых соединены со входами элемента 60 ИЛИ, устанавливают пятьй триггер в положение О, когда на установочном входе 9 , которьй соединен с первыми входами элементов 58 и 59, имеется сигнал высокого уровня. Выход элемента 60 соединен с одним из входов триггера 37. С выходных шин триггеров снимаются выходные сигналы счетчика 2 (т , га, ...,т5). Тактовые сигналы, которые подаются на вход второго распределителя 3, формируются двухвходовыми элементами 61-64 И в соответствии с выракения- , ми

,т5; .

Преобразователь 4 (фиг. 6) представляет собой логический блок, который из сигналов М и тактовых импульсов ol. и формирует сигналы вспомогательного кода

r,m5vm,ci r,,m,Vraj Tj n,mjVtn m5 i r,,vmjWdra

r in IfljCL i l Ъ

г; ™

,

r т, ,. 5

r «mjmjVtn msii. . .

8,5

,

rg m injvm5cir m vtn.Vct.

Преобразователь 4 может быть выполнен на двухвходовых элементах 65-68 И, элементах 69-72 ИЛИ, элементах 73-82 И и элементах 83- 91 ИЛИ. Сигнал г формируется элементом 73, г,, - элементом 65, г - элементами 65, 66, 74, 83, сигнал г, формируется элементом 66, г - элементами 66, 67, 75, 84. Сигнал Tg образуется на выходе элемента 67 сигнал г формируется элементами 67 68, 76, 85. В формировании сигнала Tj участвует элемент 68, Гд - элементы 68, 77, 86, а г,о снимается с

пятого инверсного выхода счетчика 2, Сигнал г,, формируется элементами i69, 78, 87, r,j - элементом 69, г, - элементами 69, 70, 79, 89, а г - эле- ментом 70. Сигнал г,5 формируется элементами 70, 71, 80, 89, сигнал - элементом 71 , сигнал г, - элементами 71, 72, 81, 90, сигнал элементом 72, а сигнал г - элементами 72, 82, 91.

Счетчик (фиг. 7) состоит из пяти RS-триггеров 92-96, соединенных элементами 97-116 связи. Соединения. триггеров и элементов связи осуществляются таким же образом, как в счетчике 2. Тактовые сигналы О , и и 9 ,которые подаются на входы третьего распределителя 1, формируются элементами 117-120 И. Кроме

того, счетчик 5 содержит элемент 12 И-НЕ, входы которого соединены со входом р и выходом элемента 120, а выход соединен с R-входом пятого триггера. На выходах триггеров формируется код L (I, , f ,..., 1) .

Распределитель 3 (фиг. 9) отличается от распределителя 1 тем, что на его входы вместо импульсов ы, , t i р подаются сигналы 0„, 4„,

5„ , 9„ со счетчика 2 соответственно. Кроме того, распределитель 3 имеет установочный вход, на который подается сигнал 9 со второго счетчика 5. Распределитель 3 состоит из

RS-триггеров на элементах 122-125 И- НЕ, соединенных элементами 126-129, 130-133 связи, входы и выходы которых соединены так же, как элементы 21-24, 25-28 распределителя 1. Вход

9 соединен с первыми входами элементов 134 и 135, вторые входы которых соединены с входами 5„ и 9 соответственно. Выходы элементов 134 и 135 соединены с S-входами

первого и второго триггеров. Выход ные сигналы о(, of распределителя 3 формируются элементами 136-139 И.

Дешифратор 6 (фиг. 10) представ- ляет собой комбинационную логическую схему, состоящую из двухвходовых элементов 140-168 И, которая формирует сигналы S из сигналов L и тактовых импульсов в соответствии с формулами

S,I, l5 2, sP 5,Г, ,l,ot S,-fJ,p Sr,V S, S,rj,o

V.53 S,,l5f, Vl.fsP

VI,f,c S,, f, JE,f S,,

S,.X S,, -f4

Входы и выходы элементов дешифратора 6 соединены между собой, с входами и выходами дешифратора в cootвeтcтвии с этими формулами.

Третий распределитель 1 полностью аналогичен первому распределителю (фиг. 2), На его входы подаются сигналь а, 4, 5, .9, а на выходах формируются сигналы of Я. ot

4

Счетчик 7 выполняется аналогично первому счетчику и отличается от него только количеством RS-тригге- ров. Триггеры 69-171 соединены при помощи элементов 172-183 связи. Счетчик имеет шесть устойчивых состояний, переключение из одного состояния в другое происходит при подаче тактовых импульсов. Реверс счетчика осуществляется изменением порядка следования тактовых импульсов. С выходных шин триггеров снимаются сигналы кода Q(q/,q-,q,).

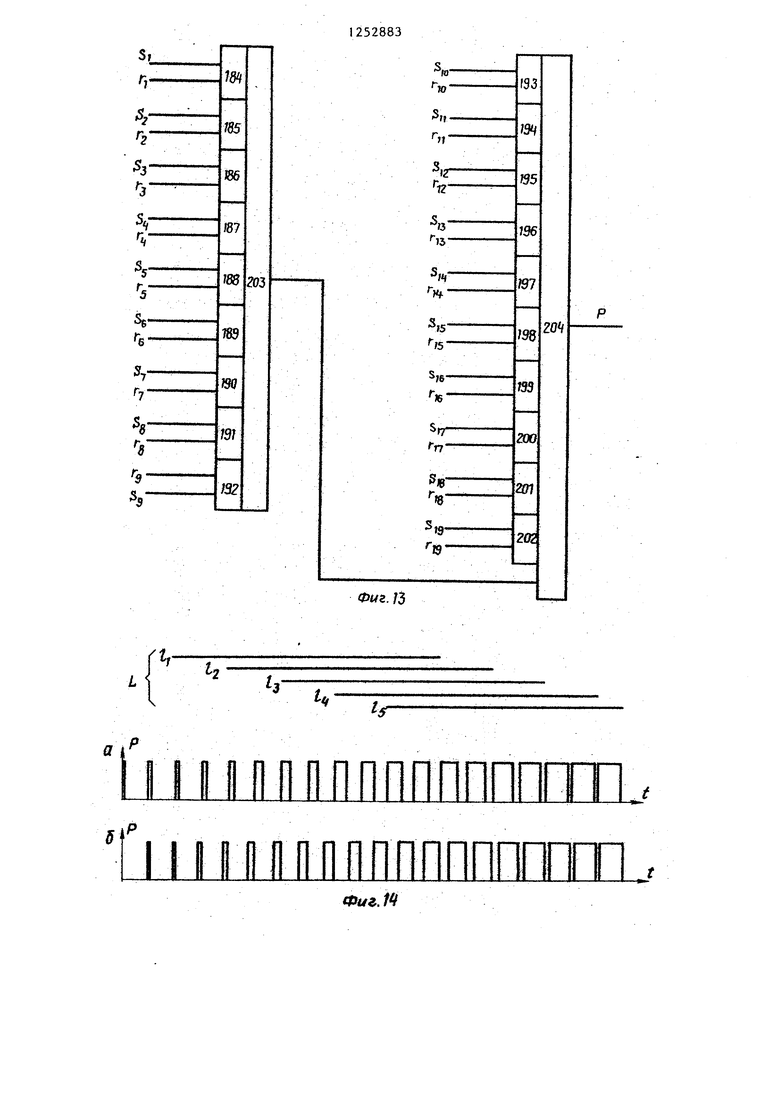

Блок 8 совпадения (фиг. 13/ может быть выполнен в соответствии с логическим вьфахением

,s,,v,....vr,s,3.

и выполняется по одной схеме, состоящей из двухвходовых элементов 18Д-202 И и элементов 203 и 204 ИЛИ, входы которых соединены с выходами элементов И. Выход элемента 204 является выходом блока 8.

Коммутатор 9 реализует выражения

q q i vq P.

Один из возможных вариантов вы- полнения коммутатора, реализованный на двухвходовых элементах 205- 213 И-НЕ„ представлен,на фиг, 15. На входы коммутатора подаются сигна- ль1 q , q,j, q счетчика 7 и сигнал Р с блока 8. Выходные сигналы qj, q , q используются для управления трехфазш.1М инвертором 10,

Работу устройства для управления многофазным инвертором рассмотрим на примере трехфазного мостового инвертора.

Тактовые импульсы od, , , ,ot , , ,, поступая на входы устройства в

125

1252883

порядке, приведенном на фиг. 3, вы- зьшают переключения триггеров в первом распределителе 1. ИмпульсЫ устанавливает первый триггер в противоположное положение со вторым, импульс Д, который должен установить второй триггер в противоположное с первым положение, переключений не вызывает, поскольку триггеры распределителя 1 уже находятся в противоположном положении. Импульс ot устанавливает второй триггер в одинаковое положение с первым, импульс р переключений не вызывает, следующий

импульс о( снова устанавливает первый триггер в противоположное со вторым положение и т.д. На выходах первого распределителя 1 появляются сигналы d. , yS 2 ® полном соответствии с фиг. 3, частота которых в два раза ниже частоты входных импульсов. Эти импульсы поступают на входы счетчика 2, а импульсы о и ot , кроме того на входы преобразователя 4. Прн изменении порядка следования входных импульсов на обратный (, jo - ,р ,0, и т,д.) переклю е- ния в первом распределителе 1 будут вызьшать импульсы и д, причем

устанавливает первый триггер в одинаковое со вторым положение,, устанавливает второй триггер в противоположное положение с первым, а импульсы d и Ы, переключений не вызывают. При этом порядок следования выходных импульсов будет противополож- ньт изображенному на фиг. 3, т.е.

2 г Рч ДI

При прямом порядке следования

сигналов распределителя 1 переключение триггеров счетчика 2 осуществляется в полном соответствии с фиг,5. При этом счетчик 2 последовательно

принимает все десять рабочих состояний в порядке возрастания (при прямом порядке следования тактовых импульсов или убывания номеров состояний , и т,д. Сигналы

т ,т,,. .. ,т с выходов триггеров подаются на вход преобразователя 4. На тактовых выходах счетчика 2 формируются сигналы 0„. 4, 5„, 9, которые подаются на второй распределитель 3.

Распределитель 3 работает аналогично распределителю 1. Порядок следования выходных сигналов(о , р ,

з P и т.д, определяется порядком следования- входных сигналов 0, 4, 5 , 9,, . Выходные сигналы распределителя 3 подаются на счетчик 5 и на входы дешифратора 5.

Счетчик 5 работает аналогично четчику 2 до состояния Г, Рд з Р , fj (фиг. 8. Импульсы устанавливает счетчик 5 в указанное сое- тояние, при этом на выходе элемента 120 появляется сигнал 9, который по переднему фронту импульса р устанавливает пятьй триггер 96 при помощи элемента 121 в положение О, возвращая тем самым счетчик 5 в состояние , соответствующее цифре 0 . Таким образом, в схеме устраняется устойчивое состояние, соответствующее половине та тового интервала, чем обеспечива-. ется К.9,5.

Для того, чтобы при этом в распределителях не возникало опасных состязаний элементов, сигнал подается на установочные входы счетчика 2 и распределителя 3 и устанавливает их триггеры в исходное состояние . При прямом порядке еле- дования входных импульсов триггеры счетчика 2 устанавливаются в О ,(.. t ,) при помощи эле- мента 58. При обратном порядке следования пятый триггер устанавлива- ется в положение О, а остальные триггеры - в положение 1 (т,т, т га 1) при помощи элементов 59 и 60.

В распределителе 1 при прямом следовании входных импульсов первый триггер устанавливается в 1 с помощью элемента 134, а при обратном порядке входных импульсов в положение 1 устанавливается вто- рой триггер с помощью элемента 135 Сигналы L со вторых выходов счетчика 5 подаются на вторые входы дешифратора 6.

Преобразователь 4 и дешифратор 6 формируют из сигналов М и тактовых сигналов девятнадцать сигналов R и S соответственно, (фиг. 5 и 8).

С тактового выхода счетчика 5 сигналы Oj, 4, 5j, 9 поступают на вход третьего распределителя 1, который работает аналогично первому распределителю. Выходные сигналы

5

О15 к-

25 ЗО

40 5 50

jj dL

У .

8 подаются на счетчик

7 который имЪет шесть устойчивых рабочих, состояний { фиг. 12). При первом состоянии элементы 184 и 185 в блоке 8 фиксируют совпадения сигналов г, и S, , г и S, соответственно. Поэтому за период прохождения всех устойчивых состояний в счетчике 2 на выходе Р блока 8 будет выдано два импульса: первый импульс, равный 0,05 этого периода и расположенный в начале первого интервала счетчика 5, и второй импульс, равный 0,1 этого периода и расположенный в середине О указанного интервала (фиг. 4а).

Аналогично элементы I79 и 180 фиксируют совпадение сигналов г и S, г и S . На щине Р за период изменения сигналов счетчика 2 появляются два импульса длительностью 0,15 и 0,2 периода и т.д. За период изменения сигналов дешифратора 6 на вы- ходной шине блока 8 появляются импульсы с линейно-нарастанщей длительностью, количество которых для рассматриваемого примера равно девятнадцати.

Для более наглядного пояснения работы устройства на фиг. 16 приведены временные диаграммы, на которых количество импульсов за период изменения сигналов дешифратора 6 уменьшено до восьми.

При q , q q .0 и коммутатор 9 пропускает входные сигналы q,, q , q без изменения, т.е. (фиг. 12). При на выходе коммутатора 9 появляется комбинация сигналов

. q t iПри q -, и коммутатор 9 пропускает сигналы без изменения: , ., При на выходе коммутатора 9 формируется кодовая комбинация q q 1, q ,0.

Таким же образом формируются импульсные сигналы / , ч ,4 ггри других состояниях триггеров счетчика 7. Выходные напряжения инвертора 10

аЬ V ьс ь ас 3меняются по трапецеидальному закону ШИМ и в каждой полуволне напряжения содержатся импульсы одной полярности.

Изменение порядка следования фаз выходного напряжения инвертора осуществляется путем изменения порядка следования входных тактовых импульсов. При этом порядок следования всех

тактовых сигналов изменяется на противоположный и работа устройства может быгь проиллюстрирована теми же времен1г1ыми диаграммами (фиг. 16), если с момента реверса рассматривать движение импульсов в направлении обратном обозначенному на фиг. 16 (спрва налево).

Таким образом, устройство обеспечивает возможность изменения порядка следования фаз вьжодного напряжения и существенно повьшает качество выходного напряжения за счет увеличени количества импульсов I filM в каждой полуволне. Это достигается без уве- лИчения аппаратурных затрат путем использования для формирования импульсов ШИМ цифровых сигналов с распределителей , соединяющих между собой счетчики. При этом сохраняется полная си метрня выходного напряжения инвертора

Формула изобретения

Устройство для управления т-фаз- ным инвертором, содержащее три счетчика Дконсона, коэффициент счета первого из которых , второго - ,5, третьего - , выходы третьего счетчика Джонсона соединены через коммутатор с выходом устройства, управляющий вход коммутатора подключен к выходу блока совпадения , отличающееся тем, что, с целью улучшения качества выходного напрягжения и обеспечения возможности реверса фаз, оно снабжено тремя четырехтактными ревер СИВНЫМ1; распределителями импульсов, дешифратором и преобразователем кодов, счетчики Джонсона выполнены че- тьфехтактными и реверсивньми, а первый и второй счетчики Джонсона снабжены четырьмя тактовыми выходами, причем выводы для подключения так«f

товых сигналов че.рез первый четырехтактный реверсивный распределитель импульсов соединены с тактовыми входами первого счетчика Джонсона, первый и третий тактовый выходы которого и его выходы соединены с входами преобразователя кодов, структура которого описывается

сигналов г -г

-1 19

выражениями

0

5 0

5

0

г, ni,ni,-ot

raj

г га, mjVTn,nj ot

4 г, .

е э™5 , r mjm5Vi4 m..oL

rgHn tnsVmgOi. г m

10 5

где ra,raj,m,,

r,,mjVm,ct r,

r,,m,vm5Vm of. r,,

r,5 in2Vm,vm3oi r,m3Vffig

r,m vm5vm oi

r,

rg m Vm5Vot

выходные сигналы счетчика Джонсона, сигналы на его первом и третьем тактовых входах,

тактовые выходы первого счетчика Джонсона через второй четырехтактный реверсивный распределитель импульсов соединены с тактовь ми входами второго счетчика Джонсона, тактовые входы и выходы которого соединены с входами дешифратора, тактовые выходы второго счетчика Джонсона соединены через третий четырехтактный реверсивный распределитель импульсов с тактовыми входами третьего счетчика Джонсона, четвертый тактовый выход второго счетчика Джонсона подключен к установочным входам первого счетчика Джонсона и второго четырехтактного реверсивного распределителя импульсов, а выходы преобразователя кодов и дешифратора соединены с входами блока совпадения.

«MJT

Л;

л;

M

Л

J

I-Ir U

DJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления инвертором | 1987 |

|

SU1617584A1 |

| Устройство для управления трехфазным транзисторным инвертором | 1985 |

|

SU1288867A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Широтно-импульсный модулятор | 1989 |

|

SU1677857A1 |

| Устройство для управления трехфазным инвертором | 1987 |

|

SU1559387A1 |

| Селектор импульсов заданной кодовой комбинации | 1987 |

|

SU1457169A1 |

| Делитель частоты следования импульсов с программным управлением | 1982 |

|

SU1027831A1 |

| Частотный манипулятор | 1980 |

|

SU873450A1 |

| Устройство для измерения непрерывных физических величин | 1980 |

|

SU875213A1 |

| Распределитель тактовых импульсов | 1986 |

|

SU1411966A1 |

Изобретение относится к преобразовательной технике и может быть использовано в системах электропитания и электропривода. Цель изобретения - улучшение качества выходного напряжения и обеспечение возможности реверса фаз. Устр-во содержит трн счетчика Джонсона (СЛ). Коэф. счета первого СЛ2 равен К,10, второго СЛ5 - ,5 и третьего СД7 - , где m - количество фаз инвертора 10. Устр-во содержит также Коммутатор 9 и блок 8 совпадения. Улучшение качества выходного напряжения обеспечивается введением трех четырехтактных реверсивных распределителей импульсов (два одинаковых 1 и 3), де111ифратора 6, преобразователя 4 кодов. Устр-во обеспечивает возможность изменения порядка следования фаз выходного напряжения, чем существенно повьшается качество выходного напряжения за счет увеличения количества импульсов ЕИМ в каждой полуволне. Это достигается путем использования цифровых сигналов с распределителей импульсов, соединяющих между собой счетчики. При этом сохраняется полная симметрия выходного капр5гжения инвертора, обеспечиваяяцая возможность реверса фаз, 16 ил.

9n

л

ФигВ

0

J

hi

rn

l

И.

tl

ГПmmr i

.-Si

:JL

fi

Si

rn

n

m m .f

ГТrn f

-2, .Ja.

-Sn

.5u.

-«a

1 tf.

Фиг, 11

ФигМ

e%lR6

b.«i|

iinfiim

% %

f

UJUUfl

тми

iriiillL

J

I

имшл

иювоиц.

«Mt

lyiOilll

Составитель В.Миронов Редактор П.Коссей Техред Л.Сердюкова Корректор Е.Сирохман

Заказ 4628/54 Тираж 631Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Авторское свидетельство СССР 532J63, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления многофазным инвертором | 1978 |

|

SU955837A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-08-23—Публикация

1983-03-01—Подача