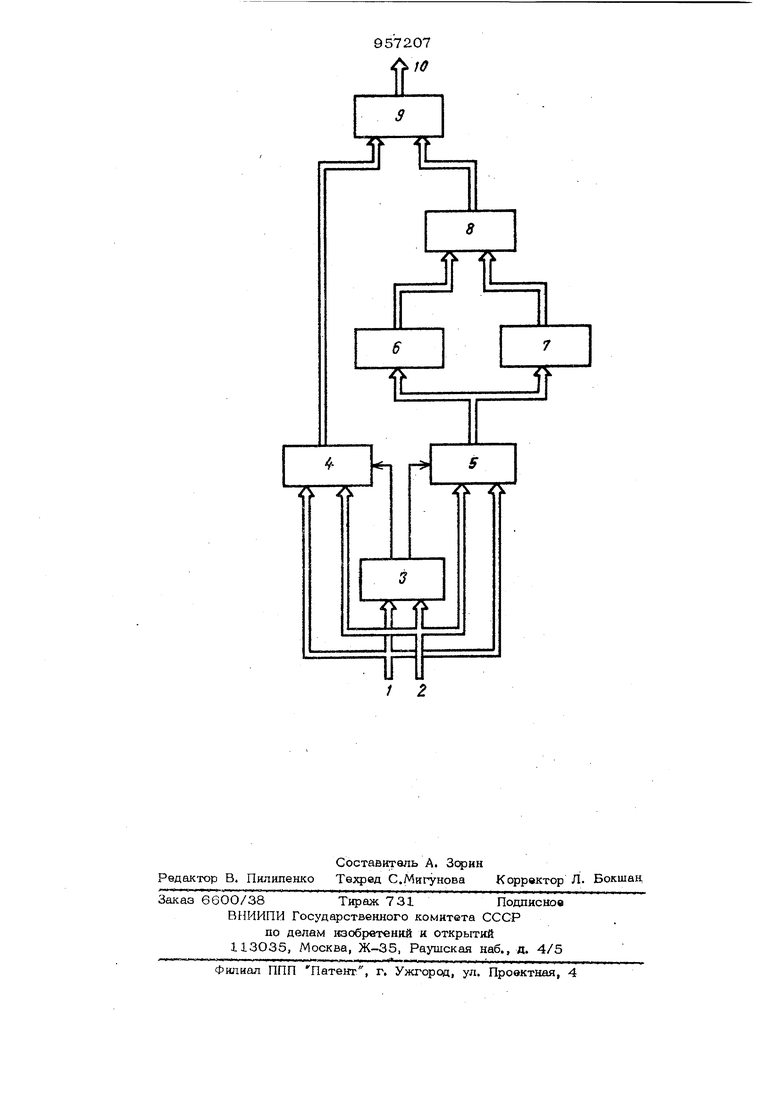

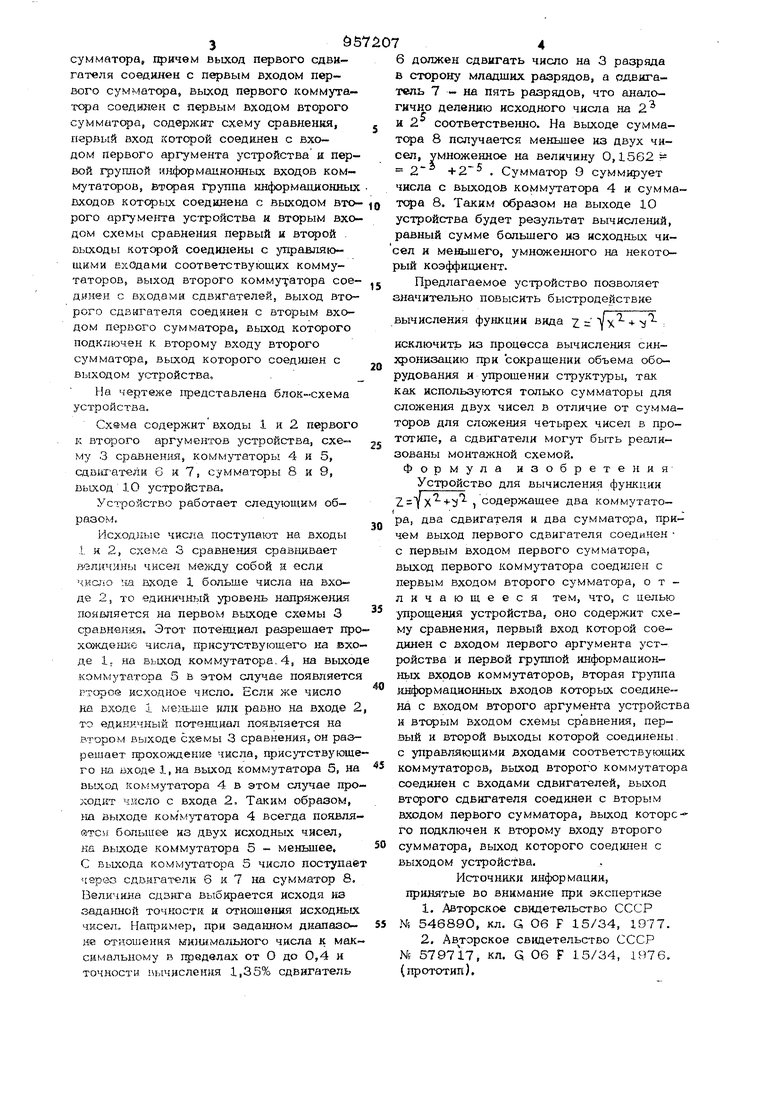

сумматора, хфичем выход первого сдвиготеля соединен с первым входом первого сумматора, выход первого коммутатора соединен с первым входом второго сум матера, содерл 1гг схему сравнения, первый вход которой соединен с входом первого аргумента устройства н первой группой информационных входов коммутаторов, Вторая группа информационных входов котсрых соединена с выходом второго аргумента устройства и вторым вхоДОМ схемы сравнения первый и аькоды которой соединены с управляющими входами соответствующих коммутаторов, выход второго коммутатора сое динен с входами сдвягателей, выход второго сдвнгателя соединен с вторым входом первого сумматора, выход которого подключен к второму входу второго сумматора, выход которого соединен с выходом устройства. На чертеже представлена блок-схема устройства. Схема содержит входы 1 н 2 первого к второго аргументов устройства, схему 3 сравнения, коммутаторы 4 и 5, сдв);1аг-ателн о и 7, сумматоры 8 и 9, Выход 1О устройства. Устройство работает следующим образом, Исходные Числа поступаю на входы 1 н 2, схема 3 сравнения сравг-швает эличинь чисел между собой я если -iKCJiO на входе 1 больше числа на входе 2, то единичный уровень напряжения появляется на первом выходе схемы 3 сравнения. Этот потенциал разрешает пр хождение числа, присутствующего на вхо де 1. на выход коммутатора, 4, на выхо коммутатора 5 В этом случае появляетс рторое исходное число. Если же число на входе 1 меыьше или равно на входе то единичный потенциал появляет-ся на втором выходе схемы 3 сравнения, он раз решает грохожденке числа, присутствукэщ го ш входе, на выход коммутатора 5, на Выход коммутатора 4 в этом случае про ход1гг число с входа 2. Таким образом, на выходе коммз.татора 4 всегда появля e-TCii большее из двух исходных чисел, на выходе коммутатора 5 - меньшее, С выхода коммутатора 5 число поступае через сдвнгателк 6 к 7 на сумматор 8, Величина сдвига выбирается исходя на заданной точности и отноше1шя исходных чисел, Нащзимер, при заданном днапаво не отношения ии1шмального числа к мак симальному в пределах от О до 0,4 и точности вычисления 1,35% сдвигатель 6 должен сдвигать число на 3 разряда в сторону младших разрядов, а одвигатель 7 - на пять разрядов, что аналогично делению исходного числа на 2 и 2 соответственно. На выходе сумматора 8 получается меньшее из двух чисел, умноженное на величину 0,1562 2 +2 . Сумматор 9 суммирует числа с выходов коммутатора 4 и сумматс а 8, Таким образом на выходе 10 устройства будет результат вычислений, равный сумме большего из исходных чиел и меньшего, умноженного на некоторый коэффициент. Предлагаемое устройство позволяет значительно повысить быстродействие вычисления функции вида Vx у исключить из процесса вычисления синхронизацию при сокращении объема оборудования и упрощении структуры, так как используются только сумматоры для сложения двух чисел в отличие от сумматоров для сложения четырех чисел в прототипе, а сдвигатели могут быть реализованы монтажной схемой. Формула изобретения Устройство для вычисления функции ) содержащее два коммутато- f pa, два сдвигателя и два сумматора, причем выход первого сдвигателя соединен с первым входом первого сумматора, выход первого коммутатора соедк11ен с первым входом второго сумматора, отличающееся тем, что, с целью упрощения устройства, оно содержит схему сравнения, первый вход которой соединен с входом первого аргумента устройства и первой группой информационных входов коммутаторов, вторая группа информационных входов которых соединена с входом второго аргумента устройства н втярым входом схемы сравнения, первый и второй выходы которой соединены с управляющими входами соответствующих коммутаторов, выход второго коммутатора соединен с входами сдвигателей, выход второго сдвигателя соединен с вторым входом первого сумматора, выход которсго подключен к второму входу второго сумматора, выход которого соединен с выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Ni 546890, кл. G Об F 15/34, 1977. 2,Ав -орское свидетельство СССР № 57.9717, кл, Q 06 F 15/34, 1976. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ = @ | 1981 |

|

SU1010621A2 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

Авторы

Даты

1982-09-07—Публикация

1980-12-04—Подача