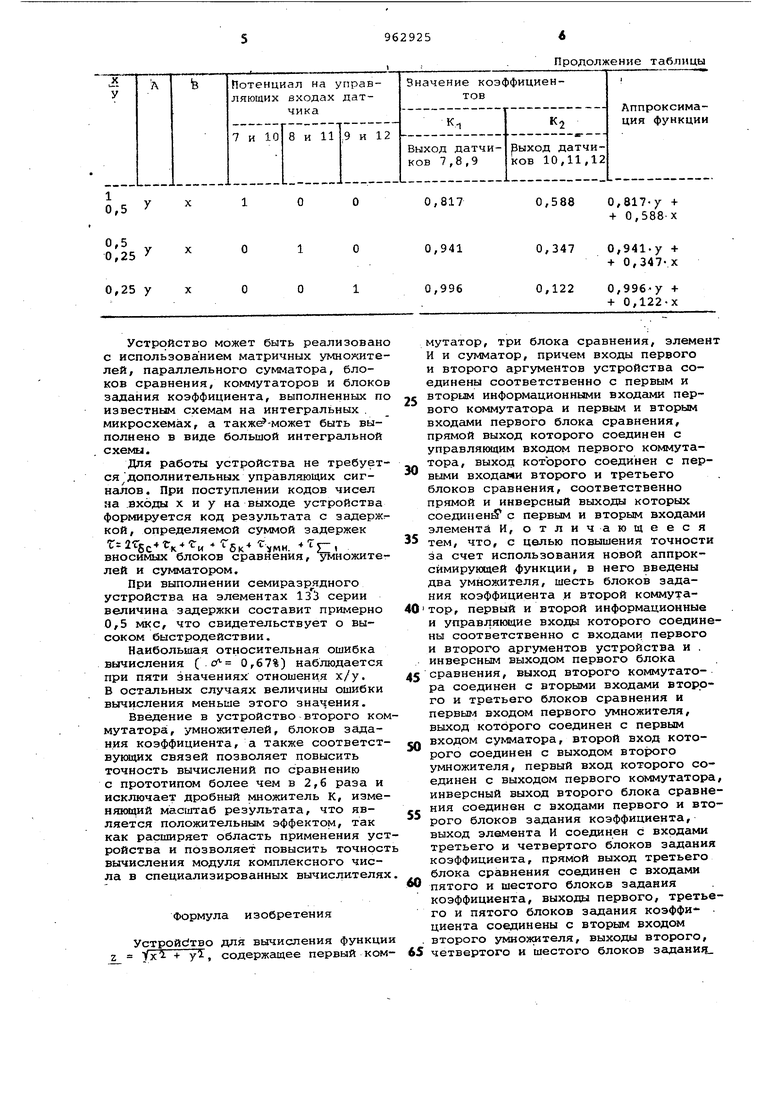

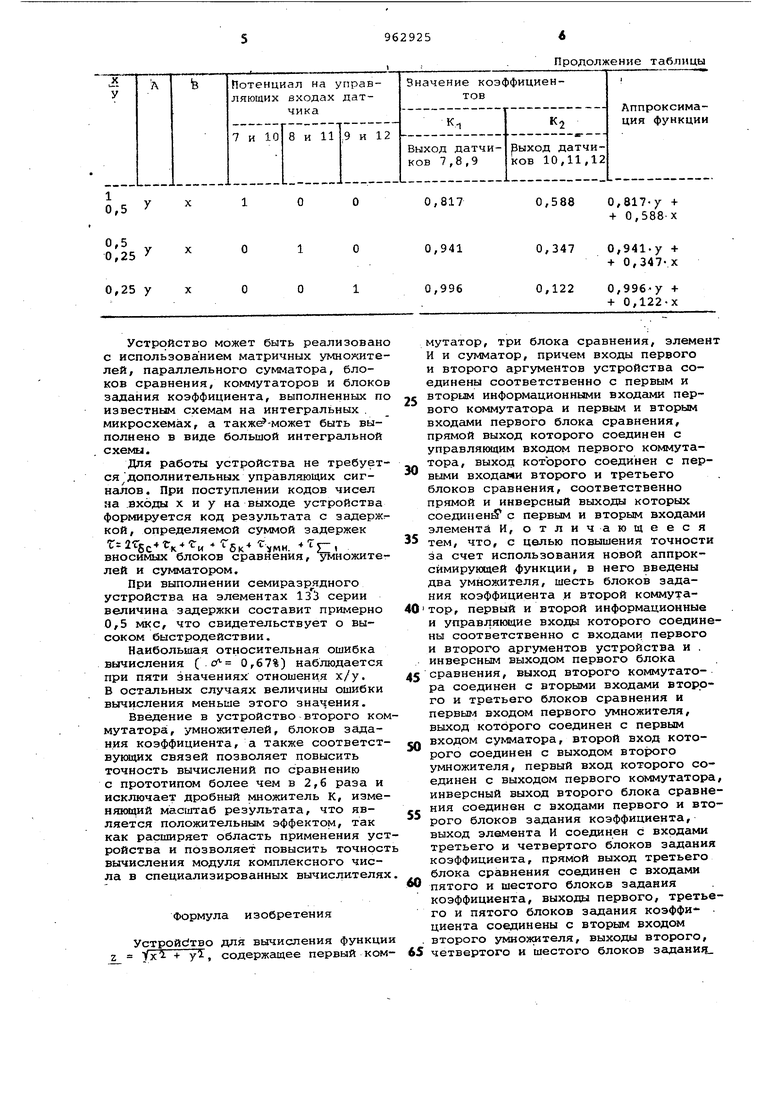

и второй коммутатор, первый и второй информацгонные и управляющие входы которого соединены соответственно с входс1ми первого и второго аргументов устройства и инверсным выходом первого блока сравнения, выход второ го коммутатора соединен с вторыми входами второго и третьего блоков сравнения и первым входом первого умножителя, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом второго умножителя, первый вход которого соединен с выходом первого коммутатора, инверсный выход второго блока сравнения соединен с входами первого и второго блоков задания коэффициента, выход элемента И соединен с входами третьего и четвертого блоков задания коэффициента, прямой выход третьего блока сравнения соединен с входами пятого и шестого блоков задания коэффициента, выходы первого, третьего и,пятого блоков задания, коэффициента соединены с вторьм входом второго умножителя, выходывторого, четвертого и шестого блоков задания коэффициента соединены с вторым входом первого умножителя. На чертеже представлена блок-схема устройства. Устройство для вычисления функции 2 Vx J « у содержит блок 1 сравнения, ко1«1мутаторы 2 и 3/ блоки 4 и 5 сравнения, элемент И 6, блоки 7-12 задания коэффициента, умножители 13 и 14 и сумматор 15. Конструктивно блоки 7-12 задания коэффициента могут быть вьтолнены в, виде шифраторов или регистров. Работа устройства основана на аппроксимации функции следующим выражением. .Z г , если х у (1) Z а К.,у К,у , если х у (2) Для повышения точности аппроксимации коэффициенты К и К изменяют свои величины в зависимости от величины отношения х/у Су/х) и принимают по три фиксированных значения. Связь между величинами коэффициентов и отношений х/у приведена в таблице (столбцы 7, 8 и 1). В столбце . 9 этой таблицы приведены аппроксимирующие выражения для каждого полуинтервала значений отношения х/у. Алгоритм (1) и (2) реализуется устройством следующим образом. Блок 1 сравнения величин х и у управляет работой коммутаторов 2 и 3 таким образом, что код,величины А на выходе коммутатора 2 всегда больше кода величины В на выходе коммутатора 3 (таблица, столбцы 2 и 3) . Тем самым-реализуется выбор выражеНИИ (1) или (2). Блоки 4 и 5 сравнения срабатывают соответственно при выполнении условий и формируют совместно с элементом. И 6 три сигнала управления (таблица, столбцы 4-6) блоками 7-12 задания коэффициента, причем каждый сигнал включает пару датчиков кода К и Kj,, которые формируют двоичные коды коэффициентов в соответствии с таблицей (в столбцах 7 и 8 приведены десятичные эквиваленты этих коэффициентов) . В каждой группе (7-9 и 10-12) включен только один блок формирования коэффициента и код, формируемый этим датчиком, поступает на соответствующий умножитель. При этом на выходе умнЬ ителя 13 формируется произведение К:,-А, а на выходе умножителя 14 произведение K,j- В. Эти произведения суммируются сумматором 15 , на выходе которого формируется двоичный код -результата вычисления функции fx у1 по аппроксимирующим выражениям, приведенным в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ ВЕКТОРА | 1991 |

|

RU2022340C1 |

| Устройство для вычисления функции арктангенса | 1985 |

|

SU1273920A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Устройство для вычисления функций @ и @ | 1980 |

|

SU978146A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1136155A1 |

X у

X у

X у

0,122 0,996-х +

0,996 + 0,122-у

0,941.x +

0,347 + 0,347-у

0,817.x +

0,588 + 0,588- у

Устройство может быть реализовано с использованием матричных умножителей, параллельного сумматора, блоков сравнения, коммутаторов и блоков Зсщания коэффициента, выполненных по известным схемам на интегральных . микросхемах, а также -может быть выполнено в виде большой интегральной схемы.

Для работы устройства не требуется дополнительных управл5нощих сигналов. При поступлении кодов чисел на .входы X и у на выходе устройства формируется код результата с згщержкой, определяемой суммой задержек

бк .

вносимых блоков сравнения, умножите;ия, уми лей и сумматором.

При выполнении семиразр ядного устройства на элементах серии величина задержки составит примерно 0,5 МКС, что свидетельствует о высоком быстродействии.

Наибольшая относительная ошибка вычисления (, сЛ 0,67%) наблюдается при пяти значениях отношения х/у. В остальных случаях величины ошибки вычисления меньше этого значения.

Введение в устройство второго коммутатора, умножителей, блоков задания коэффициента, а также соответствукмдих связей позволяет повысить точность вычислений по сравнению с прототипом более чем в 2,6 раза и исключает дробный множитель К, изменяющий масштаб результата, что является положительным эффектом, так как расширяет область применения устройства и позволяет повысить точност вычисления модуля комплексного числа в специализированных вычислителях

Формула изобретения

Устроййтво для вычисления функции Yxi + у1, содержащее первый комПродолжение таблицы

мутатор, три блока сравнения, элемент И и сумматор, причем входы первого и второго аргументов устройства соединены соответственно с первым и вторым информационными входс1ми пер5вого коммутатора и первым и вторым входами первого блока сравнения, прямой выход которого соединен с управляющим входом первого коммутатора, выход которого соединен с пер0выми входами второго и третьего блоков сравнения, соответственно прямой и инверсный выходы которых соединен с первым и вторым входами элемента И, отличающееся

5 тем, что, с целью повышения точности за счет использования новой аппроксимирующей функции, в него введены два умножителя, шесть блоков задания коэффициента и второй коммута0тор, первый и второй информационные и управляющие входы которого соединены соответственно с входами первого и второго аргументов устройства и . инверсным выходом первого блока сравнения, выход второго коммутато5ра соединен с вторыми входс1МИ второго и третьего блоков сравнения и первыгл входом первого умножителя, выход которого соединен с первым входом сумматора, второй вход кото0рого соединен с выходом второго умножителя, первый вход которого соединен с выходом первого коммутатора, инверсный выход второго блока сравнения соединен с входами первого и вто5рого блоков задания коэффициента, выход элемента И соединен с входами третьего и четвертого блоков задания коэффициента, прямой выход третьего блока сравнения соединен с входами

0 пятого и шестого блоков задания коэффициента, выходы первого, третьего и пятого блоков задания коэффи- . циента соединены с вторым входом второго умножителя, выходы второго,

5 четвертого и шестого блоков зсщания.

коэффициента соединены с вторым входом первого умножителя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-30—Публикация

1981-04-08—Подача