с входами первого элемента И, выход которого соединен с первыми входами элементов ИЛИ группы, вторые входы которых соединены соответственно с выходами коммутаторов второй группы, к-й инфйрмационный вход j -го коммутатора второй группы соединен с ()-м выходом сумматора, входы второго слагаемого сумматора соединены соответственно с шиной логического О, шиной логической 1, .выходом первого коммутатора первой группы, шинойлогического О, шиной логической 1, выходом элемен6155

та НЕ, выходом первого коммутатора первой группы, шиной логической 1, вход элемента НЕ соединен с выходом первого коммутатора первой группы, входы второго сомножителя умножителя с первого по седьмой соединены соответственно с шиной логической 1, выходом элемента НЕ, шиной логического О, шиной логической 1, выходом первого коммутатора первой группы, выходом элемента НЕ, шиной логического О, выходы элементов ИЛИ группы соединены соответственно с входами регистра результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее -регистр операнда, регистр результата, группу элементов ИЛИ, первый элемент И, элемент НЕ, блок управления, причем блок управления содержит группу элементов НЕ, первую и вторую группы элементов И, отличающееся тем, что, с целью повышения быстродействия, в него введены первая и вторая группы коммутаторов, умножитель, сумматор, а в блок управле:ния введены шесть элементов И,, раз- рядные входы первого слагаемого сумматора соединены соответственно с выходами умножителя, разрядные входы первого сомножителя которого соединены соответственно с выходами коммутаторов первой группы, -и информационный вход j-го коммутатора первой группы соединен с выходом

Изобретение относится к вычислительной технике и может быть исполь зовано при -построении специализированных вычислителей, предназначенны для цифровой обработки сигналов в реальных масштабах времени. Известно устройство для извлечения квадратного корня, содержащее треугольную матрицу вычислительных ячеек 111. Недостатком данного устройства являются большие аппаратурные затратЫфНаиболее близким к изобретению является устройство для извлечения квадратного корня, содержащее входной регистр, выходной регистр, генератор импульсов, делитель частоты, блок управления, первый и второ выходы Которого подключены к первым входам входного и выходного регистров соответственно, выход генерато ра импульсов соединен с входом делителя частоты, вычитающий счетчик, дешифратор, преобразователь параллельного входного кода в двоич ный код и элемент И, первый вход которого соединен с выходом генератора импульсов, второй вход соединен с третьим выходом блока управле ния, а выход подключен к первому входу вычитакнцего счетчика и третье му входу входного регистра, выходы которого соединены с первой группой входов выходного регистра и группой уходов блока управления, группа выходов которого соединена с группой входов преобразователя параллельного входного кода в двоичный код, группа выходов которого соединена с группами входов вычитающего счетчика 23, Недостатком известного устройства является его низкое быстродействие. Цель изобретения - повьш1ение быстродействия устройства. Поставленная цель достигается тем, что в устройство для извлечения квадратного корня, содержащее регистр операнда, регистр результата, группу элементов ИЛИ, первый элемент И, элемент НЕ, блок управления, причем блок управления содержит группу элементов НЕ, первую и вторую группы элементов И, дополнительно введены первая и вторая группы коммутаторов, умножитель, сумматор, а в блок управления введены шесть элементов И, разрядные входы первого слагаемого сумматора соединены с выходами умножителя, разрядные входы первого сомножителя которого соединены соответственно с выходами коммутаторов первой группы, i-й информационный вход j-го коммутатора первой группы соединен с выходом (2i + j -2)-го разряда регистра аргумента (1,3 1, п/2 , где п - разрядность регистра аргумента), разрядные-выходы регистров аргумента соединены с входами элементов НЕ группы, выходы (2 j -И -х элементов

3113

НЕ группы соединены соответсвенно с первыми входами элементов И первой группы, вторые входы которых соединены соответственно с выходами 2 J-X элементов НЕ группы, выход j-ro элемента И первой группы соединен с первым входом j-ro и вторым входом (j-l)-ro элементов И второй группы, выход первого элемента И второй группы соединен с первым входом первого элемента И блока управления, второй вход которого соеди-нен с инверсным выходом второго элемента И блока управления, первый вход которого соединен с инверсным выходом третьего элемента И блока управления, первый вход которого соединен с выходом четвертого элемента И второй группы, выход шестого элемента И которой соединен с вторым входом третьего элемента И блока управления, первый вход четвертого элемента И блока управления соединен с выходом первого элемента И второй группы и первым входом пятого элемента И блока управления, второй вход которого соединен с первым входом шестого элемента И блока управления и выходом третьего элемента И второй группы, выход пятого элемента И которого соединен с вторым входом шестого элемента И блока управления, инверсный выход которого соединен с вторым входом четвертого элемента И блока управления, выход второго элемента И второй группы соединен с вторым входом, второго элемента И блока управленияj выходы пятого, четвертого и первого элементов И блока управления соединены соответственно с управляющими входами всех коммутаторов, выходы коммутаторов с первого по ;п/2 - 1-й первой группы соединены с входами первого элемента И, выход которого соединен с первыми входами элементов ИЛИ группы, вторые входы которых соединены соответственно с выходами коммутаторов второй груйпы, 1(-й инфо мационный вход j-ro коммутатора второй группы соединен с (j- V;+ 1)-м выходом сумматора, входы второго слагаемого сумматора с первого по восьмой соединены соответственно с шиной логического О, шиной логической 1, выходом первого коммутатора первой группы, шиной логического О, шиной логической I, выходом элемента НЕ, выходом первого коммутатора первой группы, шиной логической 1, вход элемента НЕ соединен с выходом первого коммутатора первой группы, входы второго сомножителя умножителя с первого по седьмой соединены соответственно с шиной логической 1, выходом элемента НЕ, шиной логического О шиной логической 1, выходом первого коммутатора первой группы, выходом элемента НЕ, шиной логического О, выходы элементов ИЛИ группы соединены соответственно с входами регистра результата.

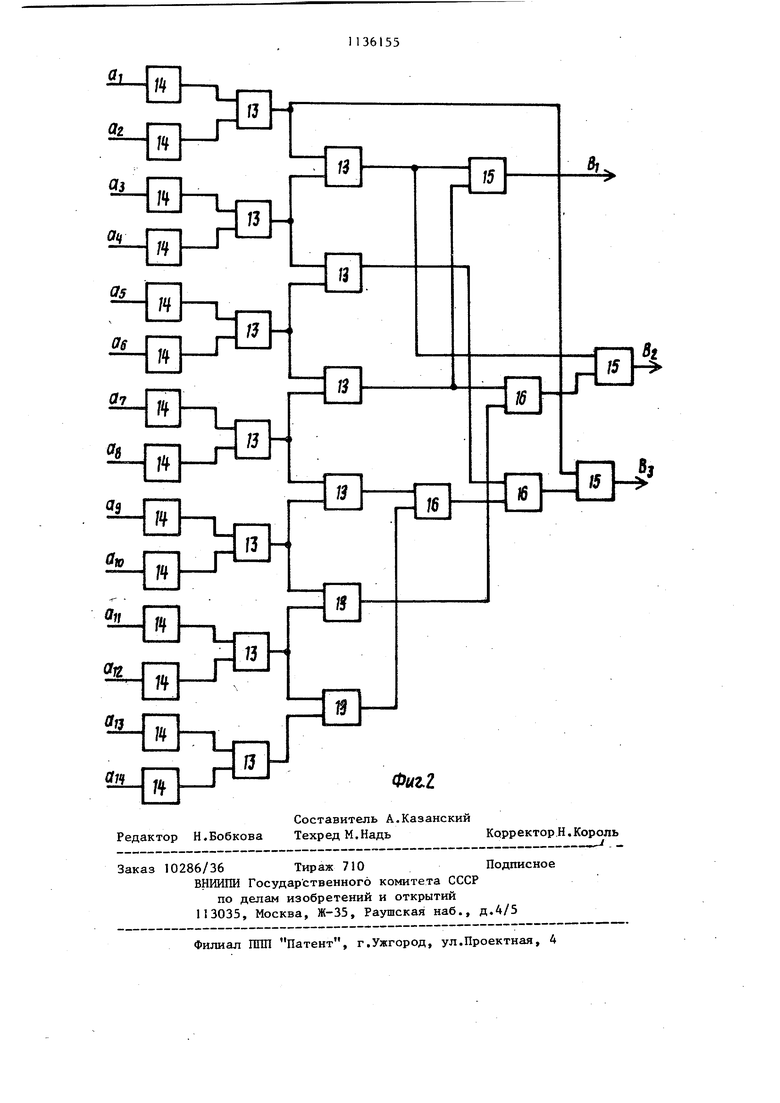

На фиг. 1 приведена блок-схема устройства для извлечения квадратного корня; на фиг. 2 - блок-схема устройства управления.

Устройство (фиг.1) содержит регистр I операнда, коммутаторы 2 первой группы, коммутаторы 3 второй группы, блок 4 управления, умножитель 5, элемент НЕ 6, сумматор 7, шину 8 логической 1, шину 9 логического О, регистр 10 результата, группу элементов ИЛИ 1 1., элемент И 12. Блок управления (фиг. 21 содержит группы элементов И 13, группу элементов НЕ 14, элементы И 15, элементы И-НЕ 16.

Устройство работает следующим образом.

Аргумент А представлен двоичным числом с фиксированной.запятой:

, а а 2 ... а , где а - старший разряд мантиссы

входного числа; а - младший разряд мантиссы входного числа.

Входное число, выраженное параллельным прямым кодом, записывается во входном регистре 1, С выхода регистра 1 сигналы всех разрядов поступают на первую группу коммутаторов 2 и блок 4 управления, с помощью которых осуществляется нормализация входного числа. При четном числе равных нулю старших разрядов мантиссы входного числа (или в случае, когда старший разряд числа равен логической 1)) старший разряд числа, снимаемого с выхода первого коммутатора 2 первЬй группы, который соединен со старшим разрядом первого сомножителя умножителя 5, равен логической 1. При нечетном Числе равных нулю старших разрядов мантиссы входного числа сигнал, сни маемьш с выхода первого ко1«1мутатора 2 первой группы, равен нулю. Таким образом, при входном числе больше О нормализация приводит к тому, что на вход двух старших разрядов первого сомножителя умножителя 5 поступает либо комбинация 01, либо Ijf; Управление коммутаторами осущест вляется М-разрядным кодом ( который вьфабатывается блоком 4 управления. В результате нормализации на вхо ды первого сомножителя умножителя 5 подается число А, которое по. своей величине находится в пределах 0,25 $ А 1. Старший разряд числа, снимаемого с первой группы коммутаторов 2, подается также на вход элемента НЕ 6, на вход-пятого разряда второ сомножителя умножителя 5 и на треTHi. и седьмой входы второго слагае;мого сумматора 7. На второй и шестой входы второго сомножителя умножителя 5, а также на шестой вход второго слагаемого сумма1тора 7 подаются с выхода элемента НЕ 6. Сиг налы Лог. 1 с шины 8 подаются на первый и четвертый входы второго со ножителя умножителя 5 и второй, пятый и восьмой входы второго слага мого сумматора 7. Все остальные входы умножителя 5 и сумматора 7 соединены с шиной 9 логического О. В результате с выходов сумматора 7 снимается число, которое опре деляется следующими формулами, соот ветствующими линейно-ломаной аппрок симации: 19/64 + 53/64А, при 1/4«А Г/ 53/128 + 19/32-А, при при 63/64М 1 127/128, или в двоичном коде: -0,0100110 + + 0,110101 А, при 0,,1 0,0110101 + 0,100110-А, при О,,1111 0,111111 при 0,innUA l Поскольку при ,1 d, 1,А при .0,01 А О, 1 « 0. Указанные формулы с учетом значеНИИ старшего разряда а, ВХОДНОГО числа можно записать следующим образом:0,01с( + 0, 0-1 А, при 0,,1 11111 0,1111111, при 0,1111 . Умножение нормализованного числа А на коэффициент О, производится в умножителе 5, при этом инверсные значения старшего разряда числа А (5) снимаются с выхода элемента НЕ 6. В сумматоре 7 осуществляется сложение числа О, 1 м.,01 .ot « А с постоянным членом 0,01о(01 «.,. Многоразрядное число с выхода сумматора поступает на вторую группу коммутаторов 3, где осуществляется денормализация результата. При этом сдвиг вправо по отношению к запятой для выходного числа осуществляется на разрядов, где Е - количество пар нулевых старших разрядов входного числа. Управление коммутаторами 3 второй группы осуществляется тем же кодом управления, вырабатываемым блоком 4 управления, который используется для управления коммутаторов первой группы. Сигналы с выходов коммутаторов второй группы через элементы ИЛИ 1 подаются на выходной регистр 10, выходы которого являются выходами устройства. При равенстве всех значаш 1х разрядов входного числа, поступающих на .входы блока 4 управления, нулю блок 4 управления вырабатывает специальный код, обеспечивающий получение нулевого результата на выходе устройства, для чего все восьмые входы коммутаторов 3 второй группы соединены с шиной логического О. В том случае, когда- первые шесть старших разрядов числа, снимаемого с коммутаторов 2 первой группы, и соединенные с входами элемента И 12, равны логической 1, на выходе элемента И 12 появляется логическая 1, которая через элементы ИЛИ 11 подается на вход регистра 10,

7 11361558

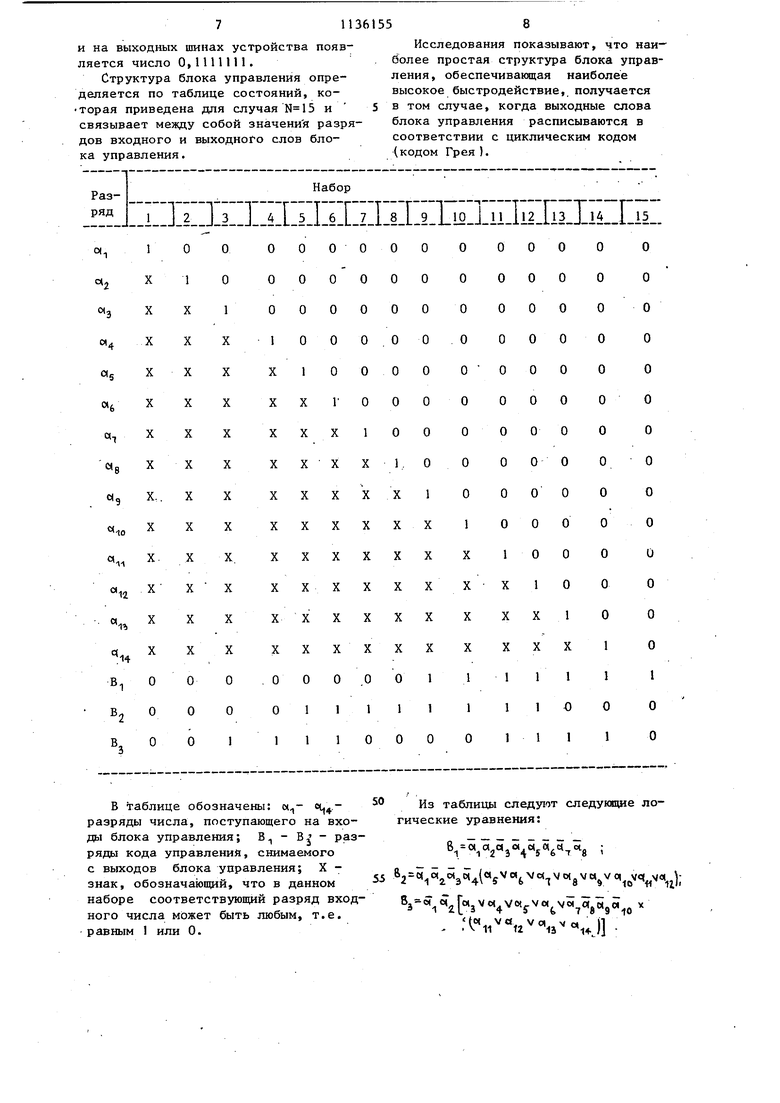

и на выходных шинах устройства нояв-Исследования показывают, что наиляется число О, ПИ 41-более простая структура блока управСтруктура блока управления опре-ления, обеспечивающая наиболее

деляется по таблице состояний, ко-высокое быстродействие, получается

торая приведена для случая и 5 в том случае, когда выходные слова

связывает между собой значения разря-блока управления расписываются в

дов входного и выходного слов бло-соответствии с циклическим кодом

ка управления.(кодом Грея). В таблице обозначены: «1,4разряды числа, поступающего на входы блока управления; В - Bj - разряды кода управлений, снимаемого С выходов блока управления; X знак, обозначающий, что в данном 55 наборе соответствующий разряд входного числа может быть любым, т.е. равным 1 или 0. Из таблицы следуют следующие логические уравнения: 6,«i«2«3 «s 6S 8 ; «i«2«3 4K t «1 «8 .V); Г r«,v«.v«,.vo( v« «,« « х f7 8 9 ю Л 11 t2 la «14. ) Выходной код блока управления BI В В, поступает на управляющие входы коммутаторов.

Введение в известное устройство первой и второй группы коммататоров, умножителя сумматора и шести элементов И позволяет получить более высокое быстродействие. Результат

в предлагаемом устррпстве формируется за один такт, равный Сумматору времени переходных процессов в блоках устройства. В известномt результат формируется за несколько тактов, при этом количество тактов прямо пропорционально разрядности аргумента.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 754411, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1982-12-14—Подача