Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления функции Z= , со- держащее два коммутатора, три блока сравнения, элемент И, два умножителя, шесть блоков задания коэффициента и сумматор, причем входы первого и второго аргументов устройства соединены соответственно с первым и вторым информационными входами первого коммутатора и первым и вторым входами первого блока сравнения, прямой выход которого соединен с управляющим входом первого коммутатора, выход которого соединен с первыми входами второго и третьего блока сравнения, соответственно прямой и инверсный выходы которых соединены с первым и вторым входами элемента И, первый и второй информационные и управляющие входы второго коммутатора соединены соответственно с входами первого и второго аргументов устройства и инверсным выходом первого блока сравнения, выход второго коммутатора соединен с вторыми входами второго и третьего блоков сравнения и первым входом первого умножителя, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом второго умножителя, первый вход которого соединен с выходом первого коммутатора, инверсный выход второго блока сравнения соединен с входами первого и второго блоков задания коэффициента, выход элемента И соединен с входами третьего и четвертого блоков задания коэффициента, прямой выход третьего блока сравнения соединен с входами пятого и шестого блоков задания коэффициента, выходы первого, третьего и пятого блоков задания коэффициента соединены с вторым входом второго умножителя, выходы второго, четвертого и шестого блоков задания коэффициента соединены с вторым входом первого умножителя.

, со- держащее два коммутатора, три блока сравнения, элемент И, два умножителя, шесть блоков задания коэффициента и сумматор, причем входы первого и второго аргументов устройства соединены соответственно с первым и вторым информационными входами первого коммутатора и первым и вторым входами первого блока сравнения, прямой выход которого соединен с управляющим входом первого коммутатора, выход которого соединен с первыми входами второго и третьего блока сравнения, соответственно прямой и инверсный выходы которых соединены с первым и вторым входами элемента И, первый и второй информационные и управляющие входы второго коммутатора соединены соответственно с входами первого и второго аргументов устройства и инверсным выходом первого блока сравнения, выход второго коммутатора соединен с вторыми входами второго и третьего блоков сравнения и первым входом первого умножителя, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом второго умножителя, первый вход которого соединен с выходом первого коммутатора, инверсный выход второго блока сравнения соединен с входами первого и второго блоков задания коэффициента, выход элемента И соединен с входами третьего и четвертого блоков задания коэффициента, прямой выход третьего блока сравнения соединен с входами пятого и шестого блоков задания коэффициента, выходы первого, третьего и пятого блоков задания коэффициента соединены с вторым входом второго умножителя, выходы второго, четвертого и шестого блоков задания коэффициента соединены с вторым входом первого умножителя.

Недостатком этого устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия.

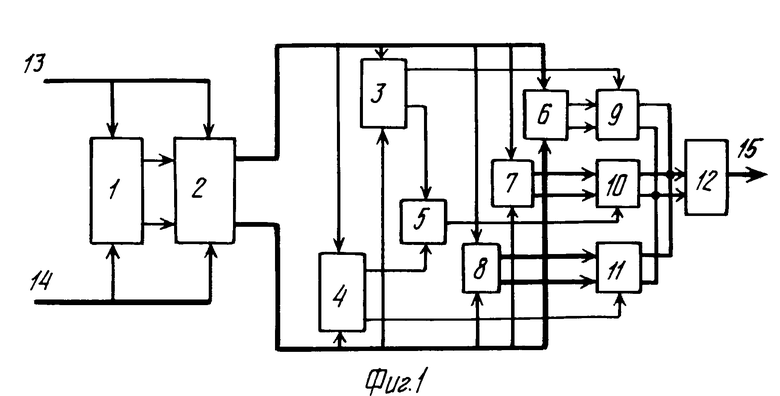

Цель достигается тем, что в устройство для вычисления модуля вектора, содержащее первый, второй и третий блоки сравнения, коммутатор, сумматор и элемент И, причем входы первого и второго аргументов устройства соединены соответственно с первыми и вторыми информационными входами первого блока сравнения и коммутатора, управляющие входы которого соединены соответственно с первым и вторым выходами первого блока сравнения, первый выход коммутатора соединен с первыми информационными входами второго и третьего блоков сравнения, второй выход коммутатора соединен с вторыми информационными входами второго и третьего блоков сравнения со сдвигом соответственно на один и два разряда в сторону старших разрядов, второй выход второго блока сравнения и первый выход третьего блока сравнения соединены с первым и вторым входами элемента И, а выход сумматора является выходом устройства, введены первый, второй и третий преобразователи многорядного кода в двухрядный и первый, второй и третий блоки элементов И, каждый из которых содержит две группы элементов И, первые входы которых являются соответственно первым и вторым информационными входами блока элементов И, вход управления которого соединен с вторыми входами элементов И обеих групп, выходы которых являются соответственно первым и вторым выходами блока элементов И, причем первый выход коммутатора соединен с первыми входами первого, второго и третьего преобразователей многорядного кода в двухрядный, вторые входы которых соединены с вторым выходом коммутатора, а первый и второй выходы первого, второго и третьего преобразователей многорядного кода в двухрядный соединены соответственно с первыми и вторыми информационными входами первого, второго и третьего блоков элементов И, первые выходы которых соединены с первым входом сумматора, второй вход которого соединен с вторыми выходами первого, второго и третьего блоков элементов И, управляющий вход первого блока элементов И соединен с первым выходом второго блока сравнения, управляющий вход второго блока элементов И соединен с выходом элемента И, а управляющий вход третьего блока элементов И соединен с вторым выходом третьего блока сравнения.

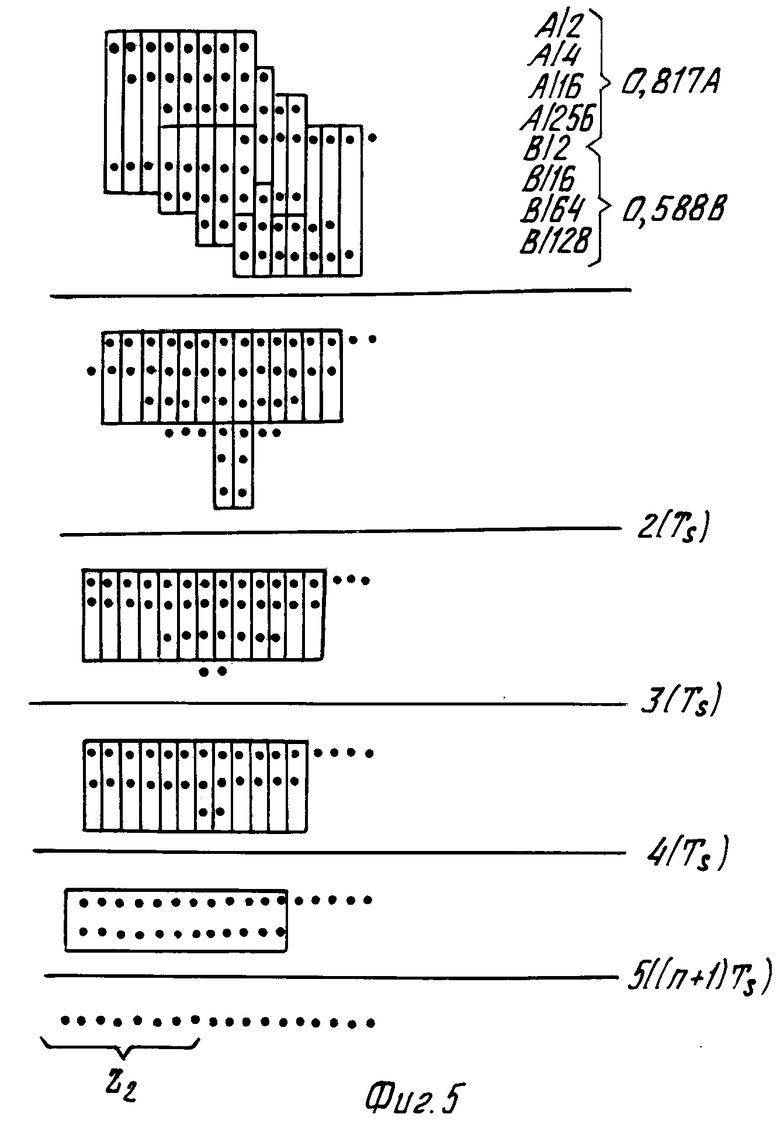

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема преобразователя многорядного кода в двухрядный; фиг. 3...5 иллюстрирует процесс преобразования кодовых матриц z.

Устройство (фиг. 1) содержит первый блок 1 сравнения, коммутатор 2, второй 3 и третий 4 блоки сравнения, элемент И 5, первый 6, второй 7 и третий 8 преобразователи многорядного кода, первый 9, второй 10 и третий 11 блоки элементов И, сумматор 12, входы первого 13 и второго 14 аргументов, выход 15.

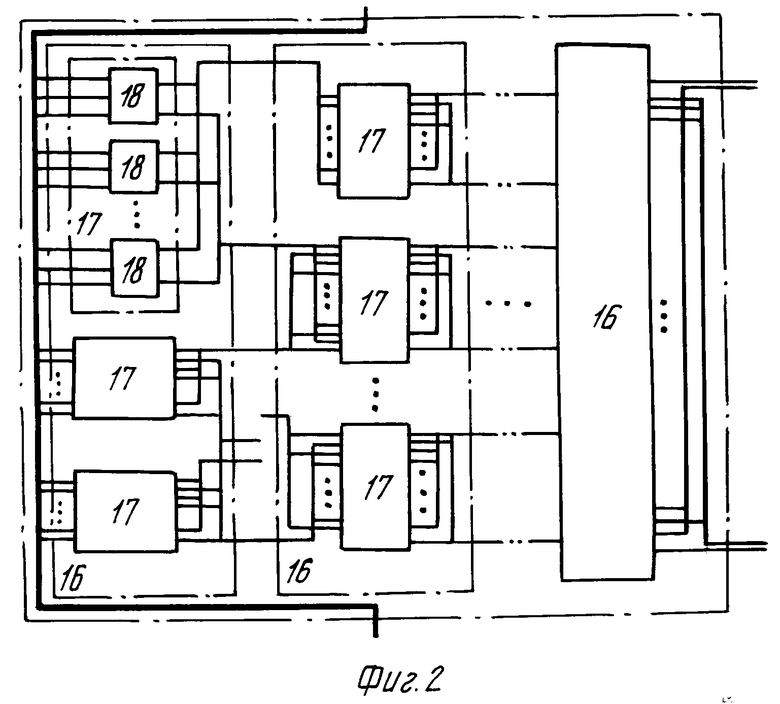

Преобразователь многорядного кода (фиг. 2) содержит α слоев 16 сумматоров (α - количество тактов свертывания исходной кодовой матрицы z до двухрядного кода результата) содержащих блоки 17 сумматоров единого веса, состоящие из одноразрядных трехвходовых сумматоров 18.

Устройство реализует ту же аппроксимирующую зависимость, что и прототип:

Устройство функционирует под воздействием синхронизирующих сигналов, подаваемых на коммутатор (на фигурах не показаны).

По шинам 13, 14 на входы коммутатора 2 и блока 1 поступают прямые коды  х

х и

и  y

y . Коммутатор 2 реализует операцию по первому (А) и второму (В) выходам:

. Коммутатор 2 реализует операцию по первому (А) и второму (В) выходам:

В результате сравнения на втором выходе блока 1 образуется сигнал единичного уровня в случае, если  х

х <

<  y

y . Этот сигнал вызывает появление аргумента

. Этот сигнал вызывает появление аргумента  y

y на первом выходе коммутатора 2, а аргумента

на первом выходе коммутатора 2, а аргумента  х

х на втором выходе коммутатора 2. В случае

на втором выходе коммутатора 2. В случае  х

х ≥

≥  y

y сигнал единичного уровня образуется на первом выходе блока 1. По этому сигналу на первом выходе коммутатора появляется аргумент

сигнал единичного уровня образуется на первом выходе блока 1. По этому сигналу на первом выходе коммутатора появляется аргумент  х

х , а на втором -

, а на втором - y

y  .

.

Блоки 3 и 4 работают аналогично блоку 1, вырабатывая результаты сравнения соответственно значений А и 4В, А и 2В. Сигнал с первого выхода блока 3 (А ≥ 4В) является управляющим для блока 9 элементов И, сигнал с второго выхода блока 4 (А < 2В) является управляющим для блока 11, объединение сигналов с второго выхода блока 3 и первого выхода блока 4 на элементе И 5 (4В > А ≥ 2В) обеспечивает управляющий сигнал для блока 10.

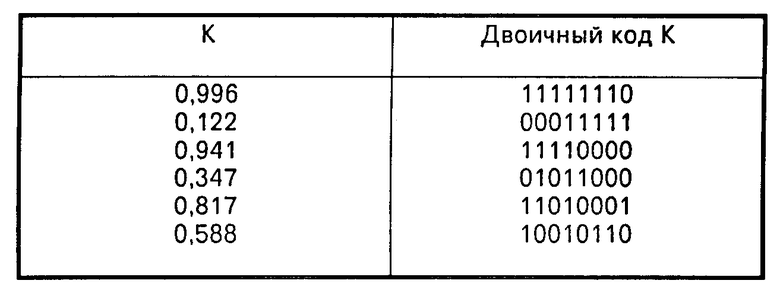

Блоки элементов И 9, 10, 11 обеспечивают прохождение на выходы сумматора 12 одного из трех результатов преобразования в преобразователях 6, 7, 8 - соответственно двухстрочных кодовых матриц z1= 0,996А + 0,122В, z2 = 0,941А + 0,347В, z3 = 0,817А + 0,588В. На входы преобразователей многорядного кода поступают парафазные коды А и В. В основу функционирования преобразователей положен принцип замены операций умножения аргументов на m-разрядные константы операциями сложения аргументов, сдвинутых на число разрядов, определяемое положением единиц в двоичном коде константы (таблица для m = 8).

Полученная таким образом кодовая матрица (КМ) содержит число слагаемых, определяемое числом значащих единиц, в константах k1 и k2аппроксимации. Если количество значащих единиц в коде больше половины разрядов, то целесообразен переход к представлению константы в виде k = 1-kдоп, где kдоп - дополнительный код исходной константы. Это позволяет уменьшить время вычисления. Очевидно, что такой подход применим к аппроксимации z1.

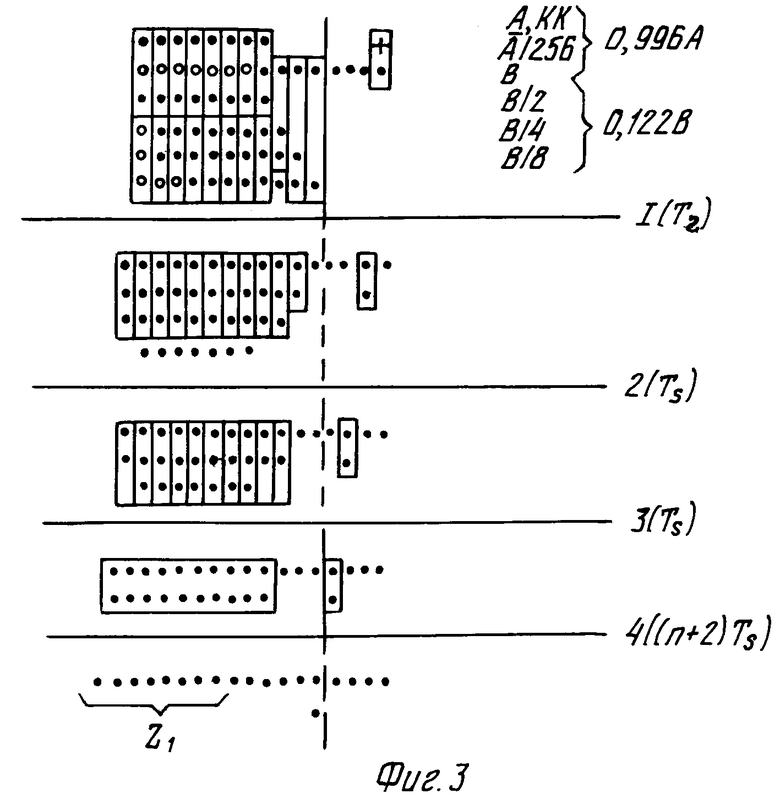

На фиг. 3 показан процесс преобразования кодовой матрицы z1, сформированной путем коммутации линий данных соответствующего веса входов преобразователя с входами его сумматоров: прямой код аргумента А, обратный код аргумента А, сдвинутый вправо на семь разрядов ( /256), прямой код аргумента В, обратные коды аргумента В, сдвинутые вправо соответственно на один, два и три разряда (

/256), прямой код аргумента В, обратные коды аргумента В, сдвинутые вправо соответственно на один, два и три разряда ( /2 +

/2 +  /4 +

/4 +  /8 ≈ 0,878

/8 ≈ 0,878  ). Точками на фигуре обозначены двоичные разряды кодов соответствующего веса, кружками - разряды, принимающие значение старшего разряда обратного кода, знаком "+" - код коррекции (КК), служащий для образования дополнительного кода из обратного - единица младшего разряда обратного кода. Рамки окружают разряды, подаваемые на входы сумматоров. Номера тактов преобразования представлены возле горизонтальной линии, там же в скобках указано время преобразования в тактах работы одноразрядного сумматора. Фигура показывает, что младшими разрядами КМ можно пренебречь.

). Точками на фигуре обозначены двоичные разряды кодов соответствующего веса, кружками - разряды, принимающие значение старшего разряда обратного кода, знаком "+" - код коррекции (КК), служащий для образования дополнительного кода из обратного - единица младшего разряда обратного кода. Рамки окружают разряды, подаваемые на входы сумматоров. Номера тактов преобразования представлены возле горизонтальной линии, там же в скобках указано время преобразования в тактах работы одноразрядного сумматора. Фигура показывает, что младшими разрядами КМ можно пренебречь.

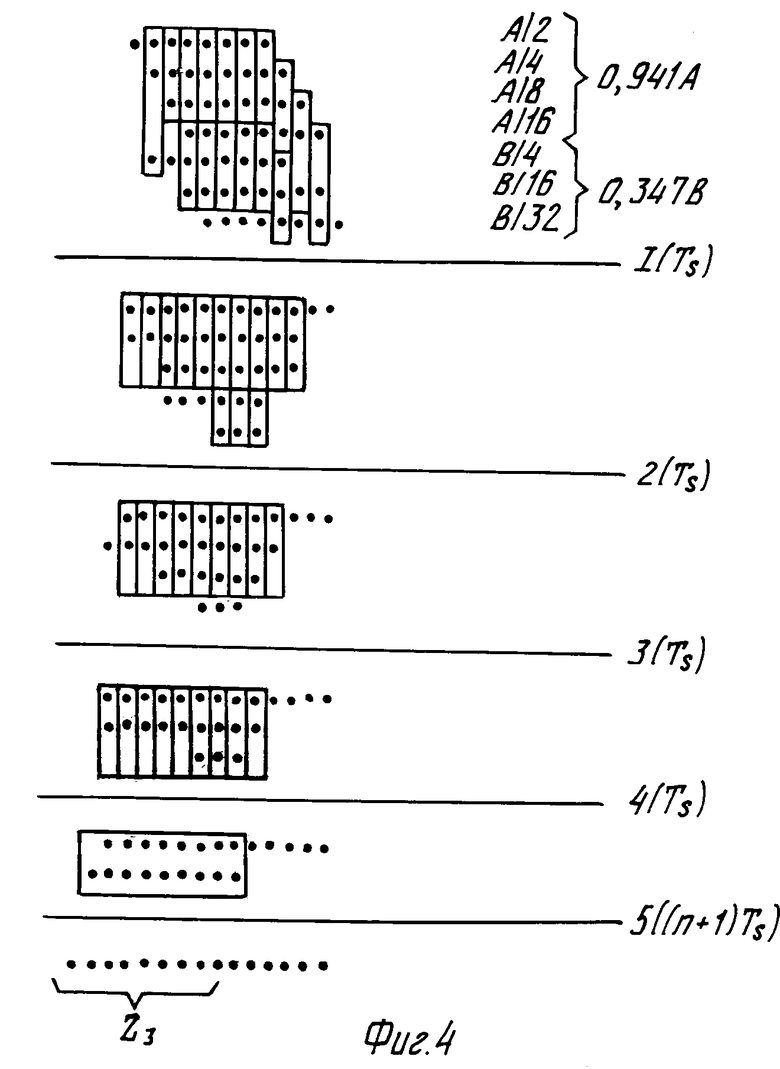

На фиг. 4, 5 показан процесс преобразования КМ z2 и z3. Обозначения аналогичны приведенным выше.

Последний такт преобразования до однострочного кода результата во всех трех случаях выполняется на параллельном сумматоре 12. Его разрядность определяется разрядностью наибольшей из двухстрочных КМ z1, z2, z3. Разрядность сумматора 12 может быть равна разрядности аргументов, тогда младшие разряды КМ могут усекаться как не влияющие на точность результата. При m≥7 погрешность за счет усечения не превышает максимальной погрешности аппроксимации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1305674A1 |

| Устройство для вычисления модуля вектора | 1989 |

|

SU1635182A1 |

| Устройство для вычисления модуля вектора | 1988 |

|

SU1541602A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Устройство для выполнения дискретных ортогональных преобразований | 1984 |

|

SU1233168A1 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1983 |

|

SU1107133A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| СОЮЗНАЯ Iмшшда^'"""ЙИБЛИОТЕК^ | 1972 |

|

SU331386A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях. Цель изобретения - повышение быстродействия. Устройство для вычисления модуля вектора содержит три блока 1,3,4 сравнения, коммутатор 2, элемент И 5, три преобразователя 6,7,8 многорядного кода, три блока 9,10,11 элементов И и сумматор 12, соединенные между собой функционально. 1 з.п. ф-лы, 1 табл. 5 ил.

| Устройство для вычисления функции Z= @ х @ +у @ | 1981 |

|

SU962925A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-10-30—Публикация

1991-06-19—Подача