Изобретение относится к вычислительной технике и мояет быть применено в устройствах управления памяти ЭВМ. Известно устройство для управления памятью, содержащее блок управления, память, распределитель, блок обработки информации tl. Недостатком известного устройштва является большой объем оборудования и невысокая надежность. Наиболее близким по техн гческой сущности к предлагаемому является устройство, содержащее два генератор три распределителя, два счетчика, дв кс мутатора, группу, элементов И, группу сумматоров по модулю два, три триггера, два элемента И, дешифратор 2. Однако конструкция известного уст ройства не позволяет реализовать алгоритм контроля и/или диагностики при возникновении сбоя, отказа в памяти или устройстве управления памят для обнаружения и коррекции неисправ ности, что приводит к снижению надежности устройства. Целью изобретения является повыше ние надежности устройства. Поставленная цель достигается тем, что в устройство для управления памятью, содержгицее дешифратор, генератор сигналов регенерации, выход которого соединен с первьы входот первого распределителя и входом первого счетчика, выход которого соединен с первом входом первого коммутатора, выход которого соединен с первьвл выходом устройства, первый выход первого распределителя соединен с вторьм входом первого коммутатора, генератор синхросигналов, выход которого соединен с первыми входё1ми первого и второго элементов И и с входом элемента НЕ, выход которого соединен с синхровходом первого триггераv выход которюго соединен с вторым входом первого элемента И, третий вход которого соединен с выходом второго триггера, .. D-вход которого соединен с первьм входом устройства, выход первого элемента И соединен с управляющим входом второго рахшределителя, первый выход которого соединен с четвертым первого элемента И, и вторым входом первого распределителя, второй зыход второго распределителя соединен с D-входом третьего триггера, выход второго элемента И соединен с входом РТОрого счетчика и с пятым входом первого элемегта И, первый выход второго счетчика соединен с управляющим входом третьего распределителя, а его выход соединен с первыми входами элементов И группы, второй выход второ о счетчика соединен с вторым входом второго элемента И, третий вход которого соединен с выходом третьего тригера, четвертый вход второго элемента И соединен с первым выходом второго ;коммутатора, первый вход которого, второй вход регистра и первый вход дешифратора соединены с выходом третьего распределителя, второй вход усройства соединен с вторыми входами элементов И группы, выходы которых соединены соответственно с первыми входами сумматоров по модулю два группы, выходы которых соединены с первыми входами регистра, выход KOTO рого соединен с вторым входом второг кбммутатора, второй выход которого соединен с вторым выходом устройства и вторым входом дешифратора, выходы которого соединены соответственно с вторыми входами сумматоров группы по модулю два, введены формирователи циклов чтения и записи и элемент ИЛИ, причем второй выход первого распределителя соединен с первыми входами формирователей циклов чтения и записи, первые выходы которых соединены с входами элемента ИЛИ выход которого соединен с вторым входом первого триггера и с шестым входом первого элемента И, третий выход второго распределителя соединен с вторым входом формирователя циклов чтения/ а четвертьШ выход второго распределителя соединен с вторым входом формирователя циклов записи, второй выход которого соединен с третьим входом первого распределителя, второй выход формирователя циклов чтения соединен с третьим входом первого коммутатора. .

Формирователь циклов чтения содержит генератор циклов, счетчик, триггер, коммутатор, два элемента ИЛИ, элемент И, причем первый вход формирователя циклов чтения соединен с первыми входами триггера и коммутатора, а второй вход формирователя циклов чтения соединен с первыми входами генератора циклов и элемента И, вторые входы которых соединены с первым входом первого элемента :ИЛИ и первым выходом счетчика, второй выход которого соединен с вторым входом коммутатора, выход которого соединен с нервном входом второго элемента ИЛИ, выход которого соедине с вторым выходом формирователя циклов чтения, первый выход которого соединен с выходом первого элемента ИЛИ, второй вход которого и второй вход второго элемента ИЛИ соединены

с выходом триггера, второй вход которого соединен с выходом элемента вьрсод генератора циклов соединен с входом счетчика.,.

Кроме того, формирователь -циклов записи содержит генератор циклов, счетчик, коммутатор, причем первый и второй входы формирователя циклов записи соединены соответственно с пвыми входами генератора циклов и коммутатора, первый и второй выходы которого соединены с первыми и вторым выходами формирователя циклов записи, выход генератора циклов соединен с входом счетчика, первый и врой выходы.которого соединены с вторыми входами генератора циклов и коммутатора.

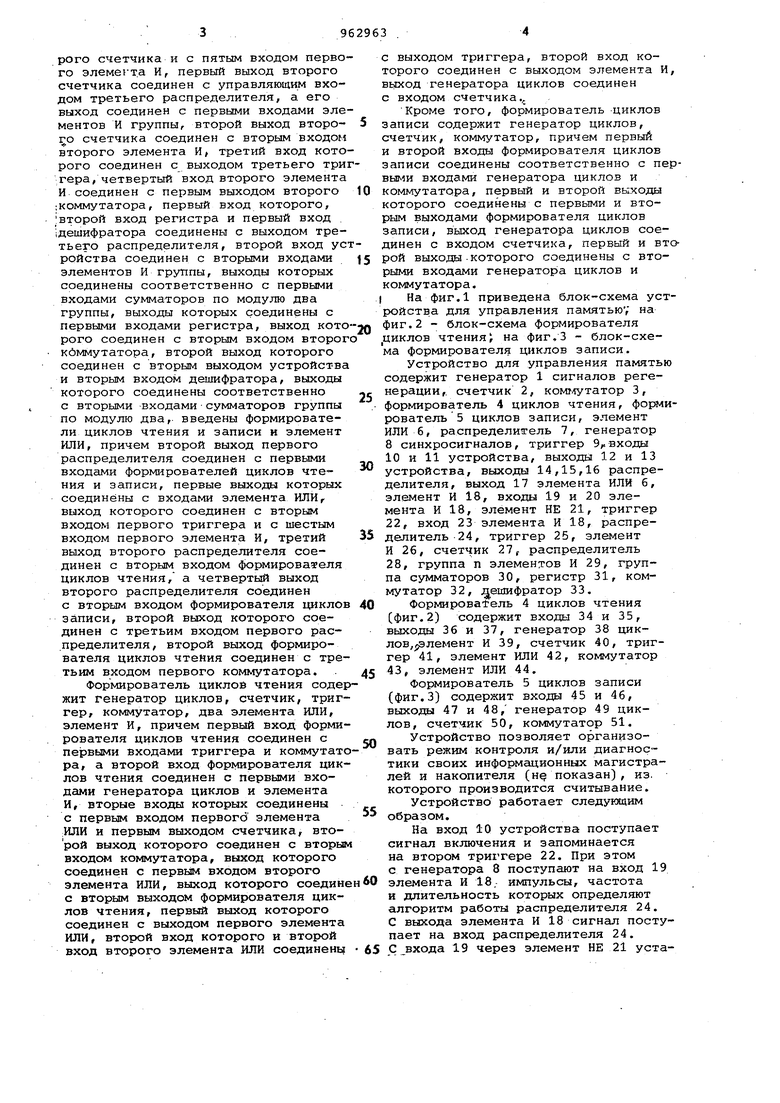

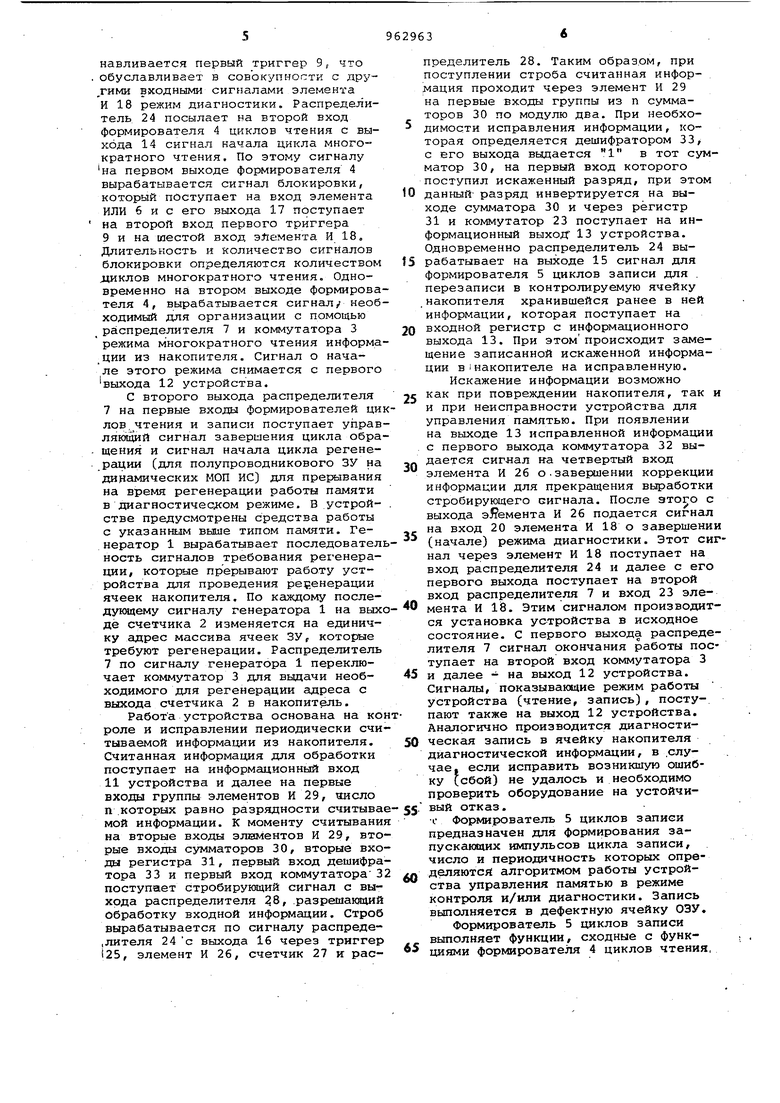

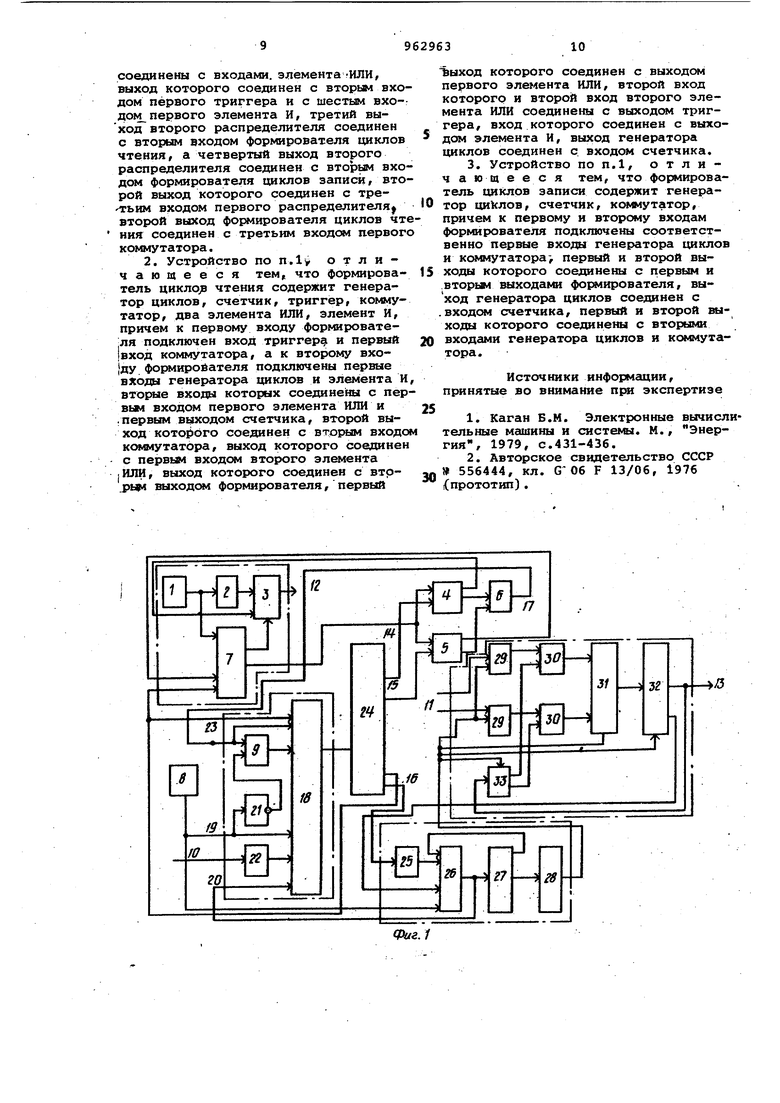

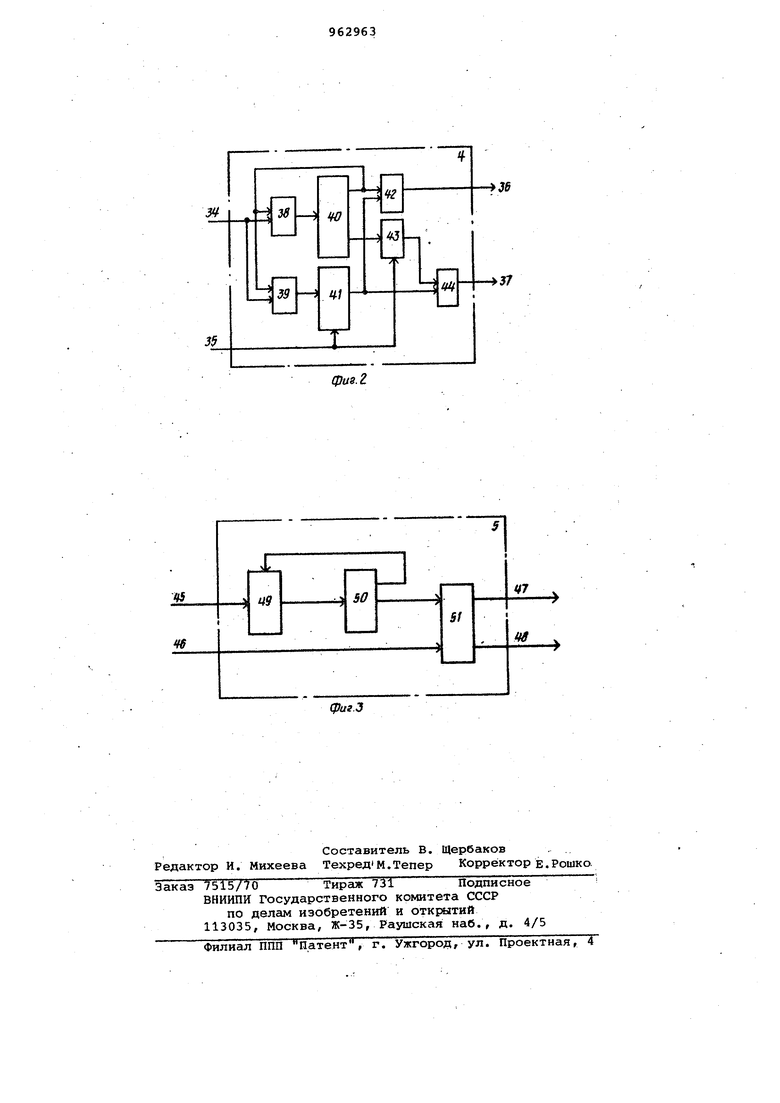

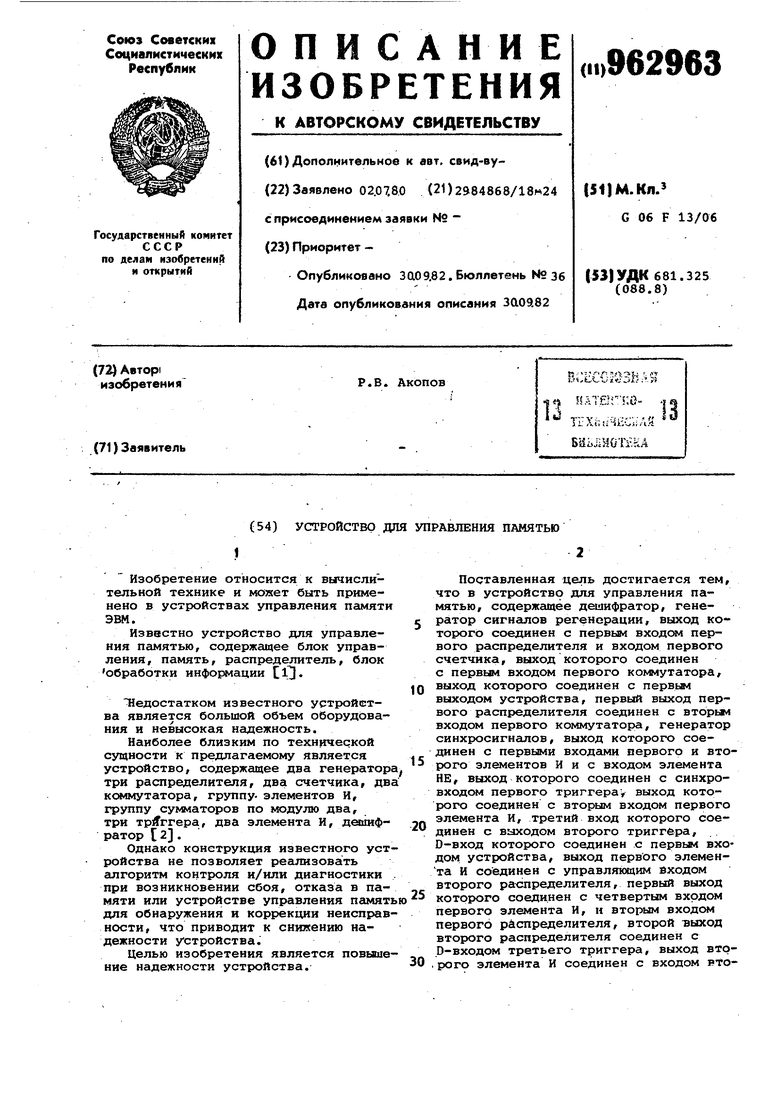

I На фиг.1 приведена блок-схема усройства для управления памятью , на фиг.2 - блок-схема формирователя циклов чтенияi на фиг.З - блок-схема формирователя циклов записи.

Устройство для управления память содержит генератор 1 сигналов регенерации,, счетчик 2, коммутатор 3, формирователь 4 циклов чтения, формрователь 5 циклов записи, элемент ИЛИ 6, распределитель 7, генератор 8 синхросигналов, триггер 9 входы 10 и 11 устройства, выходы 12 и 13 устройства, выходы 14,15,16 распределителя, выход 17 элемента ИЛИ 6, элемент И 18, входы 19 и 20 элемента И 18, элемент НЕ 21, триггер 22, вход 23 элемента И 18, распределитель 24, триггер 25, элемент И 26, счетчик 27, распределитель 28, группа п элементов И 29, группа сумматоров 30, регистр 31, коммутатор 32, д ешифратор 33.

Формирователь 4 циклов чтения (фиг.2) содержит входы 34 и 35, выходы 36 и 37, генератор 38 циклов,рэлемент И 39, счетчик 40, триггер 41, элемент ИЛИ 42, коммутатор 43, элемент ИЛИ 44.

Формирователь 5 циклов записи {фиг.З) содержит входы 45 и 46, выходам 47 и 48/ генератор 49 циклов, счетчик 50, коммутатор 51.

Устройство позволяет организовать режим контроля и/или диагностики своих информационных магистралей и накопителя (HQ показан), из. которого производится считывание.

Устройство работает следующим образом.

На вход 10 устройства поступает сигнал включения и запоминается иа втором триггере 22. При этом с генератора 8 поступают на вход 19 элемента И 18,- импульсы, частота и длительность которых определяют алгоритм работы распределителя 24. С выхода элемента И 18 сигнал поступает на вход распределителя 24. С входа 19 через элемент НЕ 21 устанавливается первый триггер 9, что обуславливает в совокупности с дру,гими входными сигналами элемента И 18 режим диагностики. Распределитель 24 посылает на второй вход формирователя 4 циклов чтения с вы- кода 14 сигнал начала цикла многократного чтения. По этому сигналу на первом выходе формирователя 4 вырабатывается сигнал блокировки, который поступает на вход элемента О ИЛИ бис его выхода 17 поступает на второй вход первого триггера 9 и на шестой вход элемента И 18. Длительность и количество сигналов блокировки определяются количеством fS ликлов многократного чтения. Одновременно на втором выходе формирователя 4, вырабатывается сигнал/ необходимый для организации с помощью распределителя 7 и коммутатора 3 20 режима многократного чтения информа ции из накопителя. Сигнал о начале этого режима снимается с первого выхода 12 устройства.

С второго выхода распределителя 25 7 на первые входы формирователей циклов,чтения и записи поступает управляклдий сигнал завершения цикла обращения и сигнал начала цикла регенерации (для полупроводникового ЗУ на JQ динамических МОП ИС) для прерывания на время регенерации работы памяти в диагностичесд ом режиме. В устрой- . стве предусмотрены средства работы с указанным выше типом памяти, Ге- ,, нератор 1 вырабатывает последовательность сигналов требования регенерации, которые прерывают работу устройства для проведения регенерации ячеек накопителя. По каждому последукнцему сигналу генератора 1 на выхо- де счетчика 2 изменяется на единичку адрес массива ячеек ЗУ, которые требуют регенерации. Распределитель 7 по сигналу генератора 1 переключает коммутатор 3 для выдачи необ- 45 ходимого для регенерации адреса с выхода счетчика 2 в накопит ь,

Работа устройства основана на контроле и исправлении периодически считываемой информации из накопителя. 50 Считанная информация для обработки поступает на информационный вход 11 устройства и далее на первые входы группы элементов И 29, аисло п .которых равно разрядности считывав-$5 мой информации. К моменту считывания на вторые входы элементов И 29, вторые входы сумматоров 30, вторые входы регистра 31, первый вход дешифратора 33 и первый вход коммутатора32 поступает стробирующий сигнал с выхода распределителя 28, .разрешакядий Обработку входной информации, Строб вырабатывается по сигналу распреде.лителя 24 с выхода 16 через триггер . i25, элемент И 26, счетчик 27 к рас-

пределитель 28, Таким образ.ом, при поступлении строба считанная информация проходит через элемент И 29 на первые входы группы из п сумматоров 30 по модулю два. При необходимости исправления информации, которая определяется дешифратором 33/ с ЕГО выхода выдается 1 в тот сумматор 30, на первый вход которого поступил искаженный разряд, при этом данный- разряд инвертируется на выходе сумматора 30 и через регистр 31 и коммутатор 23 поступает на информационный выход- 13 устройства. Одновременно распределитель 24 вырабатывает на выходе 15 сигнал для формирователя 5 циклов записи для перезаписи в контролируемую ячейку .накопителя хранившейся ранее в ней информации, которая поступает на входной регистр с информационного выхода 13, При этомпроисходит замещение записанной искаженной информации внакопителе на исправленную.

Искажение информации возможно как при повреждении накопителя, так и при неисправности устройства для управления пгмятью. При появлении на выходе 13 исправленной информации с первого выхода коммутатора 32 выдается сигнал н-а четвертый вход элемента И 26 о.завершении коррекции информации для прекращения выработки стробирующего сигнала. После этого с выхода элемента И 26 подается сигнал на вход 20 элемента И 18 о завершени (начале) режима диагностики. Этот синал через элемент И 18 поступает на вход распределителя 24 и далее с его первого выхода поступает на второй вход распределителя 7 и вход 23 элемента И 18. Этим сигналом производится установка устройства в исходное состояние. С первого выхода распределителя 7 сигнал окончания работы поступает на второй вход коммутатора 3 и далее - на выход 12 устройства. Сигналы, показывающие режим работы устройства (чтение, запись), поступают также на выход 12 устройства. Аналогично производится диагностическая запись в ячейку накопителя диагностической информации, в случае, если исправить возникшую ошибку (сбой) не удалось и необходимо проверить оборудование на устойчивый отказ.

о Формирователь 5 циклов записи предназначен для формирования запускающих импульсов цикла записи, число и периодичность которых определяются алгоритмом работы устройства управления памятью в режиме контроля и/или диагностики. Запись выполняется в дефектную ячейку ОЗУ.

Формирователь 5 циклов записи выполняет функции, сходные с функциями формирователя 4 циклов чтения, П© ригналу начала записи диагности- j|§gKoft информации (например, запись. О и запись 1 или запись информации инверсной считанной), который п лступает с выхода 15 распределителя 14 устройства управления памяти ,, ренератор 49 начинает формирование цмпульсов, необходимых для работы счетчика 50, При этом счетчик 50 посыпает через коммутатор 51 на вход элемента ИЛИ 6 сигналы начала циклов записи. По окончании цикла записи диагностической информации счетчик 50 посылает сигнал блокировки работы генератора 49, и формирователь 5 циклов записи переходит в режим ожидания. Формирователь 5 ЦИКЛОВ записи может продолжить свою работу, если необходимо выполнить восстановление информации в дефектной ячейке. Формирователь 4 циклов чтения предназначе для формирования запускающих импульсов цикла , число и периодичность которых определяются алгоритмом работы устройства управленияПамяти в режиме контроля и/или диагностики. Чтение выполняется из дефектной ячейки ОЗУ. - По сигналу начала цикла многократ ного чтения, который поступает с выхода 14 распределителя 24 устройства . упра 5ления памяти, генератор 38 начи нает формирование счетных импульсов поступающих на вход счетчика 40, частота, длительность и количество которых зависят от характеристики ОЗЫ;. Запускающие импульсы на начало |диклов чтения р первого выхода счет чика 40 через коммутатор 43 и элеме ИЛИ 44 поступают на первый выход 36 формирователя 4 циклов чтения и далее - на вход коммутатора 3. После окончания цикла многократно го чтения на втором выходе счетчика 40 формируется сигнал окончания цикла многократного чтения, который бло кирует работу генератора 38 и разре шает прохождение запускающих импульсов через элемент И 39 на вход триг гера 41. Последний по сигналу начал цикла чтения диагностической информации, записанной в дефектную ячейк ОЗУ, формирует импульсы начала чтения, которые через элемент ИЛИ 44 поступают с выхода 37 на коммутатор 3. Управление работой коммутатора 43 и триггера 41 производится сигна лами, поступающими со входов 34 и 3 Предлагаемое устройство для управ ления памятью позволяет реализовать режимы автоматического контроля и диагностики, что приводит к существе венному увеличению надежности при минимагаьных затратах на оборудование. Формула изобретения 1. Устройство для управления памятью, содержащее дешифратор, генератор сигналов регенерации, выход которого соединен с первым входом, первого распределителя и входом первого счетчика, выход которого соединен с первым входом первого коммутатора, выход которого соединен с первым выходом, устройства, первый : выход первого распределителя соеди нен с вторым входом первого коммутатора, генератор сигналов, выход которого соединен с первыми входами первого и второго элементов И и с входом элемента НЕ, выход которого соединен с синхровходом первого триггера, выход которого соединен с вторым входом первого элемента И, третий вход которого соединен с выходом второго триггера, D-вход которого соединен с первым входом устройства, выход первого элемента И соединен с управляющим входом второго распределителя, первый выход которого соединен с четвертым входом первого элемента И, и вторым входом первого распределителя, второй выход второго распределителя соединен с D-входом третьего триггера, выход второго элемента И соединен с входом второго счетчика и с пятым входом первого элемента И, первый выход второго счетчика соединен с управлякицим входом третьего распределителя, а его выход соединен с первыми входами элементов И группы, второй выход второго счетчика соедиг/ нен с вторым входом второго элемента И, третий вход которого соединен с выходом третьего триггера, четвертый вход второго элемента И соединен с первым выходом второго коммутатора, ервый вход которого, второй вход регистра и первый вход дешифратора соединены с выходом третьего распределителя, второй вход устройства соединен с вторыми входами элементов И группы, .выходы которых соединены соответственно с первыми входами сумматоров по модулю два группы, выходы которых соединены с первыми входами регистра, выход которого соединен с BTOPIJM входом второго коммутатора, второй выход.которого соединен с вторым выходом устройства и вторым входом дешифратора, выходы которого соединены соответственно с вторыми входами сумматоров группы по модулю два, отличающееся тем, что, с целью повышения надежности, в него введены формирователи цикловчтения и записи и элемент ИЛИ, причем второй выход первого распределителя соединен с первыми входами формирователей циклов чтения и записи, первые выходы которых соединены с входами, элемента-ИЛИ, выход которого соединен с вторым вхо дом первого триггера и с шестым входом первого элемента И, третий выход второго распределителя соединен с вторым входом формирователя циклов чтения, а четвертый выход второго распределителя соединен с вторым вхо дом формирователя циклов записи, вто рой выход которого соединен с треТьим входом первого распределителя второй выход формирователя циклов чт ния соединен с третьим входом первог коммутатора. 2. Устройство по п.1у отличающееся тем, что формирователь цикло;9 чтения содержит генератор циклов, счетчик, триггер, коммутатор, два элемента ИЛИ, элемент И, причем к первому входу формировате;ля подключен вход триггеру и первый 1вход коммутатора, а к второму вхо|ду.формирователя подключены первые входы генератора циклов и элемента И вторые входы которых соединены с пер BfcM входом первого элемента ИЛИ и .первым выходом счетчика, второй выход соединен с ВТОЕ«М входо к МФ1утатора, выход которого соединен с первьм входом второго элемента |ИЛИ, выход которого соединен с втрj)bw выходом формирователя, первый Ьыход которого соединен с выходом первого элемента ИЛИ, второй вход которого и второй вход второго элемента ИЛИ соединены с выходом триггера, вход которого соединен с выходом элемента И, выход генератора циклов соединен с входом счетчика. 3. Устройство ПОП.1, отличающееся тем, что формирователь циклов записи содержит генератор циkлoв, счетчик, коммутатор, причем к первому и второму входам формирователя подключены соответственно первые входы генератора циклов и коммутатора-, первый и второй выходы которого соединены с первым и .вторым шлходами формирователя, выход генератора циклов соединен с входом счетчика, первый и второй выходы которого соединены с вторыми входами генератора циклов и коммутатора. Источники информации, принятые во внимание при. экспертизе 1.Каган Б.М. Электронные вычислиельные машины и систекы. М., Энергия, 1979, с.431-436. 2.Авторское свидетельство СССР 556444, кл. G-06 F 13/06, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

Ш

Ц9

-Ч

ts

47

М

Авторы

Даты

1982-09-30—Публикация

1980-07-02—Подача