(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1173446A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Запоминающее устройство | 1982 |

|

SU1056266A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Запоминающее устройство | 1978 |

|

SU746745A1 |

| Вычислительная система | 1990 |

|

SU1709331A1 |

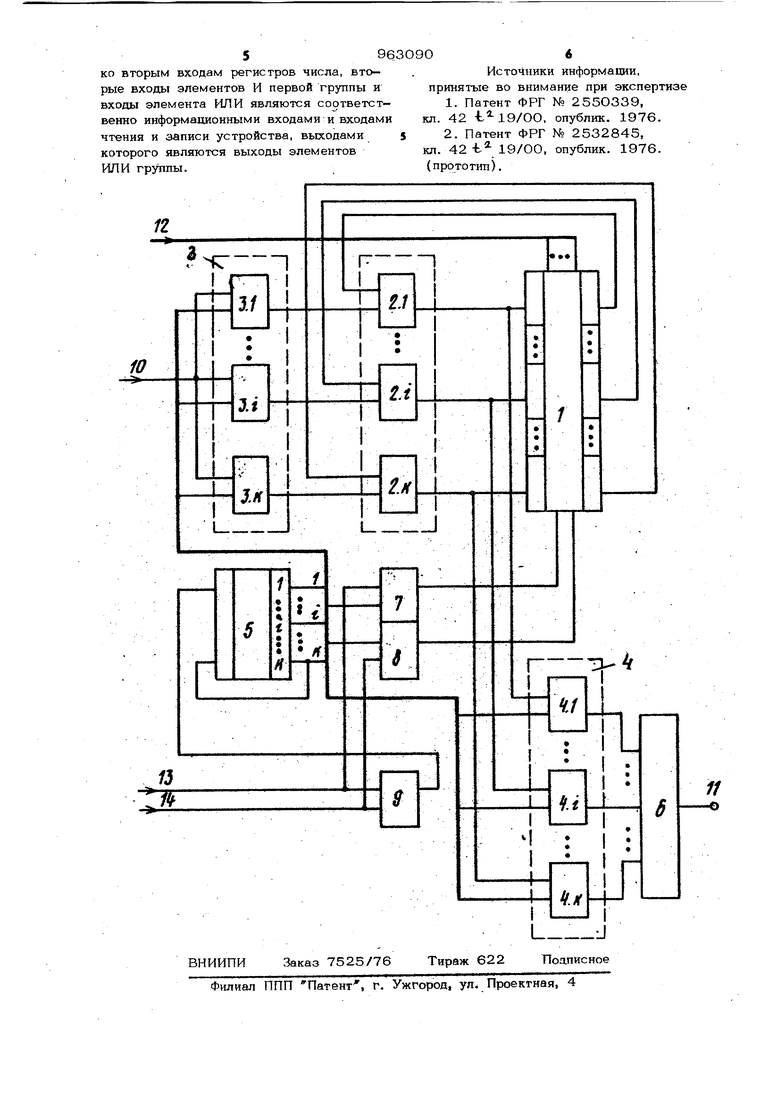

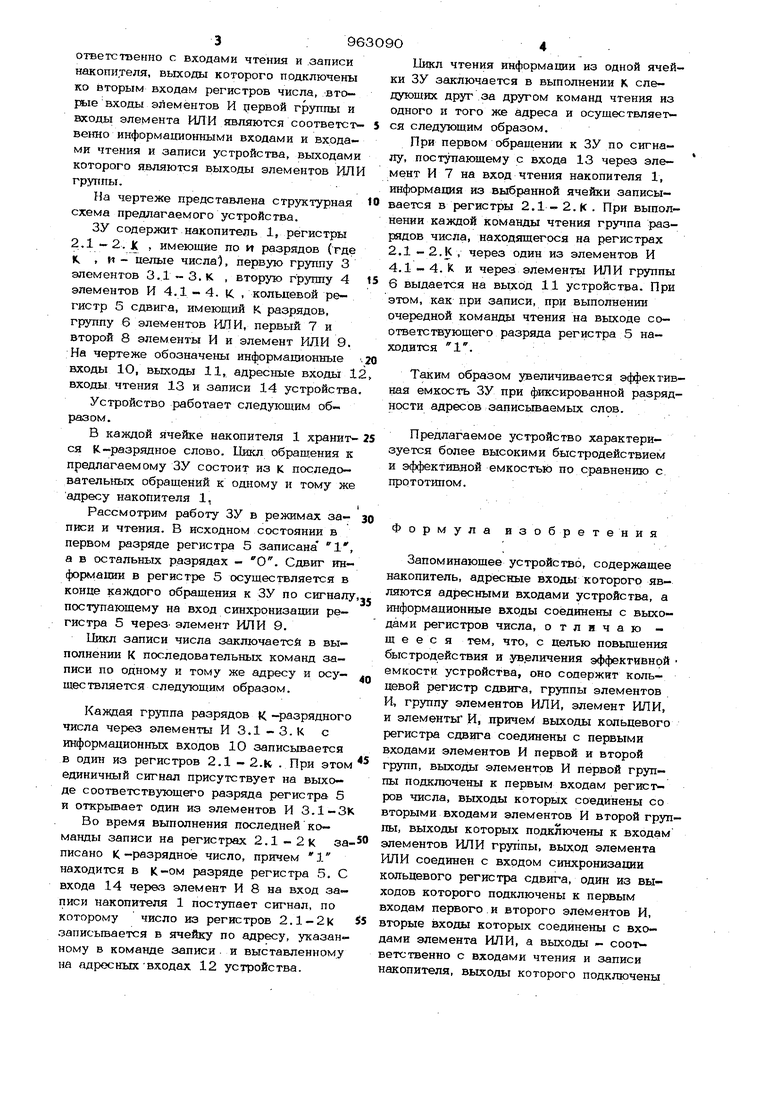

. Изобретение относится к запоминающим устройствам (ЗУ). Известно ЗУ, которое состоит из буферного накопителя, снабженного узлами, выдающими данные.в течение короткого рабочего цикла, и главного запоминающего блока с относительно длинным рабочим циклом f 1 Недостаток данного ЗУ - невозможност увеличения его эффективной емкости. Наиболее близким к предлагаемому является ЗУ, содержащее основную память большой емкости с больщим временем доступа и буферную память малой емкостп 2 Недостатками известного ЗУ являются невозможность увеличения его емкости при заданной разрядности адресной шины ЦВМ и невысокое быстродействие, обусловленное временем доступа к буферной памяти. Цель изобретения - повышение быстродействия и увеличение эффективной емкости устройства. Поставленная цель достигается тем, что в запоминающее устройство, содер- жа1цее накопитель, адресные входы которого являются адресными входами устройства, а информационные входы соединены с выходами регистров числа, введены кольцевой регистр сдвига, группы элементов И, группа элементов ИЛИ, элемент ИЛИ и элементы И, причем выходы кольцевого регистра сдвига соединены с первыми входами элементов И первой и второй групп, выходы элементов Vi первой группы подключены к первым входам регист ров числа, выходы которых соединены со вторыми входами элементов И второй группы, выходы которых подключены к входам элементов ИЛИ группы, выход элемента ИЛИ соединен с входом синхронизации кольцевого регистра сдвига, од- , ни из выходов которого подключены к первым входам первого и второго элементов И, вторые входы которых соединены с входами элемента ИЛ1.-1, а выходы - соответственно с входами чтения и записи накопителя, выходы которого подключены ко вторым входам регистров числа, вторые входы элементов И цервой группы и входы элемента ИЛИ 51вляются соответственно информационными входами и входами чтения и записи устройства, выходами которого являются выходы элементов ИЛИ группы. На чертеже представлена структурная схема предлагаемого устройства. ЗУ содержит накопитель 1, регистры 2.1 -2. К , имеющие по и разрядов (где К, , и - целые числа), первую группу 3 элементов 3.1 - 3. К , вторую группу 4 элементов И 4.1 - 4. К. , кольцевой регистр 5 сдвига, имеющий К разрядов, группу 6 элементов ИЛИ, первый 7 и второй 8 элементы И и элемент ИЛИ 9. На чертеже обозначены информационные входы Ю, выходы 11, адресные входы 1 входы чтения 13 и записи 14 устройства Устройство работает следующим образом. В каждой ячейке накопителя 1 хранится К-разрядное слово. Никл обращения к предлагаемому ЗУ состоит из к последовательных обращений к ошюму и тому же адресу накопителя 1, Рассмотрим работу ЗУ в режимах за- писи и чтения. В исходном состоянии в первом разряде регистра 5 записана 1, а в остальных разрядах - О. Сдвиг информации в регистре 5 осуществляется в конце каждого обращения к ЗУ по сигналу поступающему на вход синхронизации регистра 5 череЗ элемент ИЛИ 9. Никл записи числа заключаетсй в выполнении К последовательных команд записи по одному и тому же адресу и осуществляется следующим образом. Каждая rpjTina разрядов К -разрядного числа через элементы И 3.1 - 3. К с информационных входов 10 записывается в один из регистров 2.1 - 2.К .При этом единичный сигнал присутствует на выходе соответствующего разряда регистра 5 и открьгоает один из элементов И 3.1-ЗК Во время выполнения последней команды записи на регистрах 2.1 -2к записано к -разрядное число, причем находится в К-ом разряде регистра 5. С входа 14 через элемент И 8 на вход записи накопителя 1 поступает сигнал, по которому число из регистров 2.1 -2к записьюается в ячейку по адресу, указанному в команде записи и выставленному на адрес ныос входах 12 ус тройс тва. 96 О4 Цикл чтения информации из одной ячейки ЗУ заключается в выполнении К следующих друг за другом команд чтения из одного и того же адреса и осуществляется следующим образом. При первом обращении к ЗУ по сигналу, поступающему с входа 13 через элемент И 7 на вход чтения накопителя 1, информация из выбранной ячейки записывается в регистры 2.1-2. К. При выполнении каждой команды чтения группа разрядов числа, находящегося на регистрах 2.1 - 2. К , через один из элементов И 4.1-4. fc и через элементы ИЛИ группы 6 выдается на выход 11 устройства. При этом, как при записи, при выполнении очередной команд чтения на выходе соответствующего разряда регистра 5 находится 1. Таким образом увеличивается эффективная емкость ЗУ при фиксированной разрядности адресов записываемых слов. Предлагаемое устройство характеризуется более высокими быстродействием и эффективной емкостью по сравненшо с прототипом. Формула изобретения Запоминающее устройство, содержащее накопитель, адресные входьг которого являются адресными входами устройства, а информационные входы соединены с выходами регистров числа, отличаю - щ е е с я тем, что, с целью повьпиения быстродействия и ув.еличения эффективной емкости устройства, оно содержит кольцевой регистр сдвига, группы элементов И, группу элементов ИЛИ, элемент ИЛИ, и элементы И, причек выходы кольцевого регистра сдвига соединены с первыми входами элементов И первой и второй групп, выходы элементов И первой группы подключены к первым входам регистров числа, выходы которых соединены со вторыми входами элементов И второй группы, выходы которых подключены к входам элементов ИЛИ группы, выход элемента ИЛИ соединен с входом синхронизации кольцевого регистра сдвига, один из выходов которого подключены к первым входам первого. и второго элементов И, вторые входы которых соединены с входами элемента ИЛИ, а выходы - соот ветственно с входами чтения и записи накопителя, выходы которого подключены

ко вторым входам регистров числа, вторые входы элементов И первой группы и входы элемента ИЛИ являются соответственно информационными входами и входами чтения и записи устройства, выходами

которого являются выходы элементов ИЛИ группы.

Источники информации, принятые во внимание при экспертизе

(npoTOTim).

Авторы

Даты

1982-09-30—Публикация

1981-03-20—Подача