2. Устройство по п. 1, отличающееся тем что блок анализа информации содержит элементы НЕ

.и элементы П-НБ, причем выходы первого и второго элементов И-НЕ подключены к входам третьего элемента И-НЕ, выход которого является выходом бло,ка, первые входы первого и второго элементов И-НЕ соединены с выходеа т

первого и второго элементов НЕ соответственно, второй вход первого элемента И-НЕ и вход второго элемента НЕ объединены и являются одним, и вхопов . доугим вхпдом KOTODoro является объединенные второй вход второго элемента И-НЕ и вход первого эле мента НЕ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1980 |

|

SU959166A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство | 1985 |

|

SU1298800A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| Запоминающее устройство с исправлением информации в отказавших разрядах | 1986 |

|

SU1317487A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для контроля ввода-вывода | 1980 |

|

SU896626A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопители информации, входы которых подключены к выходам адресного блока, дешифратора, регистра команд и блока ввода информации, 5 / .:. j t i входы которых являются адресными, управляющими и информационнйг-ш входами устройства,, а выходы накопителей информации соединены с одними из входов блока вывода информации, выходы которого являются информационными выходами устройства, о т л и ч а ю щ е ее я тем, что, с целью упрощения устройства и повьш ения его надежности за счет обнаружения етиибок, в нем выходы блока ввода информации соединены с другими входами блока вывода информации, а также введен блок анализа информации, входы которого подключены к информационным входам и выходам устройства, а выход является управляющим выходом устройства..

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах (ЗУ).

Известно ЗУ, содержащее в каждом разряде выходной формирователь, микросхемы памяти, буферные элементы, выходы которых соединены с соответствующими входами микросхем пагляти, выходы которых объединены между собой и соединены с входом выходного формирователя ij .

Это устройство недостаточно надежно, поскольку возможна запись ложной информации при неисправностях информационных цепей записи и возможно обращение на чтение при неисправных информационных цепях считывания.

Наиболее близким техническим реше ием к изобретению является ЗУ,каждый разряд которого включает микросхемы памяти, буферные элементы адреса, буферный элемент команды, дешифратор выборки, выходы которого соединены с входами выборки микросхем памяти, одноименные входы адреса которых объединены между собой и соединены с выходами буферных элементов адреса, йходы команды микросхем памяти объединены собой и соединены с выходом буферного элемента команда, выходной буферный элемент, входной буферный элемент, выход которого соединен с.объединенными между собой информационными входаг1и микросхем памяти, выходы которых объединены между собой и соединены с входом выходного буферного элемента 2 .

Такое ЗУ также недостаточно надежно, посколйку возможна запись ложной информации при неисправных информационных цепях записи,.и возможно обращение на чтение при уже неисправных информационных цепях считывания.

Для построения ЗУ большой емкости наращиванием однотипных ЗУ иногда используется последовательное соединение ЗУ. Адресные и командные сигналы подаются на все ЗУ параллельно а одноименные разряды всех ЗУ соединяются последовательно. В режиме записи записываемая информация подается на информационные входы первого ЗУ. Б режиме чтения считанная информация снимается с информационных выходов последнего ЗУ. Выбор нужного ЗУ осуществляется с помощью специального дешифратора, управляемого старшими разрядами регистра адреса.

В такой системе в каждом невыбранном ЗУ обеспечивается трансляция сигналов с информационных входов на информационные выходы, а в выбранном ЗУ организуется поступление считанных сигналов в общую цепь прохождения информации..

Недостатком указанного ЭУ большой емкости являются большие затраты оборудования для ррганиэации трансляции сигналов с информационных входов на информационные выводы ЗУ и для организации поступления считанных сигналов в общую цепь прохождения информации.

Целью изобретения является упрощение устройства и повышение его надежности за счет обнаружения ошибок

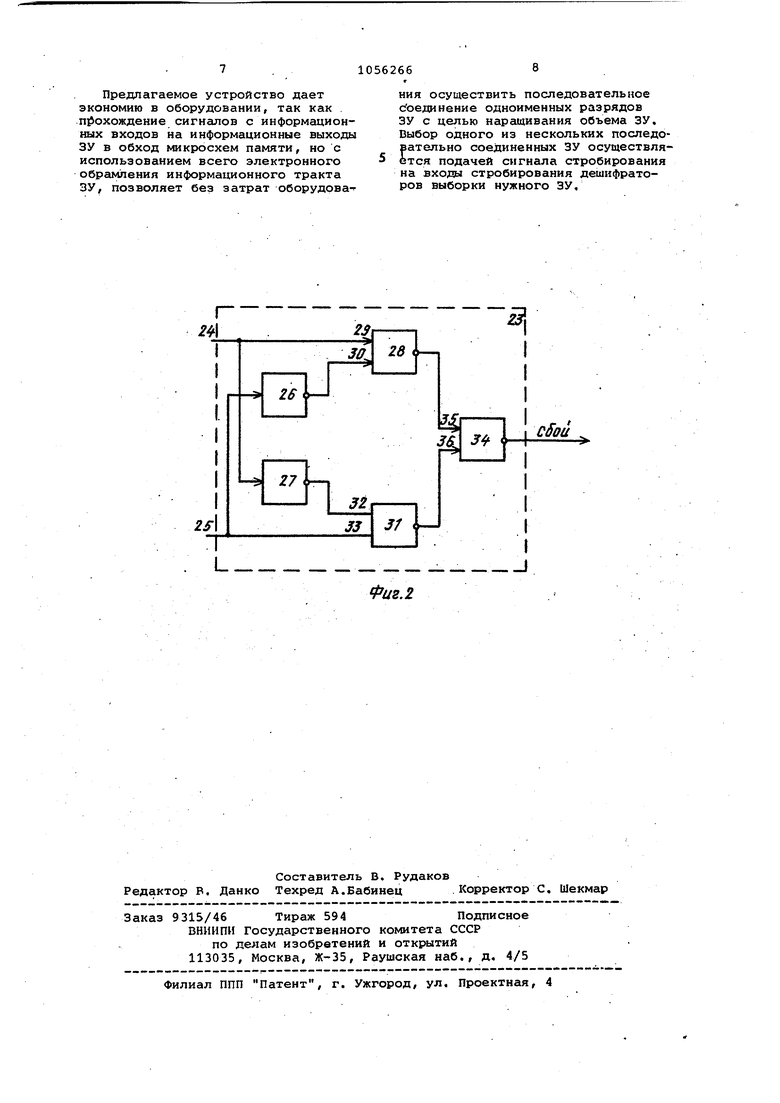

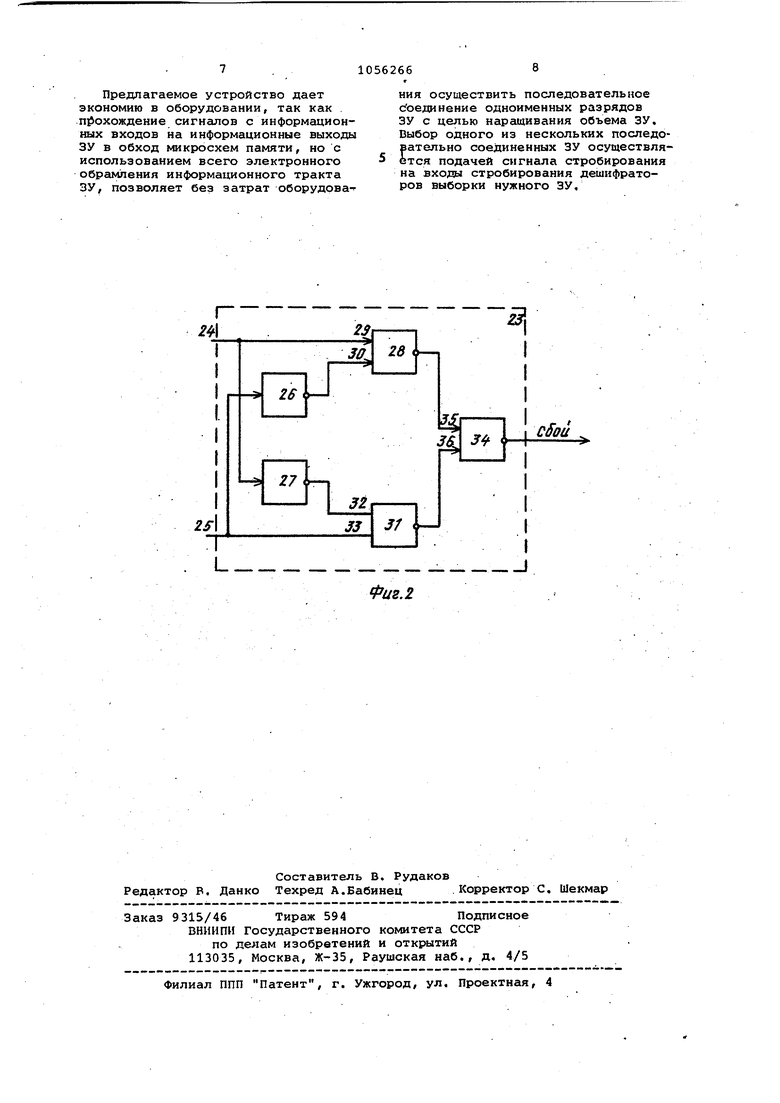

Поставленная цель достигается тем, что в запоминающем устройстве, содержащем накопители информации, входы которых подключены к выходам адресного блока, дешифратора, регистра команд и блока ввода информации, входы которых являются адресными, управляющими и информационными входами устройства, а выходы накопителей информации соединены с одними из входов блока вывода информации, выходы которого являются информаЕционными выходами устройства, выходы блока ввода информации соединены с другими входами блока вывода информации, при этом в устройство введен блок анализа информации, ВХоды которого подключены к информационным входам и выходам устро,йства, а выход является управляющим выходом устройства. Кроме того, блок анализа информации содержит элементы НЕ и элементы И-НЕ, причем выходы первого и второго элементов И-НЕ подключены к входам третьего элемента И-НЕ, выход которого является выходом блока первые входы первого и второго элементов И-НЕ соединены с выходами первого и второго элементов НЕ соответственно, второй вход первого элемента И-НЕ и вход второго элемента НЕ объединены и являются одним и входов блока, другим входом которого являются объединенные второй вход второго элемента И-НЕ и вход первого элемента НЕ. На фиг. 1 изображена функциональная схема ЗУ; на фиг. 2 - то же, . блока анализа информации. Устройство (фиг. 1) содержит накопители .инфррмации, выполненные на микросхемах 1 и 2 памяти, с адресны ми 3-6,, командными 7 и 8 и информационными 9 и 10 , входами 11 и 12 выборки и выходами 13 и 14, адресный блок, состоящий из буферных элементов 15 и 16 адреса,- ре- гистр 17 команд, блок вывода информации, выполненный в виде элемента И-НЕ 18 и имеющий входы 19 и 20, блок ввода информации, выполненный в виде элемента НЕ 21, дешифратор 2 и блок 23 анализа информации с входами 24 и 25. Несколько Таких устройств (фиг.1 входят в состав многоразрядного накопителя. В свою очередь, несколько многоразрядных накопителей могут обеспечить наращивание информационного объема ЗУ до требуемой величин Блок 23 содержит первый 26 и вто рой 27 элемент НЕ, первый элемент И-НЕ 28 с входами 29 и 30, второй элемент И-НЕ 31 с входами 32 и 33 и третий элемент И-НЕ 34 с входами 35 и 36. Устройство работает в трех режимах: Запись, Чтение и Хранение В режиме Запись на адресные входы буферных элементов 15 и 16 и дешифратора 22 поступает адресный код, на управляющий вход, дешифрато ра 22 поступает сигнал разрешения выборки, на вхьд регистра 17 поступает сигнал записи, а на вход элемента 21 - записывается информация, которая может быть представлена низ «сим или высоким уровнем. Запись информации происходит в ту микросхему или 2 памяти, на входе 11 или 12 ко торой находится разрешающий потенци с одного из выходов дешифратора 22. В рехшме Запись на входе 19 элемента И-НЕ 18 всегда находится высокий уровень с выходов 13 и 14 гликросхем 1 и 2 памяти, разрешающий прохождение сигнала, поступившего на его вход 20. Инвертированный сигнал с выхода элемента И-НЕ 18 поступает на вход 24 блока 23, поэтому на входах 24 и 25 блока 23 при исп авных разрядных цепях всегда имеются одинаковые уровни, а на информшдионном выходе устройства всегда имеется тот же уровень, что и на его информационном входе, т-.е. в режиме записи обеспечивается трансляция через ЗУ входной информации. Пусть на входах 24 и 25 блока 23 находятся высокие уровни, которые поступают «а входы элементов НЕ 26 и 27, а также на входы 29 и 33 элементов И-НЕ 28 и 31. На выходах элементов НЕ 26 и 27 имеются низкие уровни, которые поступают на . входы 30 и 32 элементов И-ПЕ 28 и 31 и независимо от уровней на входах 29 и 33 тех же элементов создают на их выходах высокие уровни. При совпадении высоких уровней на входах 35 и 36 элемента И-НЕ 34 на его выходе имеется низкий уровень. Пусть на входах 24 и 25 блока 23 находятся низкие уровни. Можно показать , что на выходе блока -будет также низкий уровень. Если входная информация представлена низким уровнем, то при неисправности элемента НЕ.21 и цепи на его выходе на выходе блока 23 находится высокий уровень, СИГНс1ЛИЗИруЮй1ИЙ о неисправности цепей записи. Неисправности элемента НЕ 21 и цепи на его выходе, создающие портоянный низкий уровень на входе, 24 блока 23 приводят к совпадению сигналов на входах 24 и 25 блока 23 и, следовательно, к отсутствию сигнала сбоя. Однако запись информгщии происходит правильно, так как неисправности не вызывают изменения информации на информационных входах 9 и 10 микросхем 1 и 2 памяти. Если в.ходная информация представлена высоким уровнем то неисправности элемента НЕ 21 и цепи на его выходе, создающие постоянный высокий уровень на входе 24 блока 23, приводят к совпадению сигналов на входах 24 и 25 блока 23 и, следовательно, к отсутствию сигнала сбоя. Однако происходит запись верной информации, так как неисправности не вызывают изменения информации на информационных входах 9 и 10 (микросхем 1 и 2 памяти. Неисправности элемента НЕ 21 и цепи на его выходе, создающие постоянный низкий уровень на входе 24 -блока 23, приводят к несовпадению сигналов на входах 24 и 25 блока 23.. Низкий уровень, поступакядий на вход 24 блока 23, приводит к появл нию на выходе элемента НЕ .27 высок го уровня, который поступает на вх 32 элемента И-НЕ 31. Совпадение на входах 32 и 33 элемента И-НЕ 31 высоких уровней приводит к появлению на его выходе низкого уровня, торый поступает на вход 36 элемент И-НЕ 34. Независимо от уровня сигн на входе 35 этого элемента на его выходе имеется высокий уровень, си нализирующий о неисправности цепей записи. ,; Неисправности элемента И-НЕ 18 или цепи на его выходе, которые со дают несовпадение сигналов на входах 24 и 25 блока 23, приводят к выработке сигнала сбоя. Однако во всех случаях происходит запись аер йой информации, а сигнал сбоя указывает на неисправность цепей считывания, , . Для более полного контроля разрядных цепей в цикле загписи можно после записи информации в том же цикле изменить входной уровень на инверсный и дополнительно проконтр лировать всю разрядную цепь, но уж без подачи управляющего сигнала дешифратора 22, .т.е. без. записи новой информации. ... ... В.режиме Чтение на адресные входы буферных элементов 15 и16 дешифратора 22 поступает адресный код, на управляющий вход дешифрато ра 22 поступает сигнал разрешения выборки/ на ВХОД регистра 17 поступа е.т сигнал чтения.. Чтение информации происходит из той г-мкросхемы 1 или 2 памяти, на входе 11:или 12 которой имеется раз решающий сигнал с одного из выходов дешифратора 22. Считанная информаци :В зависимости от выбранной микросхе мы 1 или 2 памяти появляется на выходе 13 или 14 и поступает на вход 19 элемента И-НЕ 18. Так как считанная информация может быть представлена .низким или высоким уровнем, то для того, чтобы потенциал на входе 20 э 1еМента И-НЕ 18 не влиял на прохождение считанного сигнала, он доллсен быть высоки для чего на вход элемента НЕ 21 в р ежиме чтения необходимо подать низ кий уровень, который через элемент НЕ 21 поступает на вход 20 элемента И-НЕ 18. На входах 24 и 25 блока 23 мо- гут быть разные уровни, т.е. выдается сигнал сбоя, однако в режиме Чтение он должен игнорироваться. При последовательном соединении нескольких ЗУ считанная информация может поступить на вход элемента НЕ. 21 с другого ЗУ, тогда эта информация проходит с входа на выход данного ЗУ аналогично тому, как в режиме Запись, так как при отсутствии обращения к данному ЗУ на выходах 13 и 14 микросхем 1 и 2 паЫяти имеются высокие уровни. В режиме Хранение на адресные входы буферных элементов 15 и 16 и дешифратора 22, на вход регистра 17 команд можно подать любые уровни. Дешифратор 22 не долхсен выдавать разрешак|ций уровень, чтобы не было обращения в какой-либо микросхеме 1 и 2 памяти. Это достигается тем, что не подается сигнал разрешения на управляющий вход дешифратора 22. Уровень, поступивший на вход 25 блока 23 и н,а вход э лемента НЕ 21, проходит через этот элемент и поступает на вход 20 элемента И-НЕ 18. Так как в этом режиме нет обращения к накопителю, то на выходах 13 и 14 микросхем 1 и 2 памяти имеется высокий уровень, который разрешает прохождение сигнала с входа 26 элемента И-НЕ 18 на его.выход, а оттуда на вход 24 блока 23, т.е. в режиме Хранение возможен контроль всей разрядной цепи так же как и в режиме Запись. . Технико-экономический эффект предлагаемого устройства по сравнению с Изве.стным заключается в повышении надежности устррйстваг упрощении диагностики и- экономии оборудования. . Предлагаемое устройство обладает более высокой надежностью, так как введен контроль записываемой информации и информационных цепей записи вплоть до информационных входов микросхем памяти, введен контроль информационных цепей считывания в цикле записи. Использование предлагаемого ЗУ в вычислительной системе позволяет: ввести контроль иЭДормационных цепей записи и считывания без обращения ЗУ на запись или считывание, т.е. в режиме хранения информации, . подавая разные уровни на информационные входы и контролируя сигналы на информационных выходах; многократной записью информации в случае сбоя или отказа отделить сбой от отказа, так как случайный сбой при повторной записи не повторится. В случае использования в процессоре кода предлагаемое устройство позволяет отличить неисправность или сбой элементов хранения информации от неисправностей информационных цепей записи и считывания, что значительно упрощает диагностику и поиск неисправностей.

Предлагаемое устройство дает экономию в оборудовании, так как . прохождение сигналов с информационных входов на информационные выходы ЗУ в обход микросхем памяти, но с использованием всего электронного обрс1мления информационного тракта ЗУ, позволяет без затрат оборудовав

ГI.

ния осуществить последовательное боединение одноименных разрядов ЗУ с целью наращивания объема ЗУ. Выбор одного из нескольких последовательно соединенных ЗУ осуществляется подачей сигнала стробирования на входы стробирования дешифраторов выборки нужного ЗУ,

Щ т

cSoa

3

Фиг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3967251, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Сдвижной печной патрубок | 1929 |

|

SU19761A1 |

| Полупроводниковые запоминающие устройства | |||

| М., Радио и связь, 1981, с | |||

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

Авторы

Даты

1983-11-23—Публикация

1982-08-17—Подача