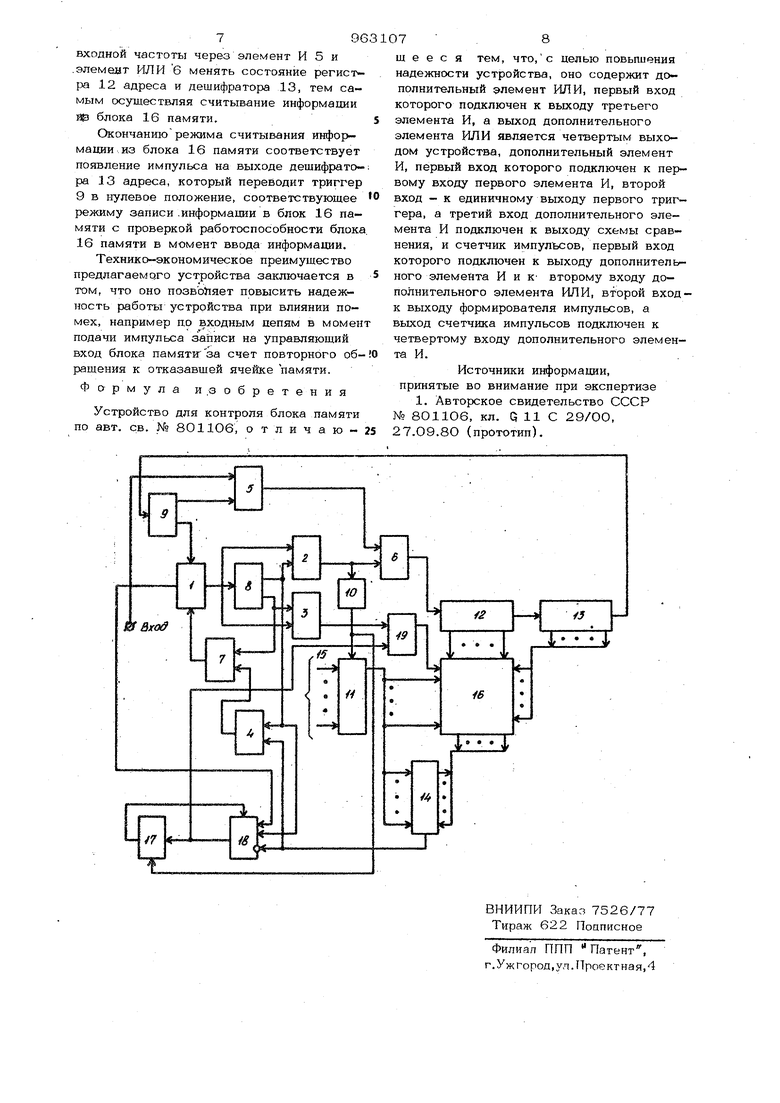

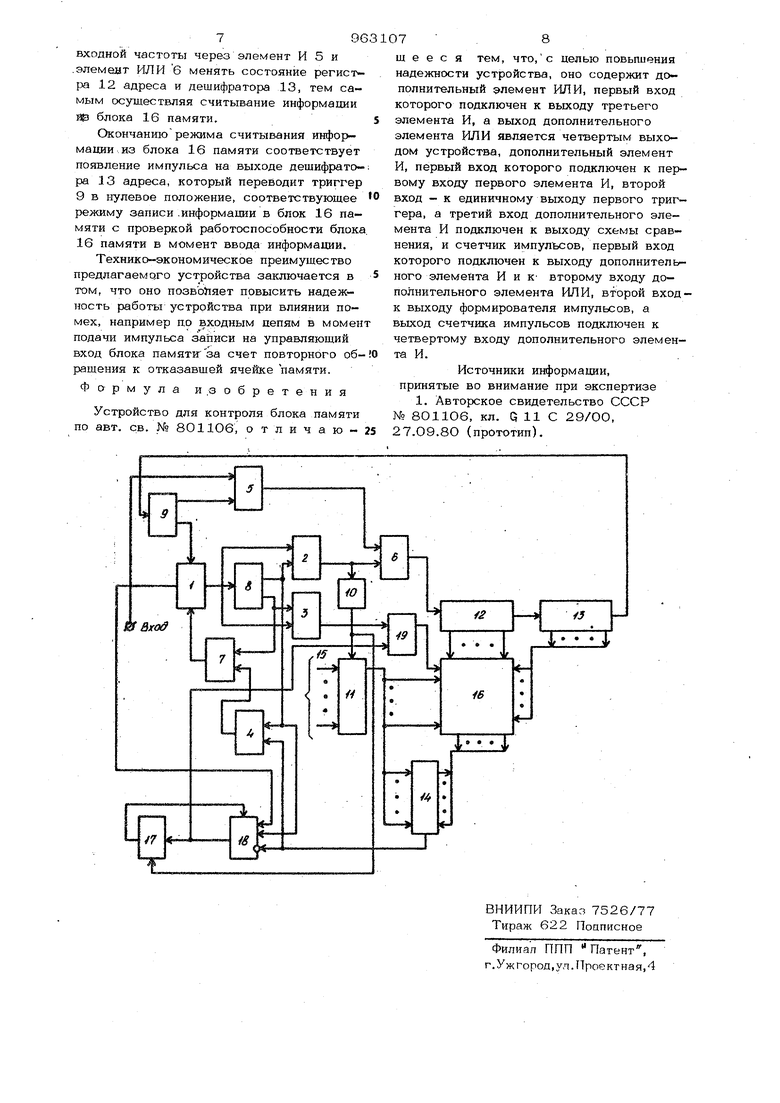

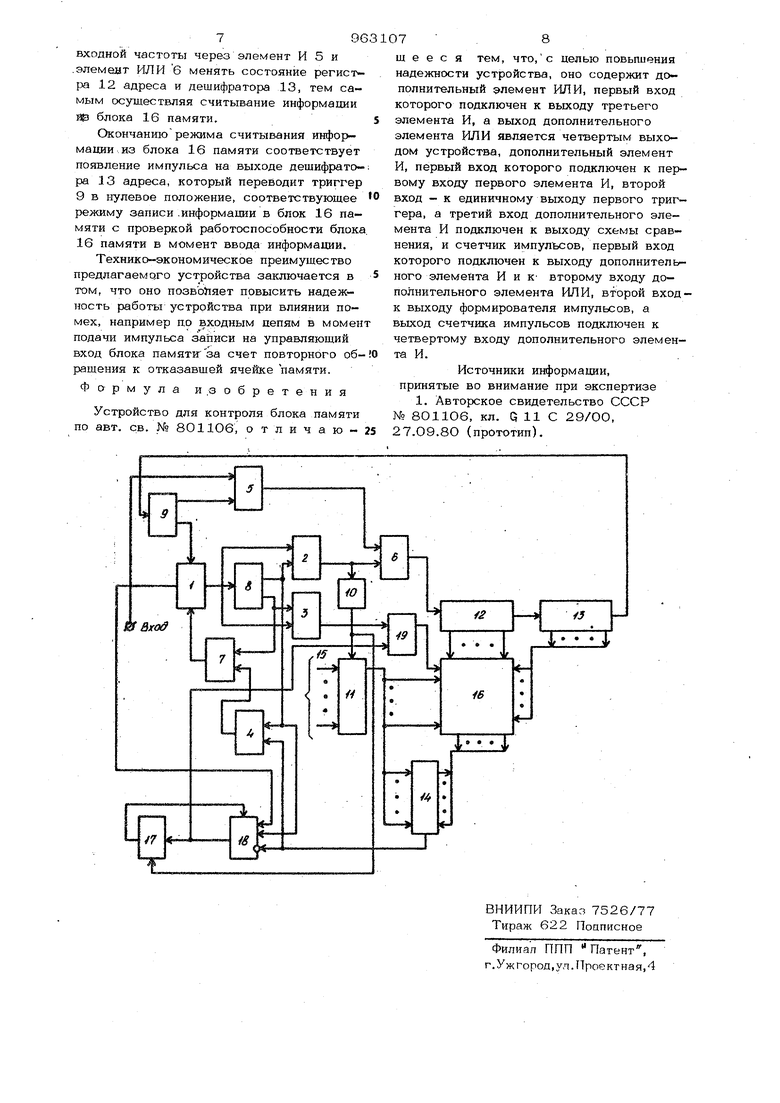

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПАМЯТИ Изобретение относится к вычислительной технике и может быть использовано в факсимильной технике связи. По основному авт. св. № 801106 известно устройство для контроля блока памяти, содержащее входной регистр, регис адреса, дешифратор адреса, схему сравнения и первый элемент ИЛИ, выход которого подключен ко входу регистра адреса, одни из выходов которого соединены с первыми выходами устройства, а другой выход подключен ко входу дешифратора адреса, одни из выходов которого соединены со вторыми выходами устройства, выходы входного регистра подключены к третьим выходам устройства и к одним из входов схемы сравнения, другие входы которой соединены с первыми входами устройства, второй элемент ИЛИ, пять элементов И, два триггера и форми- рователь импулн,сов, причем второй вход устройства подключен к первым входам первого и пятого элементов И, выход пер вого элемента И соединен с первыми вхо дами второго и третьего элемента И, и счетным входом первого триггера, нулевой выход которого подключен ко второму входу третьего элемента И и первому входу второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, единичный выход первого триггера подключен к первому входу четвертого элемента И и второму входу второго элемента И, выход которого соединен с первым входом пс;рвого элемента ИЛИ и входом формирователя импульсов, выход которого подключен к одному из входов входного регистра, другие входы которого соединены с шинами ввода информации, выход схемы сравнения подключен ко второму входу четвертого элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, другой выход дешифратора адреса подключен к счетному входу второго триггера, нулевой и единичный выходы которого соединены соответственно с третьим входом первого и вторым входом пятого элемента И, выход пятого элемента И пошслючен ко вто рому входу первого элемента ИЛИ, выход третьего элемента И соединен с четвертым выходом, устройства fl . Недостатком известного устройства является возможность ошибочного определения адреса неисправной ячейки памяти под воздействием случайной помехи, например по входным цепям в момент поступления импуль са записи, 11ель изобретения - повышение надежности устройства при , наличии помех за счет повторного обращения к отказавшей ячейке памяти. Поставленная цель достигается тем, что в устройство для контроля блока памяти, содержащее входной регистр, регис адреса, дешифратор адреса, схему сравнения, первый элемент ИЛИ-, выход которог подключен ко входу регистра адреса, одни из выходов которого соединены с первым выходами устройства, а другой выход под ключен ко входу дешифратора адреса, одн из выходов которого соединены со вторыми выходами устройства, выходы входног регистра подключены к третьим выходам устройства и к одним из входов схемы сравнения, другие входы которой соединены с первыми входами устройства, второй элемент ИЛИ, пять элементов И, два триг гера и формирователь импульсов, причем второй вход устройства подключен к. первым входам первого и пятого элементов И, выход первого элемента И соединен с первыми входами второго и третьего эле- ментов И и счетным входом первого триг гера, нулевой выход которого подключен ко второму входу третьего элемента И и первому входу второго элемента ИЛИ, вы ход которого срединен со вторым входом первого элемента И, единичный выход пер вого триггера подключен к первому входу четвертого элемента И и второму входу второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ и входом формирователя импульсов, выход которого подключен к одному из входов входного регистра, другие входы которого соединены с шинами ввода информации, выход схемы сравнения подключен ко второму Входу четвертого элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, другой выход дешифратора адреса подключен к счетному входу второго триггера, нулевой и единичный выходы которого соединены соответственно с третьим входом первого и вторым входом пятого элемен та И, выход пятого элемента И подклю- чен ко второму входу первого элемента ИЛИ дополнительно введены дополнительный элемент ИЛИ, первый вход которого подключен к выходу третьего элемента И, а выход дополнительного элемента ИЛИ 5шляется четвертым выходом устройства, дополнительный элемент И, первый вход которого подключен к первому входу первого элемента И, второй вход - к единичному выходу первого триггера, а третий вход дополнительного элемента И подклю1- чен к выходу схемы сравнения, и счетчик импульсов, первый вход которого подключен к выходу дополнительного элемента И и ко второму входу дополнительного элемента ИЛИ, второй вход - к выходу формирователя импульсов, а выход счетчика импульсов подключен к четвертому входу дополнительного элемента И. На чертеже представлена блок-схема предлагаемого устройства. Устройство для контроля блока памяти содержит элементы И 1 - 5, элементы ИЛИ 6 и 7, триггеры 8 и 9, формирователь 1О импульсов , входной , регистр 11, регистр 12 адреса, дешифратор 13 адреса, схему 14 сравнения, шины 15 ввода информации, блок 16 памяти, счетчик 17 импульсов, дополнительный элемент И 18 и дополнительный элемент ИЛИ 19. Выход первого элемента ИЛИ 6 подключен ко входу регистра 12 адреса, одни из выходов которого соединены с первыми выходами устройства, а другой выход подключен ко вхрду дешифратора 13 адреса, одни из выходов которого соединены со вторыми выходами устройства. Выходы входного регистра 11 подключены к третьим выходам устройства и к одним из входов схемы 14 сравнения, другие входы которой соединены с первыми входами устройства. Второй вход устройства подключен к первым входам первого 1 и пятого 5 элементов И. Выходы первого элемента И 1 соединены с первыми входами второго 2 и третьего 3 элементов И и Счетным входом первого триггера 8, нулевой выход которого подключен ко второму входу третьего элемента И 3 и первому входу второго элемента ИЛИ 7, выход которого соединен со вторым входом первого элемента И 1. Единичный выход первого триггера 8 подключен к первому входу четвертого элемента И 4 и второму входу второго элемента И 2, выход которого соединен с первым входом первого элемента ИЛИ 6 и входом формирователя 10 импульсов, выход которого подключен к одному из входов входного регистра 11.

входы которого соединены с шинами 15 ввода информации. Выходы схемы 14 сравнения подключены ко второму входу четвертого элемента И 4, выход которого соединен со вторым входом второго элемента ИЛИ 7. Другой выход дешифратора 13 адреса подключен к счетному входу второго триггер)а 9, нулевой и единичный выходы которого соединены соответственно с третьим входом перво- го 1 и вторым входом пятого 5 элемента И. Выход пятого элемента И 5 подключен ко второму входу первого элемента ИЛИ 6. Выход третьего элемента И 3 соединен с первым входом дополнительного элемента ИЛИ 19, выход которого подключен к четвертому выходу устройства. Второй вход устройства подключен к первому входу дополнительного элемента И 18, единичный выход первого триггера 8 подключей ко второму входу дополнительного элемента И 18, третий вход которого подключен к выходу схемы 14 сравнения, выход дополнительного элемента И 18 подключен ко второму входу дополни- тельного элемента ИЛИ 19 и к первому входу счетчика 17 импульсов, выход которого подключен к четвертому входу дополнительного элемента И 18, выход формирователя 10 импульсов подключен ко второму входу счетчика 17 импульсов. Информационные входы и выходы контролируемого блока 16 памяти подключены соответственно к первому, второму и третьему выходам и к первому входу устройства, а управляющий вход записи информации - к четвертому выходу устройства. Устройство работает следующим образом. В исходном состоянии триггеры 8 и 9 установлены в нулевое состояние. Регистр 12 адреса и дешифратор 13 адреса устанавливают адрес исходных ячеек блока 16 памяти. Во входной регистр 11 введена исходная информация для записи в блок 16 памяти. На второй вход устройства поступает первый импульс входной частоты, который проходит через элемент И 1 на счетный вход триггера, 8и через элемент И 3 - на управляющий вход записи информации блока 16 памяти, записывая в него информацию с выходом входного регистра 11. Задний фронт первого входного импульса переводит триггер 8 в единичное состояние. Отсутствие сигнала на управляющем входе записи информа- иии блока 16 памяти при наличии выходных адресов с регистра 12 адреса и дещифратора 13 адреса соответствует режиму вьщачи информации для блока 16 памяти. Информация с блока 16 памяти поступает на вход схемы 14 сравнения, где сравнивается с информацией на входном регистре 11 и, в случае их совпадения, с выхода схемы 14 сравнения через элемент И 4 и элемент ИЛИ 7 поступает потенциал разрешения на элемент И 1 для прохождения второго импульса входной частоты. Второй импульс входной частоты поступает на счетный вход триггера 8, через элемент И 2 - на вход формирователя 10 импульсов и через элемент ИЛИ 6 - на вход регистра 12 адреса. Задний фронт этого импульса изменяет адрес в регистре 12 адреса, через формирователь 10 импульсов сбрасывает входной регистр 11 и переводит триггер 8 в нулевое состояние. Теперь во входной регистр вводится информация для записи в блок 16 памяти. Далее работа устройства проходит по алгоритму, .описанному выше. В случае разового отказа ячейки в блоке 1в памяти информация на входах схемы 14 сравнения не совпадает и на ее выходе отсутствует разрешающий потенциал, вследствие чего очередной импульс входной частоты не пройдет на вход триггера 8. Отсутствие сигнала на выходе схемы 14 ср)авнения позволяет импульсам входной частоты пройти через элементы И 18 и ИЛИ 19 на управляющий вхйд записи информации в блок 16 памяти, позволяя повторить запись информации с входного-регистра 11 в блок 16 памяти. Такое повторение обращения к отказанной ячейке позволяет устранить сбой в блоке памяти, который наступает вспедст вие влияния помехи в момент подачи команды Запись. Количество импульсов повторного обращения к отказавшей ячейке блока 16 памяти фиксируется счетчиком 17 импульсов. По заполнению счет чика 17 импульсов сним1ется разрешение с четвертого входа элемента И 18, и устройство остается в режиме проверки записанной информации, при этом индикаторы регистра 12 адреса и дешифратора 13 адреса указывают координаты неисправной ячейки. Если запись информации в блоке 16 памяти проходит без отказа или после повторного обращения к отказавщей ячейке, то, перебирая все все адреса, дешифратор адреса 13 выдает ик1пульс перебора, который поступает на счетный вход триггера 9 и переводит его в единичное состояние, позволяя импульсам

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блокапАМяТи | 1979 |

|

SU801106A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Устройство для контроля блока памяти | 1981 |

|

SU1043753A2 |

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для контроля блока памяти | 1981 |

|

SU1040525A2 |

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1742823A1 |

| Устройство для моделирования многоканальных систем массового обслуживания | 1989 |

|

SU1681308A1 |

Авторы

Даты

1982-09-30—Публикация

1980-04-02—Подача