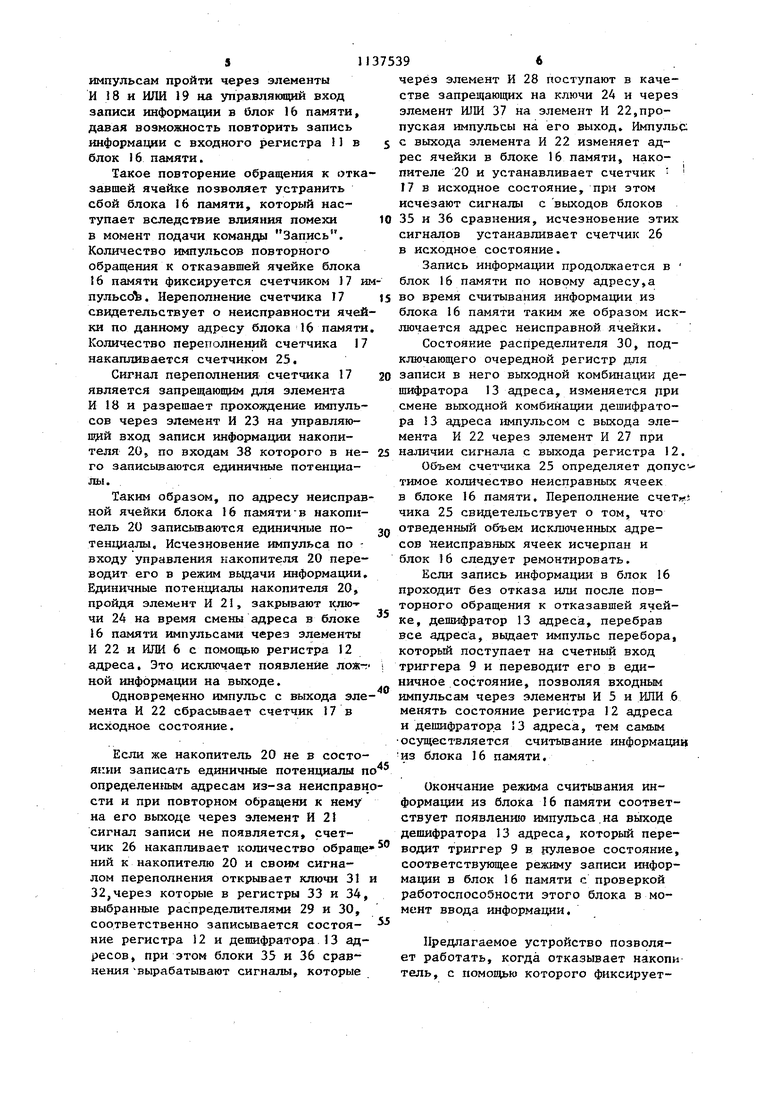

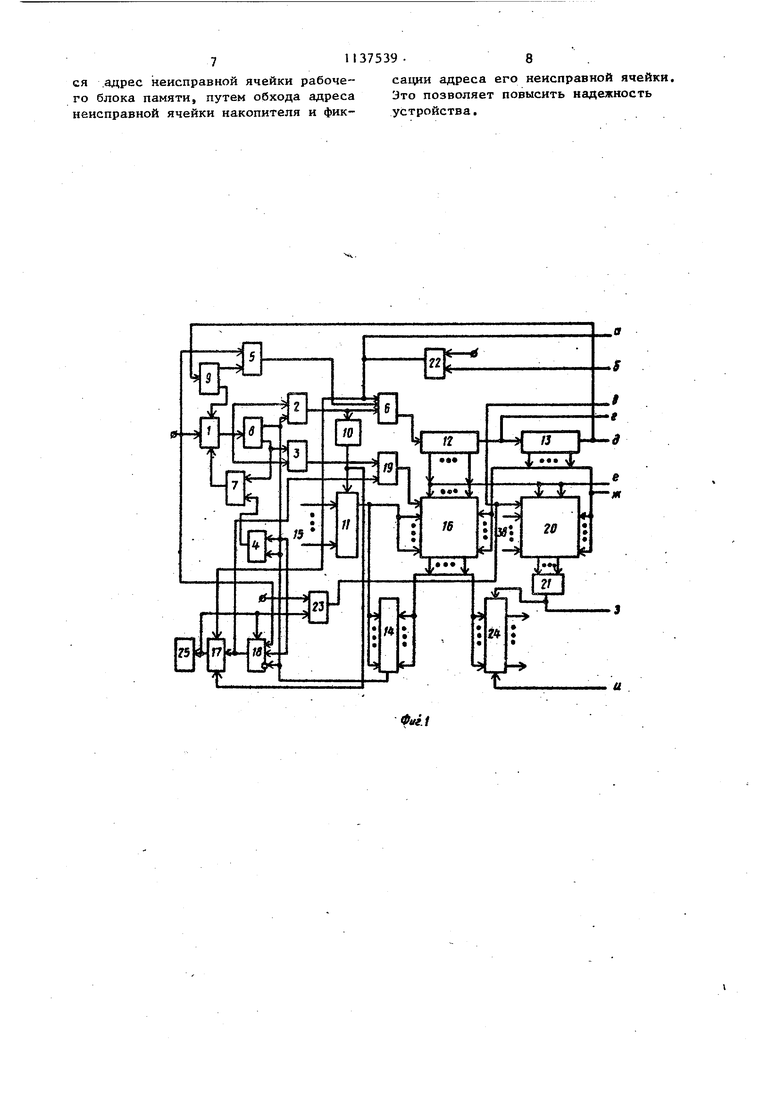

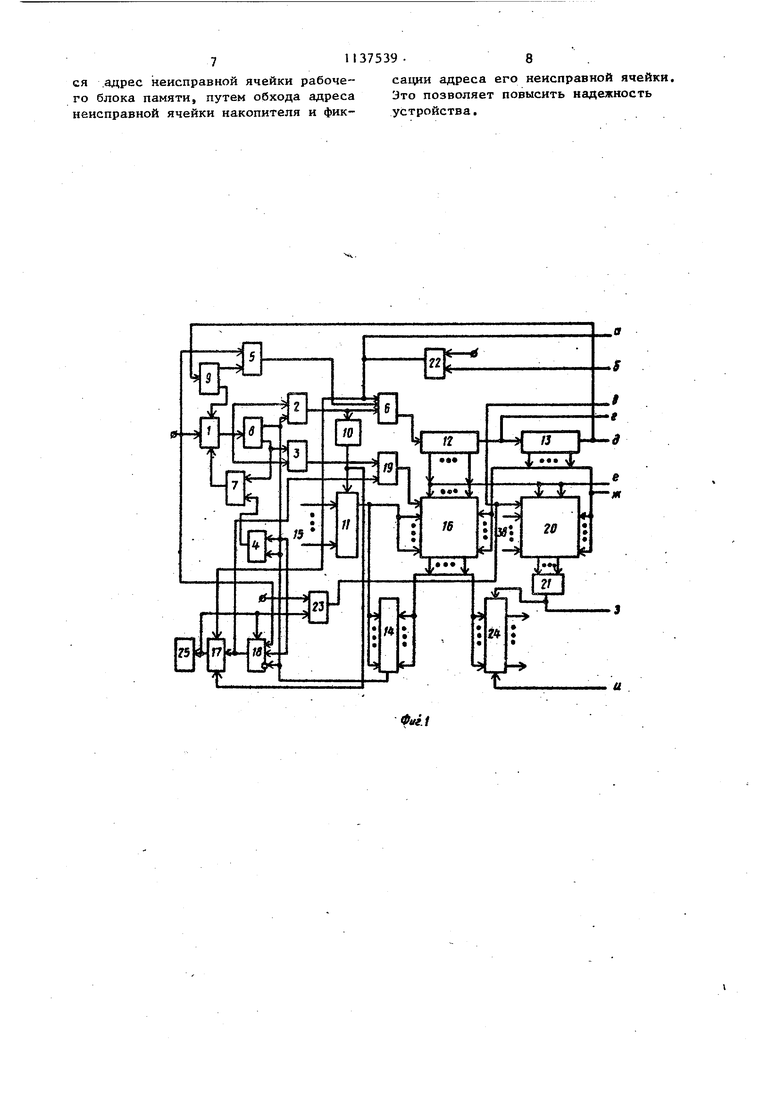

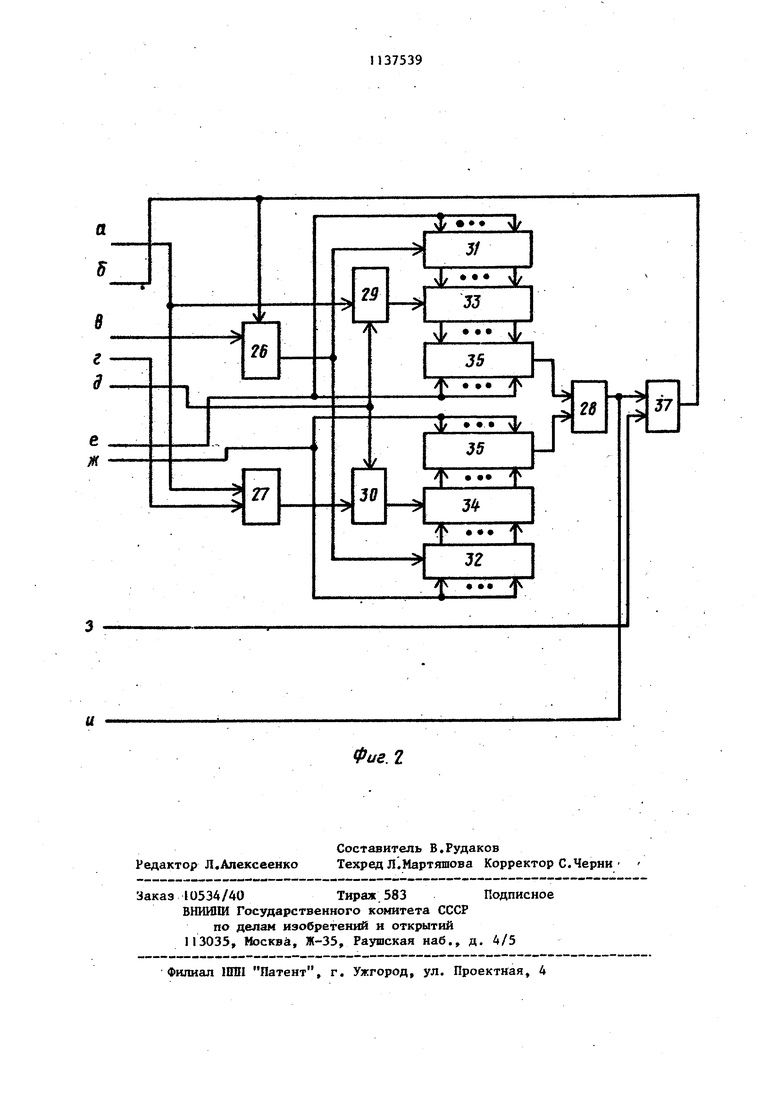

Изобретение относится к вычислительной технике. Но основному авт. св. № 1043753 известно устройство для контроля блока памяти, содержащее входной регистр, регистр адреса, дешифратор адреса, схему сравнения, первый элемент ИЛИ, выход которого подключен к входу регистра адреса, одни из выходов которого соединены с первыми выходами устройства, а другой выход подключен к входу дешифратора адреса, одни из выходов которого соединены с вторыми выходами устройства, выходы входного регистра подключены к третьим выходам устройства и к одним из входов схемы сравнения, другие входы которой соединены с первыми входами устройства, второй элемент ИЛИ, пять элементов И, два триггера, формирователь импульсов, причем второй вход устройства подключен к первым входам первого и пятого элементов И, выход первого элемента И соединен с первыми входа ми второго и третьего элементов И и счетным входом первого триггера нулевой выход которого подключен к второму входу третьего элемента И и первому входу второго элемента ШМ, выход которого соединен с вторьм входом первого элемента И, единичный выход первого триггера подключен к первому входу четвертог элемента И и второму входу второго элемента И, выход которого соединен с первым -входом первого элемента ИЛ и входом формирователя импульсов, в ход которого подключен к одному иэ входов входного регистра, другие входа которого соединены с шинами ввода информации, выход схемы сравнения подключен к второму входу четвертого элемента И, выход которо го соединен с вторьй«1 входом второго элемента ШЩ, другой выход дешиф ратора адреса подключен к счетному входу второго триггера, нулевой и единичный выходы которого соединены соответственно с третьим входом пер вого и вторым входом пятого элемен-г та И, выход пятого элемента И подключен к второму входу первого элемента Н1Ш, первый дополнительный эл мент ШШ, первый : вход которого по ключен к выходу третьего элемента И а выход является четвертым выходом устройства, и первый дополнительный элемент.И, первый вход которого под ключен к-входу первого элемента И, второй вход - к единичному выходу первого триггера, а третий вход первого дополнительного элемента И подключен к выходу схемы сравнения, и счетчик импульсов, первый вход которого подключен к выходу первого дополнительного элемента И и к второму входу первого дополнительного элемента ШШ, второй вход - к выходу формирователя импульсов, а выход счетчика импульсов подключен к четвертому входу первого дополнительного элемента И, ключи, первый дополнительный счетчик импульсов и дополнительные второй, третий и четвертый элементы И, накопитель, одни из входов которого подключены соответственно к выходам регистра адреса и дешифратора адреса, другие входы являются информационными, а выходы соединены с входами второго дополнительного элемента И, выход которого подключен к одним из входов ключей и третьего дополнительного элемента И, другой вход которого является одним из управляющих входов устройства, а выход соединен с одним из входов первого элемента ШШ и третьим входом счетчика импульсов, выход которого подключен к входу первого дополнительного счетчика импульсов, выход которого является одним из выходов устройства, и к одному из входов четвертого дополнительного элемента И, другой вход которого является другим управляющим входом устройства, а выход соединен с управляющим входом накопителя, другие входы ключей соединены с первыми входами устройства, а выходы являются другими входами устройства Ll3. Недостатком этого устройства является ненадежность его работы в случае отказа накопителя, так как при этом устройство прекращает свое функционирование на такте записи единичных потенциалов по информационным входам накопителя. Цель изобретения - повьшение надежности устройства за счет обхода и фиксации адреса, неисправной ячейки накопителя. Поставленная цель достигается тем, что в устройство для контроля блока памяти введены второй дополнительный счетчик импульсов, пятый и шестой допоЛнительш 1е;.И, распределители импульсов, группы ключей. регистры, дополнительные блоки сравнения и второй дополнительный элемент ИЛИ, причем выходы регистра адреса и быходы дешифратора адреса подключены к одним из входов дополнительных блоков сравнения и через соответствующие ключи групп к одним из входов регистров,выходы которых подключены к другим входам соответствующих дополнительных блоков сравнения, выходы которых подключены к входам шестого дополнительного элемента И, выход которого соединен с одними из входов ключей и первым входом второго дополни тельного элемента ИЛИ, второй вход которого подключен к выход} второго дополнительного элемента И, а выход - к второму входу третьего допо нительнрго элемента Ник первому входу второго дополнительного счет чика импульсов, второй вход которог подключен к выходу четвертого допол нительного элемента И, а зыкоц, - к другим входам ключей групп, выход третьего дополнительного элемента И подключен к первьа входам первого распределителя импульсов и пятого дополнительного элемента И, второй вход которого подключен к выходу регистра адреса, а выход - к перво му входу второго распределителя импульсов, выходы распределителей импульсов подключены к другим входам регистров, а вторые входы - к одном из выходов дешифратора .адреса. На фиг,1 и 2 представлена струк турная схема предлагаемого устройст ва -для контроля блока памяти. Устройство содержит элементы И 1-5 .с первого по пятьй, первый 6 второй 7 элементы ИЛИ, первый 8 и второй 9 триггеры, формирователь 10 импульсов, входной регистр 11, регистр 12 адреса, дешифратор 13 ад реса, блок 14 сравнения, шины 15 ввода информации. Входы и выхода устройства соединяются с выходами и входами контролируемого блока 16 па мяти. Устройство также содержит счетчик 17 импульсов, первый дополнителышй элемент И 18, первый допо нительный элемент ИЛИ 19, накопитель 20, второй. 21, третий 22 и чет вертый 23 дополнительные элементы И, ключи 2, первый 25 и второй 26 полнительные счетчики импульсов, пя тый 27 и шестой 28 дополнительные элементы И, распределители 29 и 30 394 импульсов, группы ключей 31 и 32, регистры 33 и 34, дополнительные блоки 35 и 36 сравнения, второй дополнительный элемент ИЛИ 37, информационные входы 38. Устройство работает следующим образом. Исходным состоянием триггеров В и 9 является нулевое. .Регистр 12 адреса и дешифратор 13 адреса устанавливают адрес исходных ячеек блОка 16 памяти. Во входной регистр 11 введена исходная информация для записи в блоке 16 памяти. На вход устройства поступает первьй импульс, который проходит через элемент И 1 на счетный вход триггера 8 и через элементы И 3 и ШШ i9 - на управляющий вход записи информации блока 16 памяти, записывая в него информацию с выходов входного регистра 11. Задний фронт первого входного импульса переводит триггер 8 в единичное состояние. Отсутствие сигнала на управляющем входе записи информации блока 16 памяти при наличии выбранных ранее адресов с регистра: 12 адреса и дешифратора 13 адреса соответствует режиму выдачи информации для блока 16 памяти. Информация с блока 16 памяти поступает на вход блока 14 сравнения, где сравнивается с информацией на входном регистре 11, ив случае их совпадения с выхода блока 14 сравнения через элемент И 4 и элемент ИЛИ 7 поступает потешщал разрешения на элемент И 1 для прохождения второго входного импульса. Этот импульс поступает на счетный вход тригге ра 8, через элемент И 2 на вход формирователя Ш импульсов и через элемент ЩШ 6 на вход регистра 2 адреса. Задний фронт этога 1шпульса изменяет адрес в регистре 12 адреса и переводит триггер 8 в нулевое состояние. Теперь во входной регистр П вводится новая информация для записи в блок I6 памяти. Далее работа устройства проходо1т по описанному алгоритму. В случае разового отказа Лчейкя в блоке 16 памяти информащш на входах блока 14 сравнения ие совпадает, и на ее выходе отсутствует разрешакнщий потенциал, вследствие чего очередкой входной импульс не проходит iHa вход триггера 8. Отсутствие сигнала иа выходе блока 14 сравнения позволяет входным импульсам пройти через элементы И 18 и ИЛИ 19 на управляннций вход записи информации в блок 16 памяти, давая возможность повторить запись информации с входного регистра 11 в блок 16 памяти. Такое повторение обращения к отка завшей ячейке позволяет устранить сбой блока 16 памяти, который наступает вследствие влияния помехи в момент подачи команды Запись, Количество дашульсов повторного обращения к отказавшей ячейке блока 16 памяти фиксируется счетчиком 17 и пульсоЪ. Переполнение счетчика 17 свидетельствует о неисправности ячей ки по данному адресу блока 16 памяти Количество переполнений счетчика 17 накапливается счетчиком 25. Сигнал переполнения счетчика 17 является запрещающим для элемента И 18 и разрешает прохождение импульсов через элемент И 23 на управляющий вход записи информации накопителя 20, по входам 38 которого в Него записьшаются единичные потенциалы. Таким образом, по адресу неисправ ной ячейки блока 16 памятив накопитель 20 записьгоаются единичные потенциалы. Исчезновение импульса по входу управления накопителя 20 переводит его в режим выдачи информации. Единичные потенциалы накопителя 20, пройдя элемент И 2I, закрывают клЮ чи 24 на время смены адреса в блоке 16 памяти импульсами через элементы И 22 и ИЛИ 6 с помощью регистра 12 адреса. Это исключает появление лож-г ной информации на выходе. Одновременно импульс с выхода эле мента И 22 сбрасьшает счетчик 17 в исходное состояние. Если же накопитель 20 не в состоянии записать единичные потенциалы п определенным адресам из-за неисправн сти и при повторном обращени к нему на его выходе через элемент И 21 сигнал записи не появляется, счетчик 26 накапливает количество обраще НИИ к накопителю 20 и своим сигналом переполнения открывает ключи 31 32,через которые в регистры 33 и 34, выбранные распределителями 29 и 30, соответственно записывается состояние регистра 12 и дешифратора 13 адресов, при этом блоки 35 и 36 сравнения вырабатывают сигналы, которые 1 96 через элемент И 28 поступают в качестве запрещающих на ключи 24 и через элемент ИЛИ 37 на элемент И 22,пропуская импульсы на его выход. Импульс с выхода элемента И 22 изменяет адрес ячейки в блоке 16 памяти, накопителе 20 и устанавливает счетчик 17 в исходное состояние, при этом исчезают сигналы с выходов блоков 35 и 36 сравнения, исчезновение этих сигналов устанавливает счетчик 26 в исходное состояние. Запись информации продолжается в блок 16 памяти по новому адресу,а во время считывания информации из блока 16 памяти таким же образом исключается адрес неисправной ячейки. . Состояние распределителя 30, подключающего очередной регистр для записи в него выходной комбинации дешифратора 13 адреса, изменяется рри смене выходной комбинации дешифратора 13 адреса импульсом с выхода элемента И 22 через элемент И 27 при наличии сигнала с выхода регистра 12. Объем счетчика 25 определяет допустимое количество неисправных ячеек в блоке 16 памяти. Переполнение счет чика 25 сввдетельствует о том, что отведенный объем исключенных адресов неисправных ячеек исчерпан и блок 16 следует ремонтировать. Если запись информации в блок 16 проходит без отказа или после повторного обращения к отказавшей ячейке, дешифратор 13 адреса, перебрав все адреса, вьщает импульс перебора, который поступает на счетный вход триггера 9 и переводит его в единичное состояние, позволяя входным импульсам через элементы И 5 и ИЛИ 6 менять состояние регистра 12 адреса и дешифратора 13 адресй, тем самым осуществляется считьюание информации из блока 16 памяти. Окончание режима считывания информации из блока 16 памяти соответствует появленшо импульса,на выходе дешифратора 13 адреса, который переводит триггер 9 в нулевое состояние. соответствующее режиму записи информации в блок 16 памяти с проверкой работоспособности этого блока в момент ввода информации. Предлагаемое устройство позволяет работать, когда отказывает накопи тель, с noMODJibw которого фиксируется .адрес неисправной ячейки рабочего блока памяти, путем обхода адреса неисправной ячейки накопителя и фик1137539.8

сации адреса его неисправной ячейки. Это позволяет повысить надежность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блока памяти | 1981 |

|

SU1043753A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

| Устройство для контроля блока памяти | 1981 |

|

SU1040525A2 |

| Устройство для контроля блокапАМяТи | 1979 |

|

SU801106A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1397968A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПАМЯТИ по авт. св. № 1043753, отличающееся тем, что,с целью повьшения надежности устройства, в него введены второй Дополнительный счетчик импульсов, пятый и шестой дополнительные элементы И, распределители импульсов, группы,ключей, регистры, дополнительные блоки сравнения и второй дополнительный элемент ИЛИ, причем выхода регистра адреса и выходы дешифратора адреса подключены к одним из входов дополнительных блоков сравнения и через соответствующие ключи групп - к одним из входов регистров, выходы которых подключены к другим входам соответствующих дополнительных блоков сравнения, выходы которых подключены к входам шестого дополнительного элемента И,: выход которого соединен с одними КЗ входов ключей и первым входом второго дополнительного элемента Ш1И, второй вход которого подключен к выходу второго дополнительного элемента И, а выход - к второму входу третьего дополнительного элемента Ник первому входу второго дополнительного счетчика импульсов, второй вход которого подключен к выходу четвертого дополнительного элемента И, а выход - к другим входам ключей групп, выход третьего дополнительного элемента И подключен, к первым входам первого распределителя импульсов и пятого дополнительного элемента И, второй вход которого подключен к выходу регистра адреса, а выход - к первому входу второго |1)аспредепителя импульсов,выходы распреЦелителей импульсов,подключены к другим оэ iвходам регистров, а вторые входы к одному из выходов дешифратора адм реса. сд Сд Ю

Фиг. 2

Авторы

Даты

1985-01-30—Публикация

1983-05-13—Подача