ройства, выходами которого являются выходы ключей первой группы, второй вход пятого элемента И и четвертые входы первого и шестого элементов И являются первым управляющим входом устройства, вторым и третьим управляющими входами которого являются соответственно второй вход девятого и первый вход восьмого элементов И, отличающееся тем, что, с целью увеличения информационной емкости устройства, в него введены третий и четвертый накопилеЛк вто рой регистр адреса, второй дешифра,тор адреса, вторая И третья группы ключей, элементы И с девятого по шестнадцатый и элементы ШМ с четвертого по восьмой, причем выход пятого элемента И подключен к первому входу десятого элемента И, второй вход которого соединен с выходом седьмого элемента И первым входом двенадцатого элемента И и первыми входами четырнадцатого и пятнадцатого элементов И, выходы которых подключены соответственно к первому входу восьмого элемента ИЛИ и к первьш входам четвертого и пятого элементов ИЛИ, второй вход и выход четвертого элемента ШШ соединены соответственно с выходом второго элемента И и с входом формирователя импульсов второй вход четырнадцатого элемента И подключен к единичному выходу второго триггера, второму входу восьмого элемента И и первому входу шестнадцатого элемента И, второй вход которого соединен с третьим входом восьмого элемента И и выходом пятого элемента ИЛИ, второй вход которого подключен к выходу тринадцатого элемента И, первым управляющим входам ключей второй группы и третьему входу десятого элемента И, выход которого соединен с первьм входом седьмого элемента ИЛИ, второй вход которого подключен к вьЬсоду двенадцатого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ

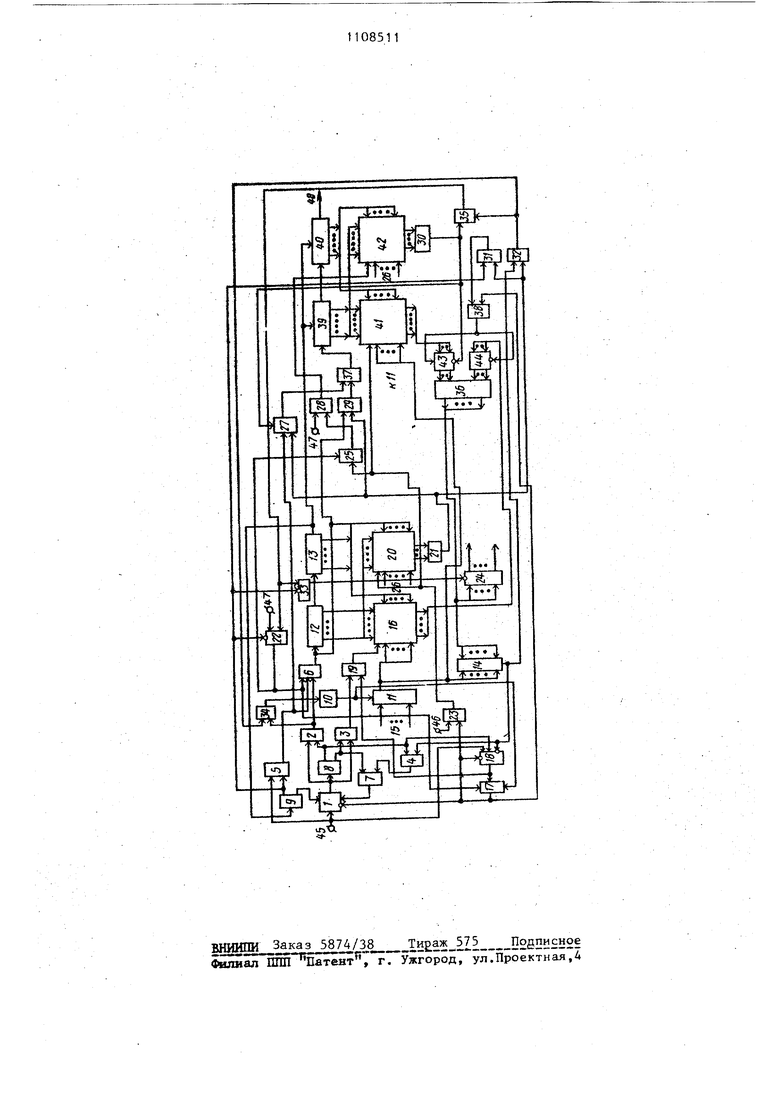

первый вход одиннадцатого элемента ИЛИ подключен к первому входу восьмого элемента И, а второй вход - к выходу второго счетчика импульсов, первый вход которого соединен с выходом восьмого элемента И, а второй вход - с выходом девятого элемента И и управляющим входом третьего накопителя, информационные входы которого подключены к выходам входного регистра, а БЬ1ходы - к входам ключей второй группы, выходы которых соединены с одними из входов шестого элемента ИЛИ, выходы которого подключены к другим входам блока сравнения и входам ключей первой группы, управляющие входа которых соединены с выходом шестнадцатого элемента И, одни из адресных входов третьего и четвертого накопителей подключены к одним из выходов второго дешифратора адреса, а другие адресные входы - к одним из выходов второго дешифратора адреса, одни из входов которого соединены с другими входами второго регистра адреса, один из входов которого подключен к выходу седьмого элемента ИЛИ,другие входы второго регистра адреса и второго дешифратора адреса соединены с другим выходом первого дешифратора адреса, выход одиннадцатого элемента И подключен к управляющему входу четвертого накопителя, выходы которого соединены с входами тринадцатого элемента И, а информационные входы - с информащ{0нными входами второго накопителя, другие входы шестого элемента. ИЛИ подключены к выходам ключей третьей группы, входы которых соединены с выходами первого накопителя, а управляющие входы и вторые управляющие входы ключей второй группы - с выходом восьмого элемента ИЛИ, второй вход которого подключен к выходу первого счетчика импульсов, другой выход второго дешифратора адреса является управляющим выходом устройства. Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Известно запоминающее устройство с самоконтролем,содержащее входной регистр, регистр адреса, дешифратор адреса, блок памяти, схему сравнения и первый элемент ИЛИ, счетчик импуль сов, пять элементов И, два триггера и формирователь импульсов l.1. Недостатком известного устройства является невозможность обхода неисправной ячейки Ь блоке памяти и сохранения его рабочего объема. Наиболее близким техническим реше нием к изобретению является запоминающее устройство с самоконтролем, содержащее основной и дополнительный накопители, входной регистр, регистр адреса, дешифратор адреса, схему сравнения, первый элемент ИЛИ, выход Которого подключен к входу регистра адреса, одни из выходов которого соединены с одними из адресныхвходов накопителя, а другой выход подключен к входу дешифратора адреса, одни из выходов которого соединены с другими адресными входами накопителя, выходы входного регистра под ключены к информационным входам накопителей и к одним из входов схемы сра нения, другие входы которой соедине ны с выходами основного накопителя, второй элемент ИЛИ, пять элементов И, два триггера, формирователь импульсов, причем вход устройства под ключен к первым входам первого и пятого элементов И, выход первого элемента И соединен с первыми входа ми второго и третьего элементов И и счетным входом первого триггера, нулевой выход которого подключен к второму входу третьего элемента И и первому входу второго элемента ИЛ выход которого соединен с вторым вх дом.первого элемента И, единичный выход первого триггера подключен к первому входу .четвертого элемента И и второму входу второго элемента И, выход которого соединен с первым вх дом первого элемента ИЛИ и входом формирователя импульсов, выход кото рого подключен к одному из входов входного регистра, другие выходы ко торого соединены с шинами ввода информации, выход схемы сравнения под ключен к второму входу четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, другой выход дешифратора адреса подключен к счетному входу второго триггера, нулевой и единичный выходы которого соединены соответственно с третьим входом первого и вторым вхо дом пятого элементов И, выход пятого элемента И подключен к второму входу первого элемента ИЛИ, дополнительный элемент ИЛИ, первый вход которого подключен к выходу третьего элемента И, а выход дополнительного элемента ИЛИ подключен к управляющему входу основного накопителя, первый дополнительный элемент И, первый вход которого подключен к первому входу первого элемента И, второй вход - к единичному выходV первого триггера, а третий вход первого дополнительного элемента И подключен к выходу схемы сравнения, счетчик импульсов, первый вход которого подключен к выходу первого дополнительного элемента Ник второму входу дополнительного элемента ИЛИ, второй вход - к выходу формирователя импульсов , а выход счетчика импульсов подключен к четвертому входу первого дополнительного элемента И, ключи, дополнительный счетчик импульсов и дополнительные второй, третий и четвертый элементы И, выходы дополнительного накопителя соединены с входами второго дополнительногоэлемента И, выход которого подключен к одним из входов ключей,и третьего дополнительного элемента И, другой вход которого является одним из входов первого элемента ИЛИ и третьим входом счетчика импульсов,выход которого подключен к входу дополнительного счетчика импульсов, выход которого является одним .из выходов устройства, и к одному из входов четвертого дополнительного элемента И, другой вход которого является другим управляющим входом устройства, а выход соединен с управляющим входом дополнительного накопителя, другие входы ключей соединены с выходами основного накопителя, а выходы являются выходами устройства С 2-. Недостатком этого устройства является то, что при исключении неисправной ячейки накопителя из обращения сокращается информационная емкость устройства. Цель изобретения - увеличение ин формационной емкости устройства лри исключении адреса неисправной ячейки накопителя из эбращения. . Поставленная цель достигается тем 1то в запоминающее устройство с само контролем, содержащее накопители, входной регистр, первый регистр адреса, первый дешифратор адреса, фор№ рователь импульсов, триггеры, блок сравнения, первый и второй счетчики импульсов, первую группу ключей, элементы ИЛИ и элементы И, причем информационные входа первого накопителя и один из входов блока сравнения подключены к выходам входного регистра, одни из адресных входов первого и второго накопителей соединены с одними из выходов первого ре Гйстра адреса,а другие адресные входы - с одними из выходов первого дешифратора адреса, вход которого подключен к другому выходу первого регистра адреса, вход которого соеди нен с выходом первого элемента ИЛИ, выход первого элемента И подключен к первым входам второго и третьего элементов И и счетному входу первого триггера, нулевой выход которого подключен к второму входу третьего элемента И и первому входу второго элемента ИЛИ, выход которого соедине с первьм входом первого элемента И, единичный выход первого триггера под ключен к первому входу четвертого элемента И и второму входу второго элемента И, вьсход которого соединен с первым входом первого элемента ШЖ другой выход первого дешифратора адреса подключен к счетному входу второго триггера, нулевой и единичный выходы которого соединены соответственно с вторым входом первого элемента И и с первым входом пятого элемента И, выход которого подключен к второму входу первого элемента ИЛИ выход блока сравнения соединен с пер вым входом шестого элемента И и вторым входом четвертого элемента И, выход которого подключен к второму входу второго элемента ИЛИ, второй вход шестого элемента И соединен с единичным выходом первого триггера, а выход - с первым входом первого счетчика импульсов и первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, а выход - к управляющему входу первого накопителя, выход формирователя импульсов соединен с управляющим входом входного регистра и вторым входом первого счетчика импульсов, входы седьмого элемента И подключены к выходам второго накопителя, выход восьмого элемента И соединен с третьим входом первого элемента ШШ и третьим, входом первого счетчика импульсов, выход которого подключен к третьим входам первого и шестого элементов И и первому входу девятого элемента И, выход которого соединен с управляющим входом второго накопителя, информационный входы которого и входы входного регистра являются одними из входов устройства, выходами которого являются выходы ключей первой группы, второй вход пятого элемента И и четвертые входы первого и шестого элементов И являются первым управляющим входом устройства, вторым и третьим управляющими входами которого являются соответственно второй вход девятого и первый вход восьмого элементов И, введены третий и четвертьй накопители, второй регистр адреса, второй дешифратор адреса, вторая и третья группы ключей, эл ементы И с девятого по шестнадцатый и элементы ИЛИ с четвертого по восьмой, причем выход пятого элемента И подключен к первому входу десятого элемента И, второй вход которого соединен с выходом седьмого элемента И, первым входом двенадцатого элемента И и первыми входами четырнадцатого и пятнадцатого элементов И, выходы которых подключены соответственно к первому входу восьмого элемента ИЖ и к первым входам четвертого и пятого элементов ИЛИ, второй вход и выход четвертого элемента ИЛИ соединены соответственно с вьпсодом второго элемента И и с входом формирователя импульсов, второй вход четырнадцатого элемента И подключен к единичному выходу второго триггера, второму входу восьмого элемента И и первому входу шестнадцатого элемента И, второй вход которого соединен с третьим входом восьмого элемента И и выходом пятого элемента ИЛИ, второй вход которого подключен к выходу тринадца-. того элемента И, первым управляющим входам ключей второй группы и третьему входу десятого элемента И, выход которого соединен с первым входом S11 седьмого элемента ИЛИ, второй вход которого подключен к выходу двенадцатого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, первый вход одиннадцатого элемента ИЛИ подключен к первому входу восьмого элемента И, а второй вход - к выходу второго счетчика импульсов, первый вход которого соединен с выходом восьмого элемента И, а второй - с выходом девятого элемента И и управяяюв(им входом третьего накопителя, информационные вхо ды которого пьд1$лючены к выходам входного регистра, а выходы - к входай ключей второй группы, выходы когорых. соединены с одними иэ входов шестого элемента ИЛИ, выхода которого подключены к другим входам блока сравнения и входам ключей первой группы, управляющие входы которых соединены с выходом шестнадцатого элемента И, одни из адресных входов третьего и четвертого накопителей подключены к одним из выходов второго дешифратора адреса, а другие адресные входы - к одним из выходов второго дешифратора адреса, одни из входов которого соединены с другими входа второго регистра адреса, один из входов которого подключен к выходу седьмого элемента ИЛИ, другие входы второго регистра адреса и второго дешифратора адреса соединены с другим выходом первого дешифратора адреса,выход одиннадцатого элемент И подключен к управляющему входу четвертого накопителя, выходы которого соединены с входами тринадцатого элемента И, а информационные входы с информационными входами второго накопителя, другие входы шестого эле мента ИЖ подключены к выходам ключей третьей группы, входы которых соединены с выходами первого накопителя, а управляющие входы и вторые управляющие входы ключей второй груп пы - с выходом восьмого элемента ИШ второй вход которого подключен к вы ходу первого счетчика импульсов, другой выход второго дешифратор а ад реса является управляющим выходом устройства. На чертеже представлена функциональная схема предложенного устройс ва. Устройство содержит элементы И 1-5 с первого по пятый, первый 6 И второй 7 элементы ИЛИ, первый 8 и 16 второй 9 триггеры, формирователь 10 импульсов, входной регистр 11, первый регистр 12 адреса, первый дешифратор 13 адреса, блок 14 сравнения. На чертеже обозначены входы 15 уст-.ройства. Устройство содержит также первьй накопитель 16, первый счетчик 17 импульсов, шестой элемент И 18, третий элемент ИЛИ 19, второй накопи|тель 20, седьмой 21, восьмой 22 и девятый 23 элементы И, первую группу клиочей 24, второй счетчик 25 импульсов. На чертеже обозначены входы 26 устройства. Устройство содержит элементы И 27-33 с десятого по шестнадцатый, элементы ИЛИ ЗА-38 с четвертого по восьмой, второй регистр 39 адреса, второй дешифратор 40 адреса, третий 41 и четвертый 42 накопители, вторую 43 и третью 44 группы ключей. ,На чертеже обозначены также управляющее входы с первого по третий и управляю й выход 48 устроства. Предпоженное устройство работает следующим образом. В Исходном состоянии триггеры 8 и 9 установлетл в нулевое состояние. Регистр 12 и дешифратор 13 устаиавливают адрес исходных ячеек накопителя 16. В регистр 11 введена исходная информация для записи в накопитель 16. И вход 45 поступает nepBbdt импульс, который проходит через элемент И 1 иа счетный вход триггера 8 и через элементы И 3 и ИЛИ 19 на управляющей вход йакопителя 16, запи-., сывая в него информацию с выходов регистра 11. Задний фронт первого входного импульса переводит триггер 8 в епиничное состояние.. Отсутствие сигнала на управляющем входе накопителя 16 при наличии выбранных адресов в регистре 12 и на выходе де1шфратора 13 соответствует режиму вьщачи информа1щи из накопителя 16. информация из которого поступает на вход блока 14, где сравнивается с информацией на регистре 11 . и в случае их совпадения . с выхода блока 14 поступает потендаал разрешения на элемент И 1 для прохождения с входа 45 второго импульса. Этот импульс поступает на счетный вход триггера 8, на входы формирователя 10, регистра 12. Задний фронт этого импульса изменяет адрес в регистре 12 и пе.реводит триггер 8 в нулевое состояние. Теперь в регистр 11 вводится новая информация для записи в нгкопитель 16. Далее работа устройства проходит аналогично описанному. В случае разового отказа ячейки в накопителе 16 информация на входах блока 14 не совпадает, и на его выхо де отсутствует разрешающий потенцигш, вследствие чего очередной импуль с входа 45 не пройдет на вход триггера 8. Отсутствие сигнала на выходе блока 14 позволяет импульсам с входа 45 пройти через элементы И 18 и ИЛИ 19 на управляющий вход накопителя 16, позволяя повторить запись информации в него с входного регистра 11. Такое повторное обращение к отка завшей ячейке позволяет устранить сбой в накопителе 16, который насту пил вследствие влияния помехи в момент подачи команды Запись. Количество импульсов повторного обращения фиксируется счетчиком 17. Переполнение счетчика 17 свидетельствует о неисправности ячейки в накопите ле 16 по данному адресу. Сигнал пер полнения счетчика 17 является запредающим для элемента И 18 и разрешает прохождение импульсов с тактовой час тотой с входа 46 через элемент И 23 на управляющий вход накопителя 20, по входам 26 которого в него записываются единичные потенциалы. Таким образом, по адресу неисправной ячейки накопителя 16 в накопитель 20 записываются единичные потенциалы. Одновременно импульсы с выхода элемента И 23 поступают на управляющий вход накопителя 41, в который по первому адресу, выбранному регист ром 39 и де фратором 40, записыва 5 ся информация с выходов регистpa 11. Одновременно сигнал переполнения счетчика 17 поступает запрещающим сигналом на вход элемента И 1, ключей 44 и раэрещающим - для ключей 43 через элемент ИЛИ 38. В момент отсутствия сигнала на выходе элемента И 23 накопитель 41 находится в режиме выдачи записанной в него информации, которая через ключи 43 и элемент ИЛИ 36 поступает на блок 14, который в случае совпадения ее с информацией на регистре 11 вырабатывает сигнал, поступающий через элемент И 32 и элемент ИЛИ 35 на вход элемента И 22 позволяя импульсам тактовой частоты с входа 47 сбросить в исходное положение счетчик 17, а через элемент ИЛИ6 - сменить адрес в регистре 12 для накопителя 16 и через элементы И 29 и ИЛИ 37 для сменБ адреса в накопителе 41. Одновременно сигнал с выхода элемента И 32 поступает на формирователь 10 для сбрасывания регистра 11. Если после обращения к накопителю 41 сигнал на выходе блока 14 не появится, то сигнал переполнения счетчика 25 поступит на входы элемента И 28, позволяя пропустить импульсы тактовой частоты с входа 47 на управляюищй вход накопителя 42, .записывая в него по входам 26 единичные потенциалы. По окончании импульса тактовой частоты сигнал с выхода элемента И 30 .закрывает ключи 43 и 24, а через элемент И 22 в это время разрешает прохождение с входа 47 импульсов тактовой частоты, которые производят смену адреса в регистрах 12 и 39 и устанавливают счетчики 17 и 25 в исходное состояние. Далее устройство работает аналогично описанному,т.е. информация записьшается в накопитель 16 по новому адресу с обходом неисправной ячейки. Если запись информации в накопитель 16 прошла без отказа сразу или после повторного обращения к отказавшей ячейке, то, перебрав нее адреса, дешифратор 13 выдает сигнал перебо- . ра, который поступит на счетный вход триггера 9 и переведет его в единичное состояние, позволяя импульсам с входа 45 через элемент И 5 и элемент ИЛИ 6 менять состояние регистра 12 и дешифратора 13, тем самым осуществляя считьшание информации из накопителя 16. Если в процессе записи информации в накопителе 16 зафиксирован адрес неисправной ячейки путем записи единичных потенциалов по этому адресу в накопитель 20, то сигнал на выходе элемента И 21 при считывании информации через элемент И 31 и элемент ШШ 38 закроет ключи 44, а .ключи 43 откроет, при этом на выход устройства поступит информация с выходов накопителя 41. Если в процессе записи информации зафиксирован адрес неисправной ячей.ки путем записи единичных потенциалов также и в накопитель 42, то при считьшании информации блокируются ключи 44 сигналом с элемента И 21 и ключи 43 - сигналом с элемента И 30. На выход устройства информация не поступает, а импульсом с выхода эелемента И 5 выбран следующий адрес накопителей 16 и 41 и накопителей 20 и 42.

Окончанию режима считьшания информации из накопителя 16 соответствует появление сигнала на выходе дешифратора 13, который переводит триггер 9 в нулевое положение, соответствующее режиму записи информации с проверкой работоспособности накопителя 16 в момент ввода информации.

Сигнал на выходе 48 свидетельствует о том, что сохранить рабочую информационную емкость устройства невозно, так как суммарное количество неисправных ячеек памяти в накопителях 16 и 41 превышает информационную емкость накопителя 16, и следует приступить к ремонту накопителей 16 и 41, для чего отключаются входы 46 и 47 тактовых частот. Тогда по заполнении счетчика 17 снимается разрешение с четвертого входа элемента И 18 и устройство остается в режиме проверки записанной информации, при этом индикаторы регистра 12 и дешифратора 13 указывают координаты неисправной ячейки.

Предлагаемое устройство отличается от прототипа тем, что оно позволяет работать с накопителем, в состав которого входят неисправные ячейки, за счет исключения их из обращения и позволяет сохранить информационную емкость устройства за счет записи информации в. другой накопитель, исправность которого также контролируется в процессе работы с ним, что дает возможность записать полный объем информации за один цикл обращения, что сокращает время обработки информации.

Технико-экономическое преимущество предложенного устройства по сравнению с прототипом заключается в увеличении его информационной емкости при исключении из обращения неисправных ячеек.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Устройство для контроля блока памяти | 1981 |

|

SU1043753A2 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

| Устройство для контроля времени работы оборудования | 1986 |

|

SU1434467A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

| Устройство для контроля блокапАМяТи | 1979 |

|

SU801106A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

ЗАПОМИПАЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накопители, входной регистр, первый регистр адреса, первьй дешифратор адреса, формирователь импульсов, триггеры, блок, сравнения, первый и второй счетчики импульсов, первую группу ключей, элементы ШМ и элементы И, причем информационные входы первого накопителя и одни из входов блока сравнения подключены к выходам входного регистра, одни из адресных входов первого . и второго накопителей соединены с одними из выходов первого регистра адреса, а другие адресные входы - с одними КЗ выходов первого дешифратора адреса, вход которого подключен к другому выходу первого регистра адреса, вход которого соединен с выходом первого элемента ИЛИ, выход первого элемента И подключен к первьм входам второго и третьего элементов И и счетному входу первого триггера нулевой выход которого подключен к второму входу третьего элемента Ни первому входу второго элемента ИЛИ, выход которого соединен с первым входом первого элемента И, единичный выход первого триггера- подключен к первому входу четвертого э/хемента И и второму входу второго элемента И, выход которого соединен с первьи входом первого элемекта ИЛИ, другой выход первого дещифратора адреса подключен к счетному входу второго триггера, нулевой и единичный выходы которого соединены соответственно с вторым входом первого элемента И и с Первым входом пятого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, выход блока сравнения соединен с первым входом шестого элемента И и вторь 1 входом четвертого элемента И, выход которого подключен к второму входу второго элемента ИЛИ, второй вход шестого элемента И соединен с единичным выходом первого триггера, а выход с первым входом первого счетчика импульсов и первым входом треть; его элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, а вьрсод - к управляющему входу первого накопителя, выход формирователя импульсов соединен с управляющим входом входного регистра У1 и вторым входом первого счетчика импульсов, входы седьмого элемента И подключены к выходам второго накопителя, выход восьмого элемента И соединен с третьим входом первого элемента ИЛИ и третьим входом первого счетчика импульсов, выход которого подключен к третьим входам первого и шестого элементов И и первому входу девятого элемента И, выход которого соединен с управляющим входом второго накопителя, информационные входы которого и входы входного регистра являются одними из входоп уст

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля блока памяти | 1980 |

|

SU963107A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3295405/18-24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-08-15—Публикация

1983-05-20—Подача