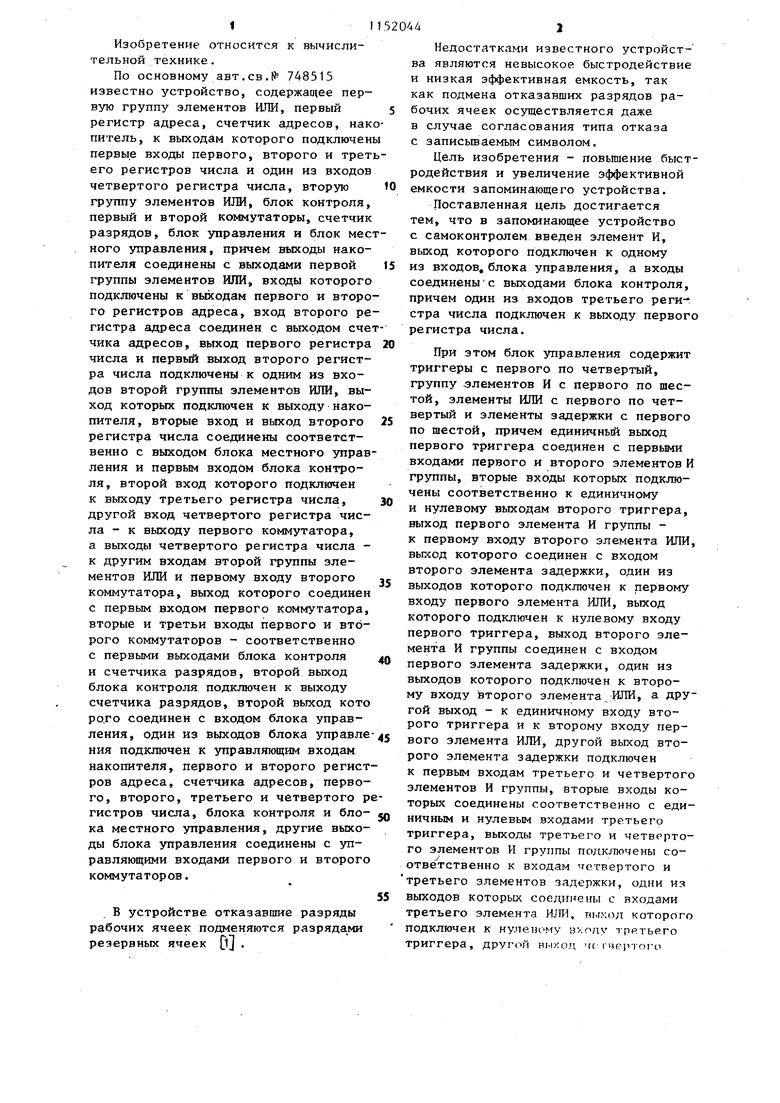

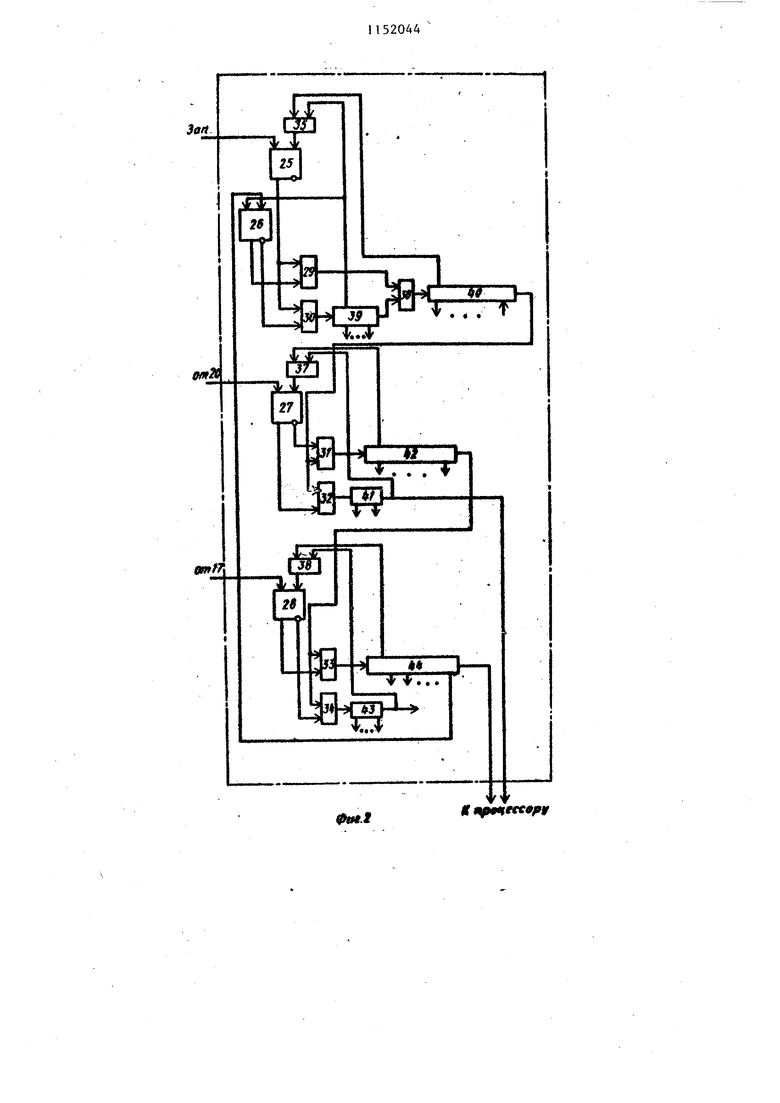

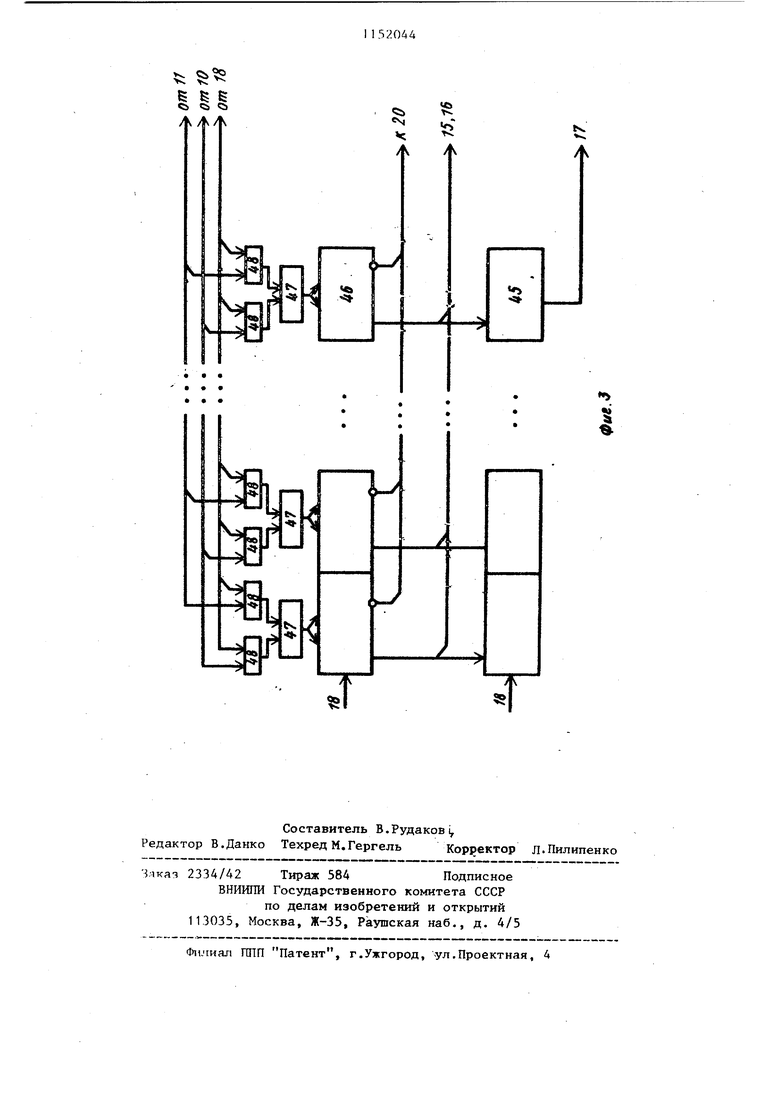

IМ Изобретение относится к вычислительной технике. По основному авт.св.( 748515 известно устройство, содержащее первую группу элементов ИЛИ, первый регистр адреса, счетчик адресов, нак питель, к выходам которого подключен первые входы первого, второго и трет его регистров числа и один из входов четвертого регистра числа, вторую группу элементов ИЛИ, блок контроля, первый и второй коммутаторы, счетчик разрядов, блок управления и блок мес ного управления, причем выходы накопителя соединены с выходами первой группы элементов ИЛИ, входы которого подключены к выходам первого и второ го регистров адреса, вход второго ре гистра адреса соединен с выходом сче чика адресов, выход первого регистра числа и первый выход второго регистра числа подключены к одним из входов второй группы элементов ИЛИ, выход которых подключен к выходу накопителя, вторые вход и выход второго регистра числа соединены соответственно с выходом блока местного управ ления и первым входим блока контроля, второй вход которого подключен к выходу третьего регистра числа, другой вход четвертого регистра числа - к выходу первого коммутатора, а выходы четвертого регистра числа к другим входам второй группы элементов ИЛИ и первому входу второго коммутатора, выход которого соединен с первым входом первого коммутатора, вторые и третьи входы первого и второго коммутаторов - соответственно с первыми выходами блока контроля и счетчика разрядов, второй выход блока контроля подключен к выходу счетчика разрядов, второй выход кото рого соединен с входом блока управления, один из выходов блока управле ния подключен к з равляющим входам накопителя, первого и второго регист ров адреса, счетчика адресов, первого, второго, третьего и четвертого р гистров числа, блока контроля и блока местного управления, другие выходы блока управления соединены с управляющими входами первого и второго коммутаторов. В устройстве отказавшие разряды рабочих ячеек подменяются разряда ми резервных ячеек jj . 4 Недостатками известного устройства являются невысокое быстродействие и низкая эффективная емкость, так как подмена отказавших разрядов рабочих ячеек осуществляется даже в случае согласования типа отказа с записываемым символом. Цель изобретения - повышение быстродействия и увеличение эффективной емкости запоминающего устройства. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем введен элемент И, выход которого подключен к одному из входов, блока управления, а входы соединеныС выходами блока контроля, причем один из входов третьего регистра числа подключен к выходу первого регистра числа. При этом блок управления содержит триггеры с первого по четвертый, группу элементов И с первого по шестой, элементы ИЖ с первого по четвертый и элементы задержки с первого по шестой, причем единичный выход первого триггера соединен с первыми входами первого и второго элементов И группы, вторые входы которых подключены соответственно к единичному и нулевому выходам второго триггера, выход первого элемента И группы к первому входу второго элемента ИЛИ, выход которого соединен с входом второго элемента задержки, один из выходов которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, выход второго элемента И группы соединен с входом первого элемента задержки, один из выходов которого подключен к второму входу второго элемента./или, а другой выход - к единичному входу второго триггера и к второму входу первого элемента ИЛИ, другой выход второго элемента задержки подключен к первым входам третьего и четвертого элементов И группы, вторые входы которых соединены соответственно с единичным и нулевым входами третьего триггера, выходы третьего и четвертого элементов И группы подключены соотвётственно к входам тетвертого и третьего элементов задержки, одни из выходов которых соединены с входами третьего элемента ИЛИ, В1,гход которого подключен к нулевому вхолу третьего триггера, другой выход ч -гнертотч элемента задержки - к первым входам пятого и шестого элементов И группы вторые входы которых подключены соот ветственно к единичному и нулевому выходам четвертого триггера, выходы пятого и шестого элементов И группы соответственно к входам шестого и пятого элементов задержки, одни из выходов которых подключены к входам четвертого элемента ИЛИ, выход которого подключен к нулевому входу четвертого триггера, другой выход шесто го элемента задержки - к нулевому входу второго триггера, единичные входы первого, третьего и четвертого триггеров являются одними из входов блока управления. На фиг. 1 изображена структурная схема запоминающего устройства с самоконтролем; на фиг. 2 - структурная схема блока управления (например, дл режима записи); на фиг. 3 - один из возможных вариантов блока контроля. Устройство (фиг. 1) содержит накопитель 1, имеющий входы 2, первую группу элементов ИЛИ 3, первый 4 и второй 5 регистры адреса. Регистр 4 имеет входы 6. Устройство также содержит счетчик 7 адресов. К выходам 8 накопителя 1 подключены одни из входов первого регистра 9 числа. Устройство содержит, кроме того, второй 10, третий 11 и четвертый 12 регистры числа, вторую группу элемен тов ИЛИ 13, блок 14 контроля, первь1й 15 и второй 16 коммутаторы, счетчик 17 разрядов, блок 18 управления, блок 19 местного управления, элемент И 20. Устройство имеет вход 21 и выход 22. Элемент И 20 име е- входы 23 и выход 24.. Блок 18 управления (фиг. 2) содержит триггеры 25-28 с первого по четвертый, элементы И 29-34 с первого по шестой, элементы ИЛИ 35-38 с первого по четвертый и элементы 39-44 задержки с первого по шес той. Блок 14 контроля (фиг. 3) содержит регистр 45 сдвига, регистр 46 элементы ИЛИ 47 и эл менты И 48. Устройство работает следующим образом. В исходном состоянии счетчик 47 обнулен. Для каждого линейного участ ка программы или для массива чисел, которые будут записываться последов тельно, выделяются резервные ячейки накопителя 1 .. В счетчик 7 при этом записывается адрес первой резервной ячейки, а на вход 6 регистра 4 поступает адрес первой ячейки записываемого или считываемого массива чисел. При записи число через вход 21 поступает в регистр 9, и через элементы ИЛИ 3 содержимое регистра 4 подается на вход накопителя 1. Прямой код числа из регистра 9 заносится на ресистр 11 и через элементы ИЛИ 13 записывается в ячейку накопителя 1. После этого производится считывание прямого кода из накопителя 1 на регистр 10. Содержимое регистров 10 и 11 подается на блок 14. В случае, если отказавших разрядов в ячейке нет или тип отказа совпадает с записываемыми символами, то на вход 6 регистра подается следующий адрес и аналогично производится запись второго числа. При совпадении содержимых регистров 10 и 11 на выходах блока 14 контроля будут все единичные сигналы, которые через элемент И 20 поступают на блок 18 управления, который вырабатывает управляющие сигналы для записи второго числа. Если же в ячейке есть отказавшие разряды и тип отказа не совпадает со значением записываемого символа, то соответствующие разряды регистров 10 и 11 в блоке 14 контроля не совпадут и на входах элемента И 20 будет соответствующее количество нулевых сигналов. По нулевому сигналу элемента И 20 блок 18 организует работу устройства в следующей последовательности . Производится запись обратного кода из регистра 9 через элементы ШШ 13 в ячейку накопителя 1, и содержимое ячейки считывается на регистр 11. После этого производится запись-считывание прямого кода числа на регистр 10. Содержимое регистров 10 и 11 подается на блок 14. Последний и счетчик 17 вьщают на ком ..мутатор 15 сигналы, по которьм из регистра 9 в.младшие разряды регистра 12 передаются ра.зряды числа, соответствукицие отказавшим разрядам ячейки. Затем с блока 14 в счетчик 17 разрядов записывается код, соответствующий количеству отказавших разрядов ячейки. Из блока 18 в блок 19 поступает сигнал, по которому в маркерный разряд ячейки накоS1пителя 1 через регистр 10 записывае ся код 1. Аналогично производится запись числа во вторую отказавшую ячейку, в которой тип отказавших разрядов не согласован с записываеtuat символом, только соответствующи разряды регистра 9 записываются в следующие младшие незанятые разряды регистра 12. После того, как все разряды регистра 12 заполнены, счетчик 17 разрядов выдает сигнал заполнения в блок 18. Адрес резервист ячейки из счетчика 7 поступает на регистр 5 и через злементы ИЛИ 3 на вход 2 накопителя 7. Содержимое регистра 12 через элементы ИЛИ 13 записывается в первую резервную яче ку массива чисел. После этого по сигналу из блока 18 в сч(етчике 7 формируется адрес следующей резервной ячейки. Чтение информации производится следуяяцим образом. В регистр 4 пода ется адрес первой ячейки считываемо го массива Jшceл, а в счетчик 7 записывается адрес первой резервной ячейки массива чисел. Счетчик 17 пр этом находится в нулевом состоянии. По сигналу из блока 18 производится передача содержимого счетчика 7 через регистр 5 и элементы ИЛИ 3 на вход 2 накопителя 1. Производится чтение из первой резервной ячейки на регистр 12. Затем из регистра 4 поступает адрес первой ячейки считы 46 ваемого массива чисел и производится чтение на регистры 9 и 10. Если в маркерном разряде код О, то, следовательно, в ячейке не было отказавших разрядов, и число из регистра 9 поступает на выход 22. Если же в маркерном разряде код 1, то производится запись-чтение обратного кода числа на регистр 11. Содержимое регистров 10 и 11 подается на блок 14. По сигналам из блока 14 и счетчика 17 через коммутатор 16 производится передача младших разрядов регистра 12 в регистр 9. J азряды отказавшей ячейки, таким образом, подменяются разрядами резервной ячейки. Число из регистра 9 nocTjmaeT на выход 21. В счетчик 17 записывается код, соответствуюв(ий количеству исдользованных разрядов регистра 12. Если все разряды ре-здстра 12 использованы, на что указывает соответствующее состояние счетчика 17, то по сигналу из блока 18 управления в счетчике 7 формируется адрес следующей резервной ячейки. Содержимое резервной ячейки считывается на регистр 12, и аналогично продолжается считывание массива чисел с подменой отказавших разрядов. Предлагаемое устройство по сравнению с известным требует меньшего колк гества резервных ячеек и является более быстродействующим. от 19 UIJ

от 1

i t

СЮ т Jj

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1399823A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ по авт. св. № 748515, отличающееся тем, что, с целью повьшения быстродействия и увеличения эффективной емкости устройства, в него введен элемент И, выход которого подключен к одному из входов блока управления, а входы соединены с выходами блока контроля, причем один из входов третьего регистра числа подключен к выходу перaqro регистра числа. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит Триггеры с первого по четвертый, группу элементов И с первого по шестой, элементы ИЛИ с первого по четвертый и элементы задержки с первого по шестой, причем единичный выход пернрго триггера соединен с первыми входами первого и второго элементов И группы, вторые входы которых подключены соответственно к единичному и нулевому выходам второго триггера, выход первого элемента И группы подключен к первому . входу второго элемента ШШ, выход которого соединен с входом второго элемента задержки, один из выходов которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, выход второго элемента И группы соединен с входом первого элемента задержки, один из выходов которого подключен к второму входу второго элемента ИЛИ, а другой выход к единичному входу второго триггера и второму входу первого элемента ИЛИ, другой выход второго элемента задержки подключен к первым входам третьего и четвертого элементов И группы, вторые входы которых соединены соответственно с единичным и нулевым выходами третьего триггера, выходы третьего и четвертого элементов И группы (Л подключены соответственно к входам четвертого и третьего элементов задержки, одни из выходов которых соединены с входами третьего элемента ИЛИ, выход которого подключен к нулевому входу третьего триггера, другой выход четвертого элемента заел ю держки подключен к первым входам пятого и шестого элементов И группы, вторые входы которых подключены соо ответственно к единичному и нулевому 4 4 выходам четвертого триггера, выходы пятого и шестого элементов И группы подключены соответственно к входам шестого и пятого элементов задержки, одни из выходов которых подключены к входам четвертого элемента ИЛИ, выход которого подключен к нулевому входу четвертого триггера, другой выход шестого элемента задержки подключен к нулевому входу второго триггера, единичные входы первого, третьего и четвертого триггеров являются .одними из входов блока управления.

Фа8.1

0IW.1

I t entffoplf

%

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-04-23—Публикация

1984-01-31—Подача