Изобретение относится к запоминающим устройствам и является усовершенствованием запоминакхцего устройства с.самоконтролем.

По основному авт.св. 748515 известно устройство содержащеенакопитепь, регистры числа, группы элементов ИЛИ, регистры Адреса, счетчик адресов, блок контроля, блок управ- . ления, блок местного управления, коммутаторы и счетчик разрядов,причем выход накопителя подключен к первым входам П(9рвого, второго и четвертого регистров числа и ко входу третьего регистра , входы накопителя соединены с выходами эле ментов ИЛИ, входы элементов ИЛИ первой группы подключены к выходам Первого регистра адреса и второго регистра адреса; вход которого соединен с выходом счетчика адресов,первый выход второго регистра числа подключен к одним из входов второй . группы элементов ИЛИ, вход и выход второго регистра числа,соединены соответственно с выходом блока местного управления и первым входом блока контроля второй вход которого соединен с выходом третьего регистра числа, выходы блока управления

подключены к управляющим входам накопителя, регистров адреска, счетчика адресов, регистров числа, блока контроля, блока местного управления и ксиллутаторов; второй вход четвертого регистра числа подключен к выходам первого коммутатора, а выходы - к другим входам элементов ИЛИ йторой группы и первому входу второtoго коммутатора, выход которого соединен со вторьм входом первого регистра числа, выход которого подключен к первому входу первого iKONwyTa-, тора, вторые и третьи входы первого

15 и второго коммутатора соединены соответственно с первыми выходами блока контроля и счетчика разрядов,втоj рые выхода которых подключены соответственно ко входам счетчика раз20 рядЬв и блока управления I.

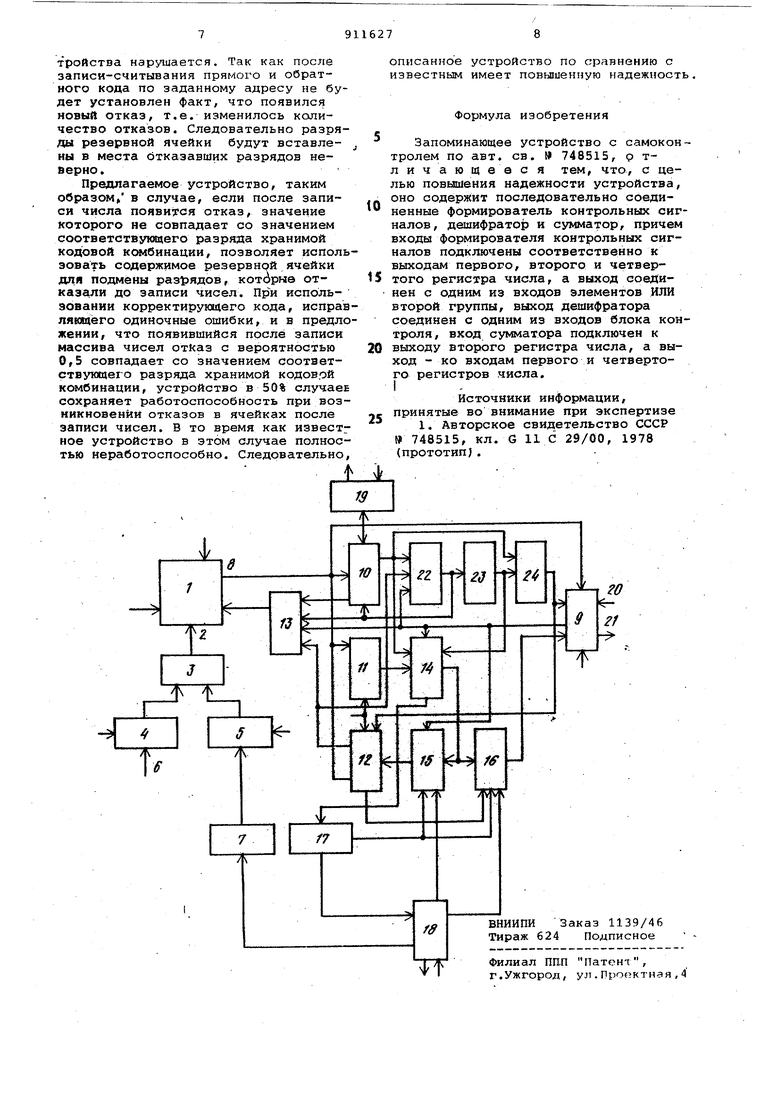

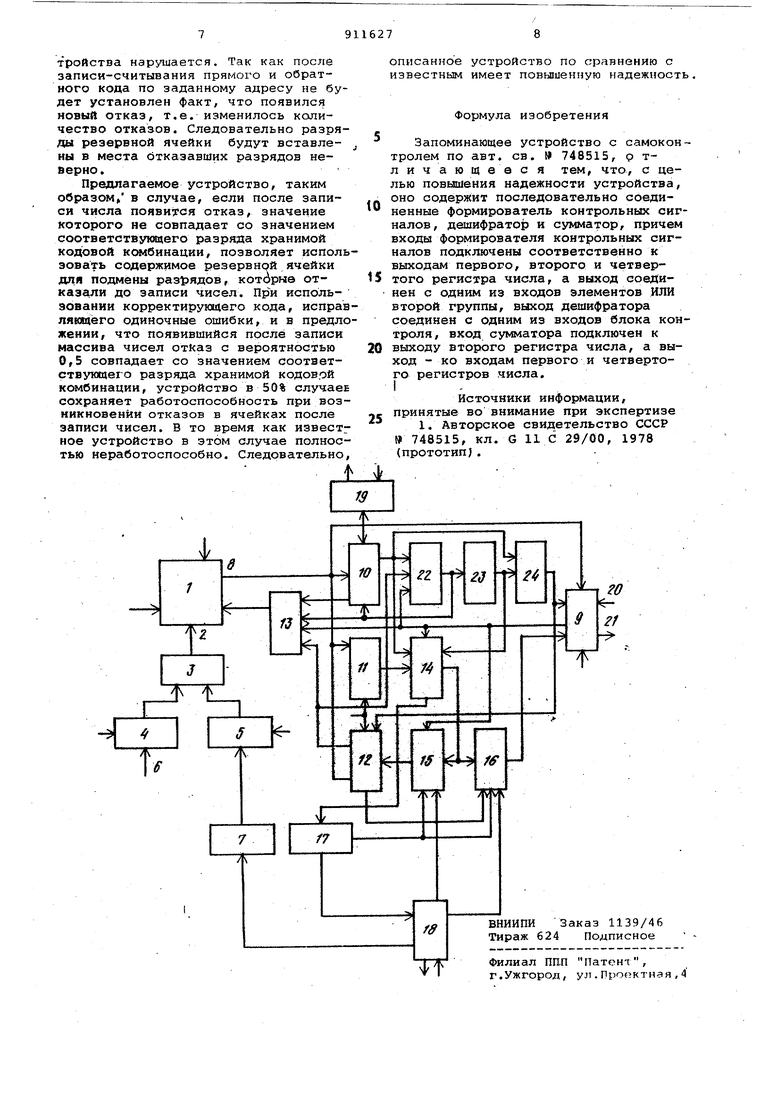

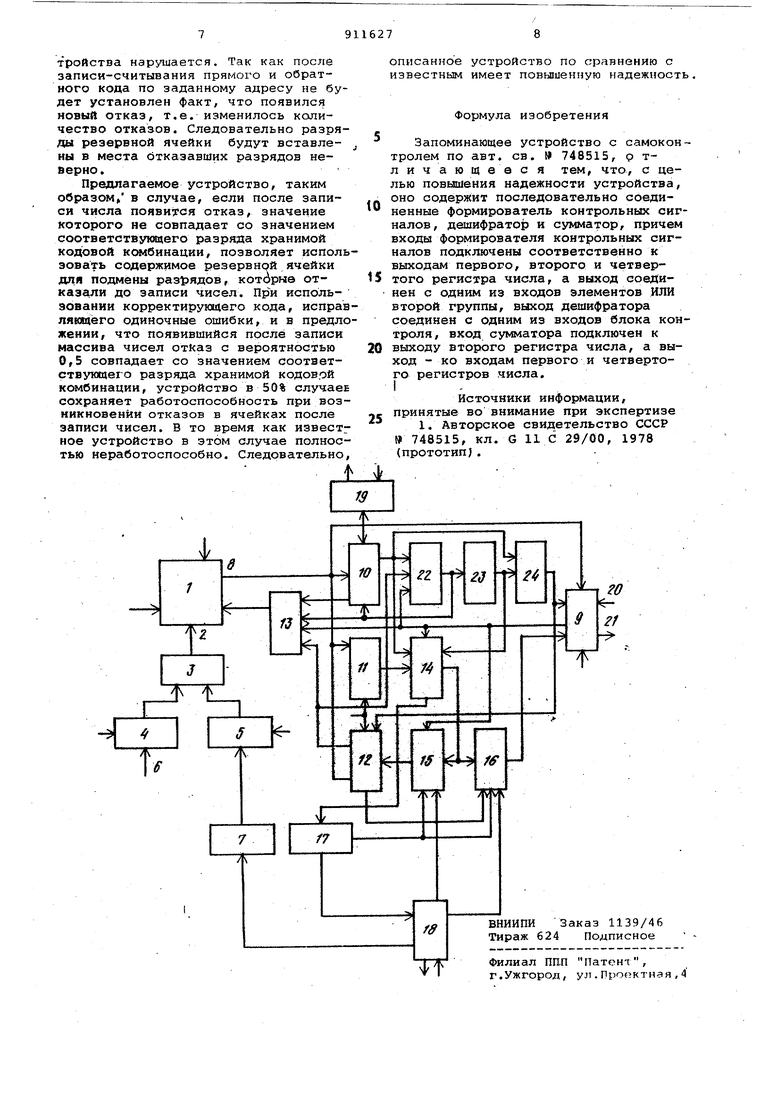

В этом устройстве при последова- v тельной записи линейного участка програьалы или массива чисел данные, подлежащие записи в отказавшие разряды ячеек, компануются на отдельном регистре в слово и записываются в резервную ячейку. При считывании программы или массива чисел вместо значений отказавших разрядов используются их истинные значения, содержашиес.ч в резервной ячейке. Однако,если после записи програлфлрл или массива чисел появляются еще отказавшие разряды, то разряды резервной ячейки могут быть уставлены в места отказав ших разрядов неверно (со смещением на количество дополнительно отказавших разрядов) . Это приводит к нару шению работоспособности устройства, снижению его надежности. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем что в запоминающее устройство с самоконтролем введены последовательно соединенные формирователь контрольных сигналов. Дешифратор и сумматор причем входы формирователя контрольных сигналов подключены соответствен но к выходам первого, второго и четвертого регистра числа, а выход соед нен с одним из йходов элементов ИЛИ второй группы, выход дешифратора соединен с одним из входов блока контроля , вход сумматора подключен к входу второго.регистра числа, а выход - ко входам первого и четвертого регистров числа. На чертеже изображена структурная схема предложенного устройства,. Устройство содержит накопитель 1 имеющий входы 2, первую группу элементов ИЛИ 3, первый регистр 4 адреса, второй регистр 5 адреса, входы 6первого регистра адреса, счетчик 7адресов. К выходам 8 накопителя подключены первые входы первого регистра 9 числа, второго регистра 10 числа, вход третьего регистра 11 чис ла и первый вход четвертого регистра 12 числа. Устройство содержит также вторую группу элементов ИЛИ 13,блок 1.4 контроля, первый 15 и второй 16 коммутаторы, счетчик 17 разрядов, блок 1 управления, блок 19 местного управления, вход 20 и выход 21 устройств .формирователь 22 контрольных сигнало дешифратор 23 и сумматор 24,представ .ляющий собой группу сумматоров по мо дулю два. При этом входы 2 накопителя 1 со динены с выходами элементов ИЛИ 3, входы которых подключены к выходам первого 4 и второго 5 регистра адреса. Вход регистра 5 соединен с выхо дом счетчика 7 адресов .-Выход регист ра 9 чисЛа и первый выход регистра 10 числа подключены к одним из выхо дов элементов ИЛИ 13, выход которы подключен к входу накопителя 1.Вторые вход и выход регистра 10 числ соединены соответственно с выходом блока 19 местного управления и первым, входом блока 14 контроля, второй вход которого подключен к выходу третьехо регистра 11 числа.Друго Вход четвертого регистра 12 числа подключен к выходу первого коммутатора 15, а выходы регистра 12 - к другим входам элементов ИЛИ 13 и первому входу второго коммутатора 16, выход которого соединен с вторым входом первого регистра числа 9, выход которого соединен с первым входом первого коммутатора 15.Вторые и третьи входы первого 15 и второго 16 коммутаторов соединены соответственно с первыми входами блока 14 контроля и счетчика 17 разрядов. Второй выход блока 14 контроля подключен ко входу счетчика 17 разрядов, второй выход которого соединен со входом блока 18 управления. Один из выходов блока 18 управления подключен к управляющим входам накопителя 1, первого 4 и второго 5 регистров-адреса,счетчика / адресов первого 9, второго 10, третьего 11 и-четвертого 12 регистров числа,блока 14 контроля и блока 19 местного управления, другие выходы, блока 18 управления соединены с управляквдими входами коммутаторов 15 и 16. Входы формиро.вателя 22 подключены к выходам первого 9, второго 10 и четвертого 12 регистров числа, а выход - ко входам второй Т-руппы элементов ИЛИ 13 и входу дешифратора 23. Выход дешифратора 23 соединен со входами блока 14 контроля и сумматора 24. Другой вход сумматора 24 подключен к выходу второго регистра 10 числа, а выход - ко входам первого 9 и четвертого 12 регистров числа. Устройство работает следующим образом. В исходном состоянии счетчик 17 разрядов обнулен. Для каждого линейного участка программы или для массива чисел,которые будут записываться и считываться последовательно, выделяются резервные ячейки накопителя 1 . В счетчик 7 адресов при этом записывается адрес первой резервной ячейки, а на вход 6 регистра сщреса 4 поступает адрес ячейки записываемого или считываемого массива чисел . При записи число через вход 20 поступает в регистр 9,и содержимое регистра 4 адреса через элементы ИЛИ 13 подается на вход ;накопителя 1. Обратный код из регистоа 9 чеоез элементы ИЛИ 13 записываются в ячейку накопителя 1. Затем содержимое ячейки считывается на регистр 11. После этого производится запись-счит.. тывание Прямого кода числа на регистр 10. Причем при записи прямого кода одновременно с информационным разрядами записываются контрольные разряды ,корректирующего кода, которые формируются формирователем 22 и через в.торую группу элементов ИЛИ 13 .поступают в накопитель 1. Сод.1ержимое регистров 10 и 11 подается на блок 14 контроля. В случае, если отказав ших разрядов в ячейке нет, то в регистр 4 на вход 6 подается следующи адрес и аналогично производится запись второго числа. Если же в ячейк есть отказавшие разряды, то блок 14 контроля и счетчик 17 разрядов выда|от на .коммутатор,J5 сигналы, по,кото рым из регистра 9 в младгиие разряды регистра 12 передаются разряды числ соответствующие отказавшим разрядам ячейки. Затем в блок 14 контроля, в счетчик разрядов 17 записывается код, соответствующий количеству отказавших разрядов ячейки.Из блока 1 управления в блок 19 местного управления поступает сигнал, по которому в маркерный разряд ячейки накопителя через регистр Ю записывается код . Одноврем(энно из регистра 10 поступает число в формирователь 22 и полученные контрольные разряды корректирующего кода записываются на место ранее записанных контрольных разрядов. При этом искаженные разряды используются как истинные. Аналогично производится запись числа во вторую отказавшую ячейку,только соответствугацие разряды регистра 9 записываются в следукхцие младшие незанятые разряды регистра 12. После того, как все разряды регистра 12 будут заполнены счетчик разрядов выдает сигнал заполнения в блок18 управления. Адрес резервной ячейки из счетчика 7 поступает на регистр 5 адреса и через элементы ИЛИ 3 на вхо 2 накопления. Содержимое регистра 12 через элемент ИЛИ 13 записывается в первую резервную ячейку массива чи сел .Одновременно в эту же ячейку записываются контрольные разряды корректирукщего кода (из формирователя 22). После этого по сигналу из блока 18 управления в счетчике 7 адреса формируется адрес следукицей резервной ячейки. Чтение информации производится следующим образом. В регистр 4 адреса через вход б подается адрес первой ячейки считываемого массива чисел, а в счетчик 7 адреса записывается адрес первой резервной ячейки чисел. Счетчик 17 раз рядов при этом находится в нулевом состоянии. По сигналу из блока 18 управления производится передача соу i JfjaOJt nrt П 11 х г лл. -t, держимого счетчика 7 адреса через ре mcfp 5 адреса и элементы ИЛИ 3 на вход 2 накопителя 1. Производится чтение числа ,из первой резервной яче ки на регистр 10. Из регистраЮ чис ла поступает в формирователь 22,где проверяется выполнение контрольных соотношений корректирукяцего кода и при ошибке вырабатывается нулевой синдром. Синдром поступает на дешифратор 23, который управляет работой сумматора 24.Скорректированное число. поступает в регистр 1. Затем из регистра 4 адреса поступает адрес первой ячейки считываемого массива чисел и производится чтение на регистр 10. Если в маркерном разряде код О, то следовательно, до записи числа в ячейке не было отказавших разрядов. Число из регистра 10 поступает в формирователь 22 к с помощью дешифратора 23 и сумматора 24 корректируется разряд числа, который мог отказать после записи числа в ячейку. После этого число записывается в регистр 9, а затем поступает на выход 21. Наличие кода i в маркерном разряде означает, что до записи числа в ячейке были отказавшие разряды. В случае, если после записи массива чисел не было отказов или появился отказ, значение которого не совпадает со значением соответствующего разряда хранимой кодовой комбинации, то производится следующее. Как и в рассмотренном случае корректируется разряд,который мог отказать после записи числа в ячейку и число записывается в регистр 9.Затем производится запись-чтение обратного кода числа на регистр 11. Содержимое регистров 10 и 11, а также сигнал с дешифратора 23 о номере разряда, отказавшего после записи числа, подаются на блок 14 контроля.По сигналам из блока 14 контроля и счетчика 17 разрядов через второй коммутатор 16 производится передача необходимого числа младших разрядов регистра 12 в регистр 9. Причем в разряд, который отказал после записи числа и который исправлен корректирующим кодом не передается информация с регистра 12. Таким образом, разрядами резервной ячейки подменяются только те разряды ячейки, которые отказали до записи числа. Число из регистра 9 Поступает на выход 21. В счетчик 17 разрядов записывается код, соответствукиций количеству использованных разрядов регистра 12. Если все разряды регистра 12 будут использованы, на что указывает соответствующее состояние счетчика разрядов 17, то по сигналу из блока управления в счетчике 7 адреса формируется адрес слеующей резервной ячейки. Содержимое рез ервной ячейки считывается на ,- -----.--- ..... - - гистр 10, корректируется и передаетя на регистр 12. Далее аналогично продолжается считывание массива чи-i сел. Если в маркерном разряде содержитя код и после записи массива исел появится отказ, значение котоого совпадает со значением соответтвующего разряда хранимой кодовой омбинации, то работоспособность ус

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1152044A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО^ei^- | 1972 |

|

SU332498A1 |

Авторы

Даты

1982-03-07—Публикация

1980-03-11—Подача