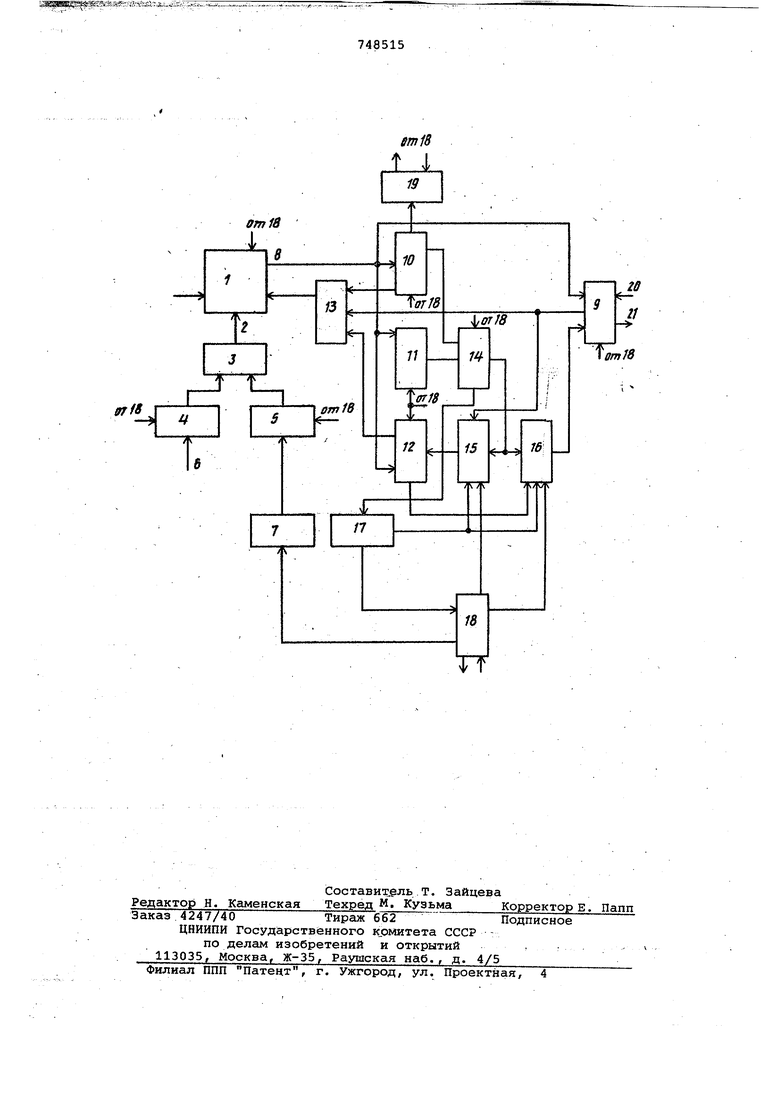

(54) ЗАПОШНАОДЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ Изобретение относится к облас.ти запоминающих устройств. Известны запоминающие устройства с самоконтролем. Одно из известных устройств содер жит адресный и ассоциативные запоминающие блоки 1 . Недостатком этого устройства является применение ассоциативных isano минающих блоков для записи данных при отказах ячеек адресного запоминающего блока, 4to усложняет устройство.- Из известных устройств наиболее близким техническим решением к данному изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, регистры чисЛа группы элементов ИЛИ, регистры адреса, счетчик адресов, блок контроля, блок управления и блок местного управления, причем выход накопителя подключен к первым входам первого .регистра числа и второго регистра числа и ко входу третьего регистра числа, входы накопителя соединены с выходами элементов ИЛИ, входы элементов ИЛИ первой группы подключены к выходам первого регистра адреса и второго регистра адреса, вход которого соединен с выходом счетчика .адресов, первый выход второго регистра числа и выход первого регистра числа подключены к одним из входов второй группы элементов ИЛИ, торые вход и выход второго регистра, числа соединены соответственно с выходом блока местного управления и первым входом блока контроля, второй вход которого соединен с выходом третьего регистра числа, один из выходов блока управления подключен к управляющим входам накопителя, первого и второго регистра адреса, счетчика адресов первого, второго и третьего регистров числа, блока контроля и блока местного управления И В этом устройс.тве в работоспособ ные разряды отказавшей ячейки накопителя записывается адрес резервной ячейки. Недостатком этого устройства является неполное использование работоспособных разрядов в отказавшей ячейке, при записи в нее адреса резервной ячейки, что приводит к снижению эффективной емкости I устройства. Целью изобретения является увели чение эффективной емкости запоминающего устройства. Поставленная цель достигается тем что устройство содержит четвёртый ре гистр числа, коммутаторы и счетчик эазрядов, причем входы, четвертого pts Ьистра числа подключены соответствен но к выходам накопителя и первого ко мутатора, а выходы - к другим входа второй группы элементов ИЛИ и первому входу второго коммутатора, выход которого соединен Ьо вторым входом первого регистра числа, выход ко торого подключен к первому входу пер вого коммутатора, вторые и третьи входы nepiBoro и второго коммутаторов соединен соответственно с первыми взаходами блока контроля и ; ра;зря:йов, вторые выходы которых -подключены соответственно ко входам сче , чика разрядов и блока управления, уп равляющие входы четвертого регистра числа коммутаторов соединены -с дру-., гими выходами блойаупрайлёйШ. На чертеже изображена блок-схема предложенного устройстза,,;..- ,-,.--... Устройство содержит накопитель 1, имеющий входы 2, перйую rpynfiy эле-. ментов ИЛИ 3/ первый регистр адреса 4, второй регистр адреса 5, входы б первого-регистра адреса, счетчик адресов 7. К выходам 8 нйкОпителяподключ:ены первые входы пёрвого pefHCTisS чйслй 9, второго регйстра числа 10, вход третьего регистра 1Г и один из входов четвертого 12 регистра числа. ....; . -г ;- -/ --:--у Устройство содержит также вторую группу элементов ИЛИ 13,. блок .конт-, роля 14, первый 15 и второй 1б ком-,. мутаторы, счетчик разрядов 17, блок, управления 18 и блок местного управ /ленйяСэ, вход 20 и выход 21 устройства.. Входы2 накопителя 1 соединены С вы1ходамй элёмелтой ЙЙИ 3, йхбда йо торых подключенй к вваходам первого 4 и второго. 5 регистров адреса. Вход регистра 5 соединен ;с йаходбм ечётчика адресов 7. Выход регистра 9 и первый выход регистра числа 10 подйлйчены кОдним из выходов элементов ИЛИ 13, йЁйсбдйбЧ Ъ й Шд ключен к входу накопителя-1. Вторые вход и выход регистра числа 10 соединены соотв,етственно с вшсодом: блока местного управления 19:И rtep-; ним входом блока контроля 14, второй вход которого подключен к выходу третьего регистра числа 11. Другой вход четвёртого регистра числа 12 подключен к выходу первого коьфлута.тора 15, а выходы регистра 12 - k Другим входам элемейтов ИЛИ 13 и rtep ному вхоДу второго коммутатора 16, выход которого соединен со вторым входом первого регистра числа 9, выход которого соединен с пёрвым о дом Первого кс Шутатора 15. Втор .и третьи входы первого 15 и второго 1/ лсоммутаторов соединены соответст/48515венно с первьми выходами блока контроля 14 и счетчика разрядов 17. BTOf рой выход блока контроля 14 подключен ко входу счетчика разрядов 17,второй выход которого соединен соВХОДОМ блока управления 18.Один из выходов блока управления 18 подключен к управляющим входам накопителя 1, первого 4 и второго 5 регистров адреса, счетчика адресов 7, первого 9, второго 10, третьего. 11 и четвертого 12 регистров числа, блока контроля 14 и Яблока местного управления 19, другие выходы блока управления 18 соединены управляющими входами коммутаторов 15 и. 16. : .. ... ... .. Устройство работает следующим образом. -. . . в исходном состоянии-счетчик раз-рядов 17 обнулен. Для калсдого линейного участка программы -или для чисел, которые .будут записывать- . ся и считыватьсяпоследовательно, выделяются резервные ячейки накопителя 1, в счетчик адресов 7 при этом. йаписываетЬя адрес первой резервной ячейки, а на вход б основного регистра адреса 4 поступает адрес первой . .... ячейки записываемого или считываемого массива гисел. .: . При записи число через вход 20 поступает в регистр 9, и содержимое , регистра адреса 4 через элементы ИЛИ 3 подаётся на вход, накопителя 1. Обратный код из. регистра 9 через эле.менты ИЛИ 13 записывается в ячейку на:кОпйтёля 1 /Затем соДержиМ(эе. .ячейки считывается на регистр 11. После это;го производится запись-считывание прямого кбда числа на регистр- 10. Содержимое регистров Ю и 11 пОдается на блок контроля 14. Вслучае, ес.лиотказав1ййхразрядов в ячейке нет, то в регистр 4 на вход б подается следующий адрес- и а.налОгично производится запись второго чис.ла. Если же в ячейке есть отказавшие разряды, то бЛОкконтроля 14 и счетчик разрядов 17 выдают на коммутатор сигналы, ;по .которым из регист 1а 9 в младшие разряды регистра 12 передаются разряду числа, соответствующие отказавшим раз:рядам ячейки, Затем с.,блока контро- . ля .14 в с.четчик разрядов 17 записывается код, соответствующий количеству отказавших разрядов ячейки. Из блока управления 18 в блок местного управления i9 Ъоступает сигнал, йо которому в маркерный разряд ячейки накопителя через регистр 10 записывается код 1. Аналогично производится запись числа во вторую отказавШУЮ ячейку, только соответствующие разряды регистра 9 записываются в.,следующие младшие незанятые разряды регистра 12. После того, как все разряды регистра 12 будут заполнены, бчётчик разрядов выдает сигнал зaпoл

нения в блок управления 18. Адрес резервной ячейки из счетчика адреса 7 поступает на регистр адреса 5 и через элементы ИЛИ 3 на вход 2 накопителя 1. Содержимое регистра 12 элементы ИЛИ 13 записывается в первую резервную ячейку массива, чисел. После этого по сигналу из блока управления 18 в счетчике адреса 7 формируется адрес следующей резервной ячейки.

Чтение информации производится еледуЩим образом. В. регистр адреса 4 через вход б подается адрес первой ячейки считываемого массива чисел, а в счетчик адреса 7 записывается адрес первой резервной ячейки массива чисел. Счетчик разрядов 17 при этом находится в нулевом состоянии. По сигналу из блока управления 18 производится передача содержимого счетчика адреса 7 через регистр адреса 5 и элементы ИЛИ 3 на вход 2 накопителя 1. Производится чтение числа из первой резервной ячейки на регистр 12. Затем из регистра адреса б поступает адрес первой ячейки считываемого массива чисел и производится чтение на регистры 9 и 10. Ecли в маркерном разряде код О, то, следовательно, в ячейке не было отказавших разрядов и число из регистра 9 поступает на выход 21.

Если же в маркерном разряде код 1, то производится запись-чтение обратного кода числа на регистр 11. Содержимое регистров 10 и 11 подается на блок ко,нтроля 14. По сигналам из блока контроля 14 исчетчика разрядов 17 через второй коммутатор 16 производится передача младших разрядов регистра 12 в регистр 9. Разряды отказавшей ячейки, таким образом, подменяются разрядами резервной ячейки, Число из регистра 9 поступает на выход 21., В счетчик разрядов 17 записывается код, соответствующий количест- ву использованных разрядов регистра 12. Если все разряды регистра 12 будут использованы, на что указывает соответствующее состояние счетчика разрядов 17, то по сигналу из блока управления в сче±чике адреса; 7 формируется а,црес следующей резервной ячейки. Содержимое резервной ячейки с итывается на регистр 12 и аналогично продолжается считывание массива чи сел с подменой отказавших разрядов.

Технико-эко юмические преимущестйа изобретения заключаются: в значительном сокращении количестварезервных ячеек в накопителе при последовательном выборе адресов. Например, если разрядность накопителя равна 32, а в выбранном для записи массиве чисел участка памяти отказали по 2 разряда в 16 ячейках, то в известном устройстве потребуется 16 резервных ячеек , в предоженном - всего лишь одн

748515

ячейка, за счет чего значительно увеличивается эффективная емкость предложенного запоминающего устройства.

Формула изобретения

Запоминающее устройство с самоконтролем, содержагцее накопитель, регистры числа, группы элементов ИЛИ, регистры адреса, счетчик адресов, Ьлок контроля, блок управления и бдо kecTHoro управления, причем выход накопителя подключен к перовым входам hepBoro и второго регистров числа

и ко входу третьего регистра числа, входы накопителя соединены с выходами элементов ИЛИ, входы элементов ИЛИ первой группы подключены к вы,ходам первого регистра адреса и второго регистра адреса, вход которого соединен с выходом счетчика адресов, первый выход второго регистра числа и выход первого регистра числа подключены к одним из входов второй групы элементов ИЛИ, вторые вход и выход второго регистра числа соединены соответственно с выходом блока местного управления и первым входом блока контроля, второй вход которого соединен с выходом третьего регистра числа, одни иэ выходов блока уггравпеЬия подключены к управляющим входам накопителя, первого и второго регистров адреса, счетчика адресов, пе;ВОго, второго- и третьего регистров числа, блока, контроля и блока местного управления, отличающееся тем, что, с целью увеличения эффективной емкости устройства, оно содержит четвертый регистр числа, коммутаторы и счетчик разрядов, причем входы четвертого регистра числа подключены соответственно к выходам накопителя и первого коммутатора, а выходы - к другим входам элементов ИЛИ второй группы и.первому входу второго коммутатора, выход которого соединен со вторым входом первого регистра числа, выход подключен к первому входу первого коммутатора, вторые и третьи входы первого и второго коммутатора соединены соответственно с первьши выходами блока контроля и сче.тчика разрядов, вторые выходы которых подключены соответственно ко входам счетчика разрядов и блока управления, управляющие входы четвертого.регистра числа и коммутаторов соединены с другими выходами блока упра зления.

Источники информации, приня:тые во внимание при экспертизе

1.Авторское свидетельство СССР № 529490, кл. G 11 С 29/00, 1976.

2.Авторское свидетельство СССР ;№ 519767, кл. G 11 С 29/00, 1976

(прототип).

ffTiS

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1152044A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Устройство для контроля памяти | 1979 |

|

SU809395A1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

Авторы

Даты

1980-07-15—Публикация

1978-06-08—Подача